AMAZINGIC晶焱科技考虑寄生电容的高速接口中的TVS选择以及方案应用由授权一级代理分销KOYUELEC光与电子0755-82574660,82542001为ODM研发设计工程师提供技术选型和方案应用支持。

摘要:

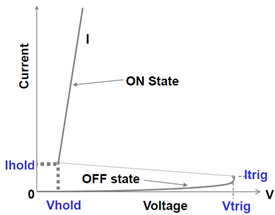

TVS的选择与其保护的应用接口息息相关,除了TVS的操作电压必须大于或等于保护线的操作电压之外,若是应用在高速的传输接口保护上,TVS的寄生电容值也必须加入考虑,否则可能会影响讯号完整性(Signal Integrity),造成讯号传输波形的失真,无法判读。但相反的,也有少数系统设计工程师因过度追求讯号完整度,而在讯号线要求过低电容值的TVS,造成可选择的防护组件方案钳位电压 (clamping voltage) 过高,如此可能严重影响TVS防护系统的效果,不符合防护设计方案的初衷。

本文将针对高速接口的传输速度说明TVS的选择方案,并且透过反射损耗来估计高速讯号的最大容许电容值,避免设计工程师挑选过小或过大电容值的防护方案。

寄生电容对于高速讯号的失真影响

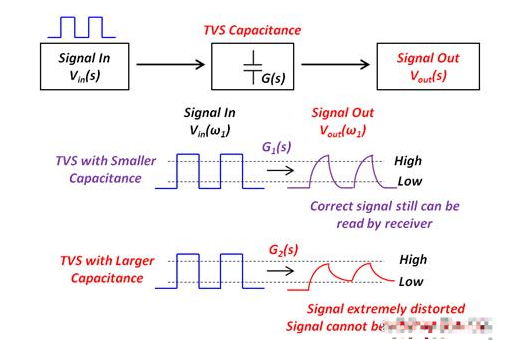

如下图一表示,讯号在线对地电容的大小会造成讯号的上升与下降时间变慢,进而造成讯号的波形失真,对地电容越大则会使上升与下降时间越慢,如下式一、二。当讯号的失真程度大过IC可以辨别的阀值情况,则有误码的情况产生。因此在高寄生电容的情况下,要解决误码情况则需要增长Bit Time使得讯号有足够时间上升或下降至判断阀值区,进而造成讯号传输速度变慢。

For Rising State: V(t)=V_0 (1-e^(-t/RC)) 式一

For Falling State: V(t)=V_0 (e^(-t/RC)) 式二

Fig. 1 电容对于讯号的失真影响

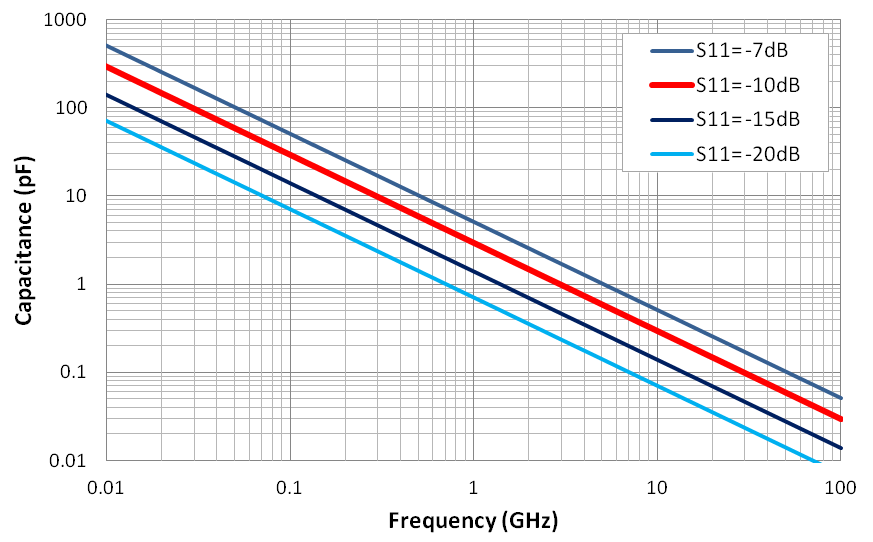

然而从时域的波形中较难量化电容值的大小将造成多严重的讯号失真,因此在高速数字讯号或射频线路的设计中,会透过FFT (Fast Fourier Transform) 将时域转换为频域来做表示,即S参数(S-Parameter),如: S11 Return Loss(反射损失)与S21 Insertion Loss(插入损失)。

高频讯号衰减与电容考虑

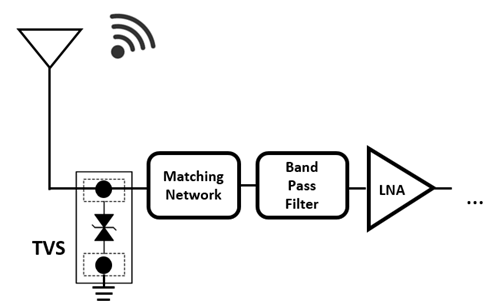

S11 Return Loss (反射损失) 描述当传输线两端阻抗不匹配时,电磁波在两接口间产生反射,而反射波与入射波功率的功率比值即Return Loss。TVS在电路上的应用需与终端阻抗并联到地,故会增加电容性负载,使得阻抗发生变化。

首先,假设单端传输线特征阻抗为50 Ohm且为理想正弦波,普遍射频工程上以S11小于 -10dB来判别是否阻抗匹配,当S11小于 -10dB时,代表入射功率可以传送超过90%至负载端。接着计算不同操作频率下的等效电容值,我们就可以得到图二中的红色线,藉此来判断不同速度的高速接口,其TVS的寄生电容值选择上限。

Fig. 2 不同反射损耗条件下要求的电容负载容许度

以USB4为例,其单一条Tx/Rx的最高传输速度可达20 Gbps,操作频率可等效为10 GHz的基频,因此从图二中可以观察到,一条高速在线在S11= -10 dB的情况下,最大可容许约0.29 pF的寄生电容。此外,亦可采用类似的方法针对S21 Insertion Loss (插入损失) 进行 TVS 的电容评估,不论采用 S11 或 S21 的评估结果是相等的,因为对于对地电容造成的反射波功率即插入的功率损耗 (S21)。然而不同的传输接口,讯号衰减忍受程度都不同,各个系统设计时可以留给 TVS 的余量也不同,最后我们可以从各传输接口的眼图条件(讯号衰减程度)来判别TVS应该容许的寄生电容大小。

晶焱科技的高速接口ESD解决方案

晶焱科技拥有业界规格最高也最完整的高速接口ESD解决方案,USB、HDMI、LAN Port对应的解决方案应有尽有,可参考下表一。AZ5B9S-01F仅有0.18pF的寄生电容,在相同DFN0603的封装大小,提供业界最低的4.6V钳制电压,是保护USB4 Re-timer/Controller的最佳选择。晶焱在市场多年的耕耘,与客户的密切合作令晶焱的产品与市场完美接轨,帮助客户解决ESD的同时,更保证了高速接口的讯号质量。

|

Interface |

Amazing Solution |

Capacitance (Typ.) |

Clamping Voltage at ESD 8kV |

|

USB2.0 (D+/D-) |

AZC399-04S |

1.4 pF |

9V |

|

USB3.0 (Tx/Rx) |

AZ1143-04F |

0.45 pF |

9V |

|

USB3.2 (Tx/Rx) |

AZ176S-04F |

0.29 pF |

4.3V |

|

USB4 (Tx/Rx) |

AZ5B9S-01F |

0.18 pF |

4.6V |

|

HDMI1.4 (TMDS) |

AZ1143-04F |

0.45 pF |

9V |

|

HDMI2.0 (TMDS) |

AZ1143-04F |

0.45 pF |

9V |

|

HDMI2.1 (TMDS/FRL) |

AZ1123-04F |

0.2 pF |

10V |

|

Display Port 1.4 |

AZ1143-04F |

0.45 pF |

9V |

|

Display Port 2.0 |

AZ1123-04F |

0.2 pF |

10V |

|

LAN 100M/1000M/2.5G |

AZ1513-04S AZ3133-08F |

2.0 pF 1.7 pF |

7.5V 12.5V |

|

LAN 5G/10G |

AZ1123-04F AZ5B0S-01F |

0.2 pF 0.18 pF |

10V 5.5V |

|

PCIE Gen4/Gen5 |

AZ5B9S-01F |

0.18 pF |

4.6V |

Table 1. 晶焱科技提供的ESD解决方案

审核编辑:汤梓红

-

接口

+关注

关注

33文章

8597浏览量

151150 -

TVS

+关注

关注

8文章

786浏览量

60613 -

寄生电容

+关注

关注

1文章

292浏览量

19234

发布评论请先 登录

相关推荐

半大马士革工艺:利用空气隙减少寄生电容

高速ADC与FPGA的LVDS数据接口中避免时序误差的设计考虑

深入解析晶振时钟信号干扰源:寄生电容、杂散电容与分布电容

仿真的时候在哪些地方添加寄生电容呢?

在LF411CD的放大模块出现输出会发生振荡,请问该元件输入端(2端)与GND间的寄生电容多大?

普通探头和差分探头寄生电容对测试波形的影响

igbt功率管寄生电容怎么测量大小

PCB寄生电容的影响 PCB寄生电容计算 PCB寄生电容怎么消除

AMAZINGIC晶焱科技考虑寄生电容的高速接口中的TVS选择以及方案应用

AMAZINGIC晶焱科技考虑寄生电容的高速接口中的TVS选择以及方案应用

评论