来源:泛林集团

Coronus® DX 建立在泛林集团 15 年来在晶圆边缘解决方案的创新之上

近日,泛林集团 (Nasdaq: LRCX) 推出了Coronus DX产品,这是业界首个晶圆边缘沉积解决方案,旨在更好地应对下一代逻辑、3D NAND和先进封装应用中的关键制造挑战。随着半导体芯片关键尺寸的不断缩小,其制造变得越来越复杂,在硅晶圆上构建纳米级器件需要数百个工艺步骤。仅需一个工艺步骤,Coronus DX 可在晶圆边缘的两侧沉积一层专有的保护膜,有助于防止在先进半导体制造过程中经常发生的缺陷和损坏。这一强大的保护技术提高了良率,并使芯片制造商能够实施新的前沿工艺来生产下一代芯片。Coronus DX 是Coronus® 产品系列的最新成员,扩大了泛林集团在晶圆边缘技术领域的领先地位。

泛林集团全球产品事业部高级副总裁 Sesha Varadarajan 表示:“在 3D 芯片制造时代,生产复杂且成本高昂。基于泛林集团在晶圆边缘创新方面的专长,Coronus DX 有助于实现更可预测的制造并大幅提高良率,为以前不可行的先进逻辑、封装和 3D NAND生产工艺得以采用铺平道路。”

沉积在工艺集成过程中增加了关键保护

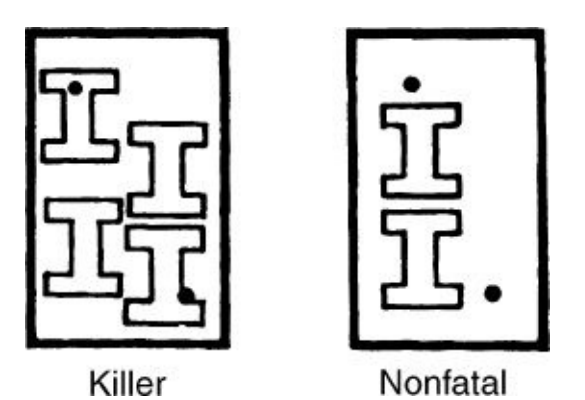

与 Coronus 晶圆边缘刻蚀技术互补,Coronus DX 使新的器件架构成为现实,这对于芯片制造商来说是颠覆性的。重复叠加的薄膜层会导致残留物和粗糙度沿着晶圆边缘积聚,并且它们可能会剥落、漂移到其它区域并产生导致器件失效的缺陷。比如:

· 在 3D 封装应用中,来自生产线后端的材料可能会迁移,并在之后的工艺中成为污染源。晶圆的塌边会影响晶圆键合的质量。

· 3D NAND 制造中的长时间湿法刻蚀工艺可能会导致边缘处衬底的严重损坏。

当这些缺陷不能被刻蚀掉时,Coronus DX 会在晶圆边缘沉积一层薄的电介质保护层。这种精确和可调整的沉积有助于解决这些可能影响半导体质量的常见问题。

CEA-Leti 半导体平台部门负责人 Anne Roule 表示:“CEA-Leti 运用其在创新、可持续技术解决方案方面的专业知识,帮助泛林集团应对先进半导体制造方面的关键挑战。通过简化 3D 集成,Coronus DX大幅提高良率,使芯片制造商能够采用突破性的生产工艺。”

专有工艺推动良率提升

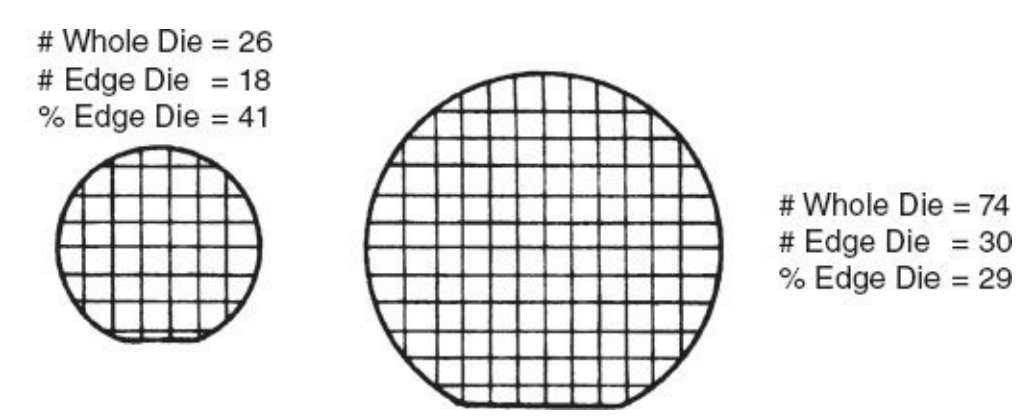

Coronus DX 采用了一流的精确晶圆中心定位和工艺控制,包括内置量测模块,以确保工艺的一致性和可重复性。Coronus 产品逐步提高了晶圆良率,每个刻蚀或沉积步骤提高 0.2% 至 0.5% 的良率,这可以使整个晶圆生产流程的良率提高 5%。每月加工超过 100,000 片晶圆的制造商在一年中可通过 Coronus 提高芯片产量达数百万 ——价值数百万美元。

各大芯片制造商都使用了 Coronus

Coronus 产品系列于 2007年首次推出,被各大半导体制造商使用,在全球范围内安装了数千个腔体。泛林集团的 Coronus 产品系列是业界首个经过大规模生产验证的晶圆边缘技术。其 Coronus 和 Coronus HP 解决方案是刻蚀产品,旨在通过去除边缘层来防止缺陷。Coronus 解决方案被用于制造逻辑、内存和特色工艺器件,包括领先的 3D 器件。Coronus DX 目前已在全球领先的客户晶圆厂中用于大批量制造。

Kioxia Corporation 内存工艺技术执行官 Hideshi Miyajima博士表示:“通过晶圆边缘技术等领域的进步提高生产工艺的质量,对于我们向客户大规模提供下一代闪存产品至关重要。我们期待继续与泛林集团及其 Coronus 解决方案合作,以实现领先的晶圆生产。”

媒体资源

· 访问泛林集团新闻中心以获取相关图片,或者了解有关泛林集团与 CEA-Leti 进行的晶圆边缘沉积研究的更多信息。

关于泛林集团

泛林集团 (NASDAQ: LRCX) 是全球半导体创新晶圆制造设备和服务的领先供应商。泛林集团的设备和服务助力客户构建更小、性能更出色的器件。 事实上,当今几乎每一块先进芯片的制造都使用了泛林集团的技术。 我们出色的系统工程、技术领先力、以及基于强大的价值观的企业文化,都与对客户的坚定承诺紧密结合。 泛林集团是一家 FORTUNE 500®(美国《财富》500 强)公司,总部位于美国加利福尼亚州弗里蒙特,业务遍及世界各地。 若需了解更多详情,请访问 www.lamresearch.com。

审核编辑:汤梓红

-

芯片

+关注

关注

455文章

50714浏览量

423139 -

晶圆

+关注

关注

52文章

4890浏览量

127931 -

泛林集团

+关注

关注

0文章

58浏览量

11801

发布评论请先 登录

相关推荐

晶圆划片为什么用UV胶带

泛林集团推出全球首个晶圆边缘沉积解决方案以提高芯片良率

泛林集团推出全球首个晶圆边缘沉积解决方案以提高芯片良率

评论