semiengineering.com; JUNE 15TH,2023

High-Density Fan-Out Packaging With Fine Pitch Embedded Trace RDL

高密度扇出封装与细间距嵌入式线路RDL;具有有机介电层的双大马士革工艺(Dual Damascene, DM)铜制程克服了细线路定义的挑战。

在新冠疫情期间,人工智能(AI)、高性能计算(HPC)和数据中心应用对高性能设备的需求大幅增加。与此同时,集成电路(IC)行业努力将硅技术节点最小化,以满足在紧密成本约束下对计算性能的无休止要求。目前,使用纳米片技术引入了2纳米节点技术。该设计在相同功耗下提供了45%的速度提升,与7纳米节点相比。然而,随着节点尺寸的减小和晶圆产出显著降低,设计成本和开发时间大幅增加,因为微小的缺陷可能会导致单个芯片的整体功能受损。芯片组技术是克服这些限制、以合理和可承受的价格为消费者提供最先进产品的最有效解决方案之一。

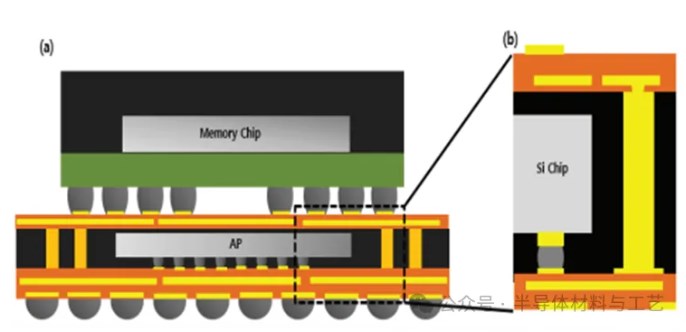

芯片组将先进节点大小的核心模块与小型芯片分开,以提高晶圆产出并重复使用先前节点模块的知识产权(IP),以降低设计成本。为了互连这些具有不同节点大小和不同材料的异构块芯片,需要采用先进的集成电路封装技术。以往,多芯片模块(MCM)翻转芯片球栅阵列(FCBGA)一直被传统采用作为层压基板上多芯片的异构接口。然而,由于基板的电路径显著长,它不适用于先进节点IC。采用2.5D硅穿孔(TSV)技术的模块接口作为高性能封装的新候选方案被引入,其具有极短的电路径,但由于硅间质的限制,在高频(4-6 GHz)应用中性能有限[1]。因此,最近出现了一种高密度扇出(HDFO)接口,它去除了硅(Si)和无机介质,并采用有机介质。特别是Amkor Technology的HDFO被称为基于硅片的扇出技术(S-SWIFT)封装,为异构集成提供了更高带宽的芯片间互连。

先前的研究已经证明了它的出色性能[1, 2]。为了展示S-SWIFT方法,需要解决许多关键的设计方面,包括:微细间距μ-凸点接口、在热组装过程中准确控制组件的翘曲、毛细管封装、过模封装技术、穿模界面(如Cu高柱)、中端线(MEOL)过程和模侧凸点过程。高密度重分布层(RDL)技术是展示HDFO插接模块可行性的核心技术之一。HDFO中的RDL提供芯片间的接口,需要更高密度的RDL来互连具有较小节点大小的芯片块。半添加工艺(SAP)用于制造HDFO模块的RDL。

然而,SAP在定义细间距特征方面面临一些挑战。细线可能会因为高纵横比而坍塌,由于与基板的接触面积小,可能会出现分层,并且用作模板的光刻胶可能会残留在通孔中[3]。为了克服这些问题,提出了一种使用有机介电层的DM铜制程的方法。在过程中,嵌入在有机介电层中的RDL可以防止种子层下挖问题。通过光刻在味之素叠层膜(ABF)型聚合物层上实现了DM铜制程的RDL [4]。评估了DM铜制程RDL在高频应用中的优势。随后,引入了一种实现DM铜制程RDL中小通孔的特殊制作方法[5]。使用高数值孔径(NA)(0.48)的光刻工具,实现了显著高分辨率的RDL(500纳米)。还研究了使用光刻和干法刻蚀的方法进行DM铜制程RDL的聚苯并噁唑(PBO)制作[6]。讨论了干法刻蚀后的开裂和铜电沉积后的过载问题。

为了克服上述挑战,开发了一种嵌入式线路RDL(ETR)工艺,并验证了ETR的图案性能和可靠性。为了实现ETR,进行了关键的工艺优化和材料修改。同时,还演示了使用ETR将ASIC、高带宽存储器(HBM)和基板相互连接的S-SWIFT封装。这些设计元素成功通过了JEDEC标准的可靠性测试。

嵌入式线路RDL的能力

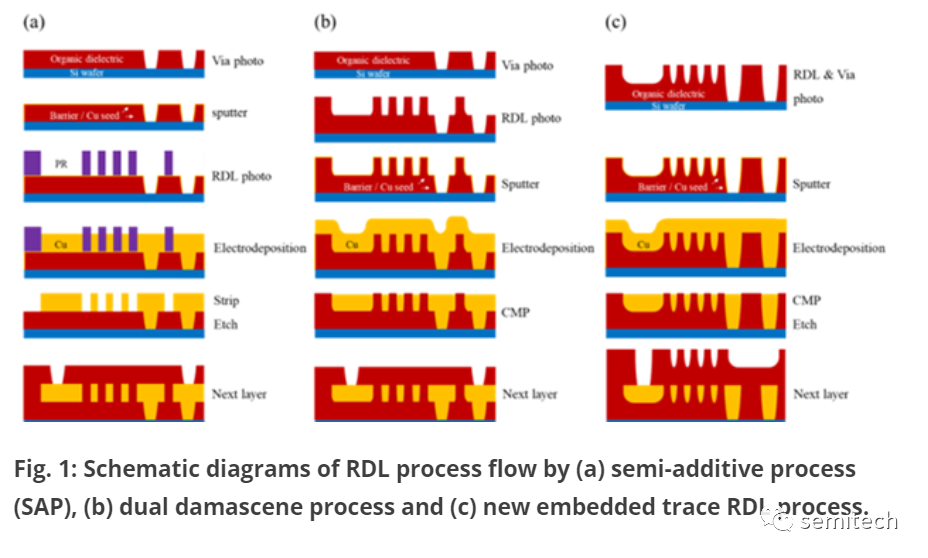

SAP通常用于制造通用封装的RDL,其标准工艺流程如图1(a)所示。首先,在载体晶圆上旋涂液态光可显有机介电层,并通过光刻将通孔图案对准。为了使Cu RDL能够电沉积,通过溅射工艺在后烘烤的介电膜上沉积了屏障和Cu种子层。在种子层上,按照光刻胶(PR)工艺对齐RDL图案,并进行Cu RDL的电沉积。最后,顺序剥离和刻蚀PR模板以及Cu/屏障层。如前所述,由于其方便和可靠的工艺性能,SAP是通用IC封装RDL解决方案的主流技术。然而,通过SAP进行RDL的尺寸缩小存在种子层下挖或侧壁刻蚀等挑战[7]。

通过在介电层中嵌入线路,可以解决这些挑战而无需刻蚀过程。如图1(b)和(c)所示,通过在预形成的钝化层上电沉积Cu,并去除Cu过载,将DM铜嵌入有机介电图案中。这种结构没有Cu坍塌风险,也没有侧壁刻蚀问题,三面面对的屏障金属具有增强的可靠性。此外,DM铜结构在高频信号传递特性方面具有优势,因为即使在高频信号中电流集中在浅层RDL表面时,三面面对的光滑Cu表面受电子散射的影响较小。[4]在图1(b)的顶部显示了在有机介电膜上形成具有RDL和通孔的DM铜结构的工艺流程。通孔和RDL结构是通过两遍光刻工艺分别形成的,其中包括有机介电材料的旋涂、软烘烤、紫外(UV)曝光、显影和热固化过程。

通过采用新颖的光刻技术,简化了先前的工艺流程。如图1(c)的顶部所示,通过对厚涂有机介电膜进行单次紫外(UV)曝光,可以形成通孔和RDL图案。与当前的DM铜方法相比,这种方法减少了40%的RDL工艺步骤,甚至比SAP减少了33%。因此,工艺成本也可以降低。此外,由于通孔和RDL可以通过一次特殊设计的光刻遮罩进行形成,可以避免通孔和捕获垫之间的错位。

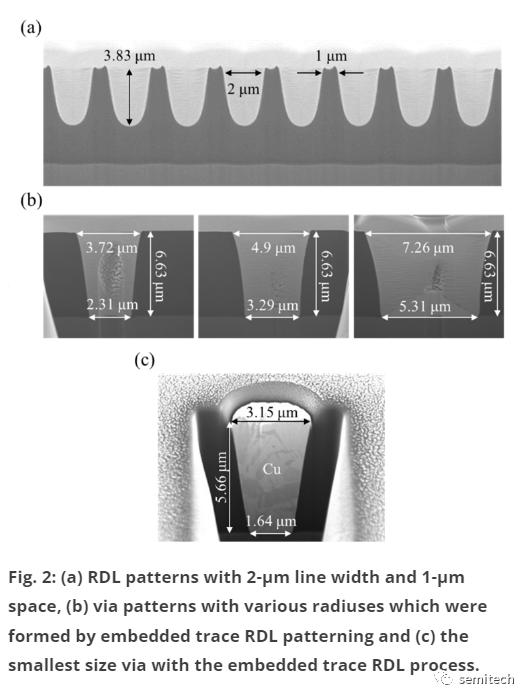

新的ETR工艺的图案能力如图2所示。可以形成具有2/1 μm线/空间的RDL沟槽图案(图2(a))和各种尺寸的通孔图案(图2(b))。如图2(c)所示,ETR的最小通孔分辨率在顶部为3.15 μm,在底部为1.64 μm。这种方法在先进电路设计方面也具有优势。在通孔和RDL层叠加期间,RDL层需要一个用于补充对准工具的布局精度的捕获垫,但ETR工艺则不需要。因此,额外的区域可以用于RDL,从而增加RDL的密度。

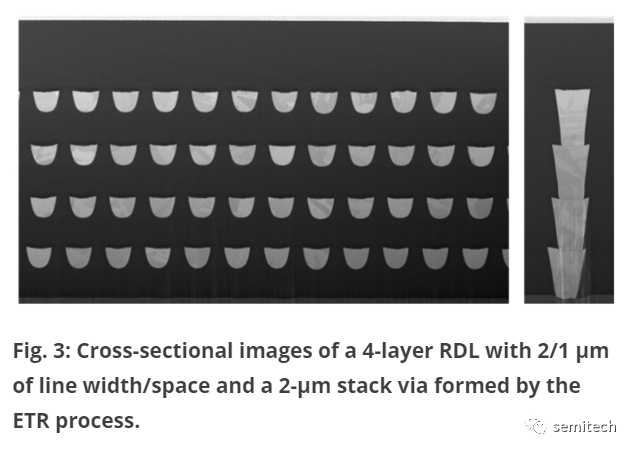

图3展示了ETR工艺的RDL层叠加能力。由于细小的RDL图案形成在介电膜的顶部,并且每个层面都是平坦的,因此ETR工艺可以实现显著稳定的层叠加。使用ETR工艺可以获得具有2/1-μm线/空间和堆叠的无垫通孔,关键尺寸为2 μm的四层RDL。

关键工艺开发

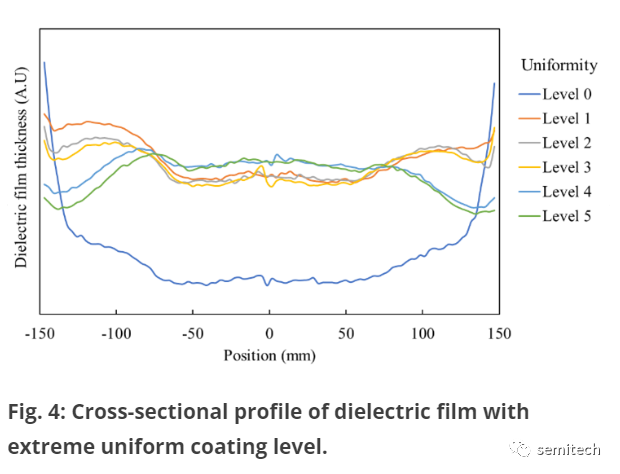

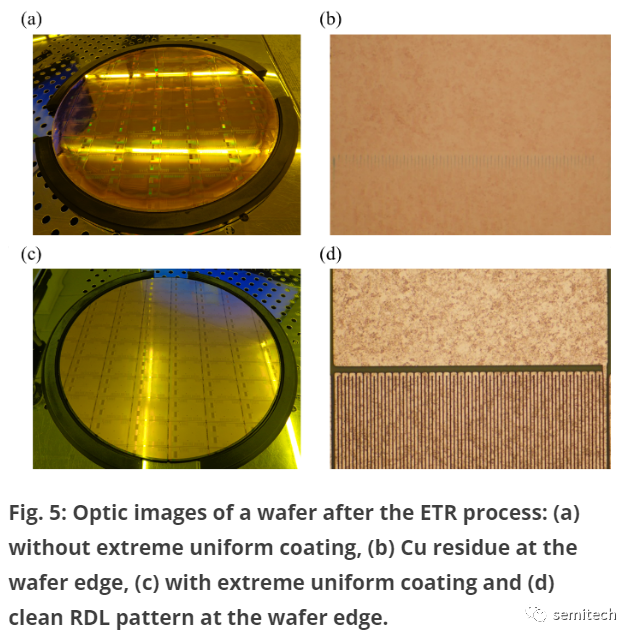

为了实现ETR工艺,需要从旋涂有机介电膜开始对工艺参数进行精细控制。开发了极端均匀涂覆技术,以防止在有机介电膜的非均匀涂覆区域形成的化学机械抛光(CMP)阴影中产生金属残留物。图4显示了随着极端均匀涂覆因子水平的变化,有机介电膜的横截面厚度分布的变化。在均匀度水平为0的情况下,未应用极端均匀涂覆。从晶圆边缘到180毫米处存在0.26 μm的涂覆高度差,导致CMP产生阴影。因此,在DM工艺后,晶圆边缘残留了较厚的Cu残留物,尽管中心区域清晰可见。从图5(a)和(b)的整个晶圆和放大图像中可以看出,晶圆边缘的RDL电路短路。

随着极端均匀涂覆水平的提高,晶圆边缘的CMP阴影减小。随着极端均匀涂覆水平增加到3级,凹型曲率涂覆剖面减小,而采用极端均匀涂覆水平4时,变为凸型涂覆剖面,没有CMP阴影。此外,由于采用极端均匀涂覆,膜厚总差异从未进行极端均匀涂覆的0.47 μm降低到进行极端均匀涂覆水平4的0.12 μm。由于极端均匀涂覆减小了CMP阴影,DM铜工艺后晶圆边缘不会残留Cu残留物。这在图5(c)中显示,并且晶圆边缘的放大图像显示在图5(d)中。因此,通过应用显著改善涂覆均匀性的4级涂覆配方,实现了非常高的良率。

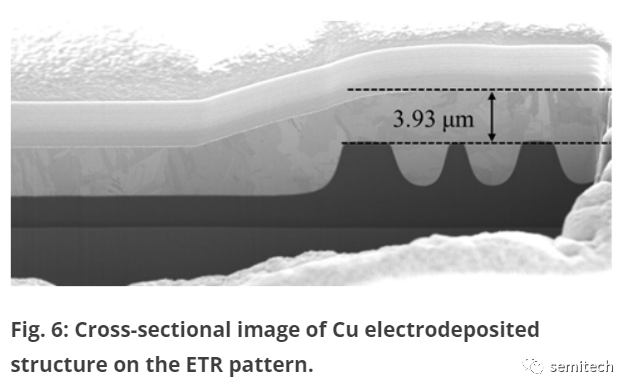

图6显示了具有宽且细的RDL混合图案的Cu电沉积ETR结构的横截面图像。在细小的RDL和小孔图案的狭窄沟槽结构中,可以实现快速的Cu填充,这是因为电镀液中的加速剂集中在Cu生长表面的大曲率区域上,并减小了曲率[8]。最初,这种孔填充原理仅适用于SAP方法中的小孔,但在DM铜工艺中,它也适用于狭窄沟槽结构。然而,在宽RDL的大沟槽中,由于除了沟槽角部分以外没有具有大曲率的区域来集中加速剂物种,因此孔填充不起作用。因此,沟槽底部的电镀速率几乎与顶部表面平行,并且为了填充宽RDL,不可避免地需要在顶部表面形成较厚的过盈层。因此,需要进行大量的Cu CMP。

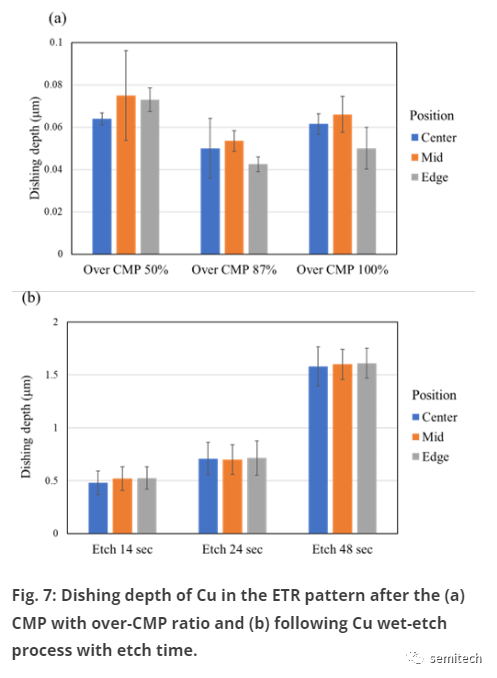

DM铜工艺的Cu CMP过程通常使用3个CMP平台的3个步骤进行:(1)大块Cu去除,(2)Cu抛光和(3)阻挡层和氧化层去除。在ETR工艺中,通过将Cu CMP与单个CMP平台和湿法蚀刻工艺相结合,简化了Cu去除过程。这种方法有利于降低工艺成本和提高工艺速度。首先,使用单个CMP平台进行高速Cu CMP工艺进行大块Cu去除。几乎4μm的Cu过盈层以900 nm/min的去除速率迅速去除。在这种情况下,全晶圆区域的CMP均匀性的精细控制是困难的。因此,不可避免地需要超过CMP来完成整个晶圆表面的大块Cu去除,并且阻止层的作用对于防止与过度CMP相关的问题(如过度凹陷或金属或介电层消失)非常重要。图7(a)显示了晶圆区域的凹陷深度在整个超过CMP比例的情况下都受到均匀控制,且不超过90 nm,因为CMP停止层限制了超过CMP。

Cu残留物在去除CMP和阻挡层之后通过经济高效的湿法蚀刻工艺而不是多步骤的CMP去除。Cu湿法蚀刻工艺清除了Cu残留物。此外,由于刻蚀时间可以均匀控制Cu凹陷,因此还可以实现额外的Cu RDL高度控制,如图7(b)所示。最后,阻挡层也通过标准的湿法蚀刻工艺清除。

S-SWIFT演示

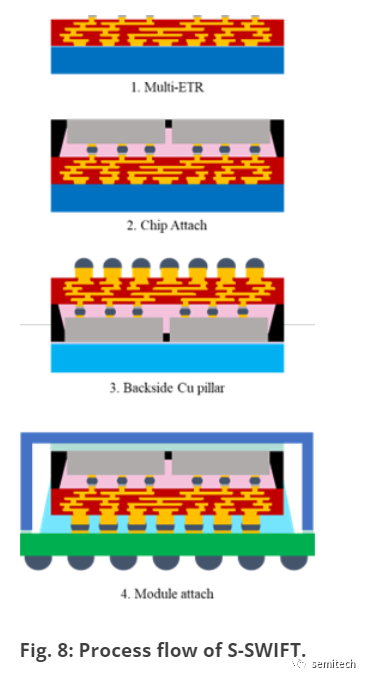

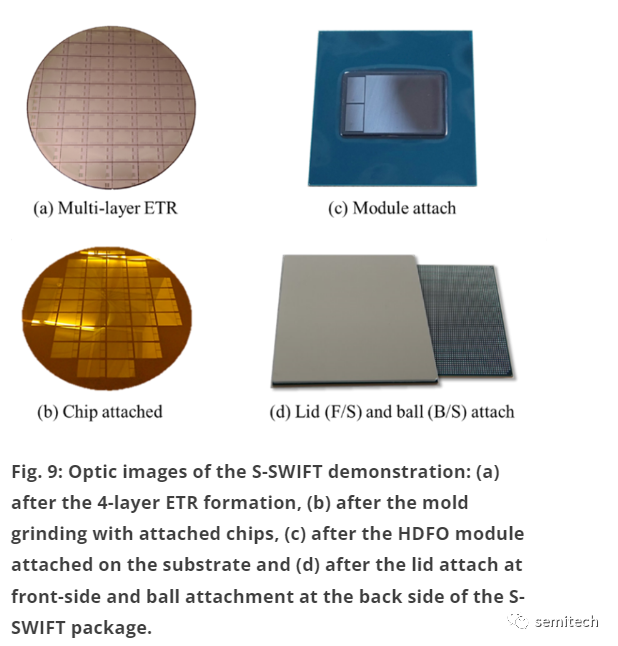

使用如图8所示的标准S-SWIFT组装流程进行了ETR的S-SWIFT演示[1]。四层ETR叠加在硅晶圆上,无铅焊料微球在ETR顶部进行电沉积。将带有ASIC和HBM的多芯片与微球对齐,并通过质量回流工艺连接。接下来,在ETR和多芯片之间进行毛细管填充。随后,使用环氧模具化合物(EMC)对连接的芯片进行模具化处理,然后进行模具研磨以暴露多芯片以接触热界面材料(TIM)。使用紫外可分离胶粘剂在HDFO的前侧上附着第二载体晶圆,并通过晶圆研磨和干法刻蚀工艺组合将背侧晶圆移除,以形成背侧的Cu柱。在Cu柱和无铅焊料电沉积之后,使用紫外激光去除载体晶圆,并进行晶圆锯切工艺。单个模块被贴附在层压基板上,并在模块和基板之间施加填充材料。然后,使用TIM材料将盖子贴附在S-SWIFT模块的前侧,并在背侧附着焊球。

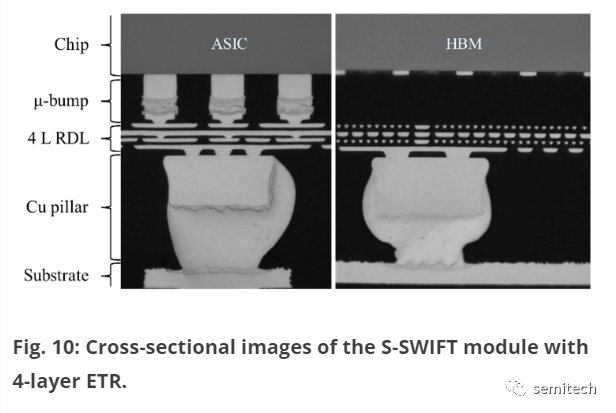

图9显示了S-SWIFT组装过程的顺序图像。即使使用了SAP的标准组装参数而没有进行任何修改,S-SWIFT组装仍然成功地进行了演示,没有出现任何问题。如果对HDFO模块使用了不同的RDL制造方法和不同的有机介电材料,由于机械特性的微小差异和包装中可用的结构区域,它们可能对组装过程没有明显影响。通过图10中的横截面图像可以确定芯片和基板上的所有焊球都良好地附着在HDFO模块上。虽然本文未提及,但通过X射线分析和扫描声学断层扫描(SAT)也已经确认了这一点。因此,可以得出结论,通过使用ETR的S-SWIFT封装实现了多芯片和基板的异质互连。

可靠性性能

由于ETR周围的种子层充当屏障,ETR的结构在电流、热和湿度对可靠性的影响方面具有优势。特别是,该层阻止了Cu离子在偏压高度加速应力测试(BHAST)期间由电流流动进入封装层。

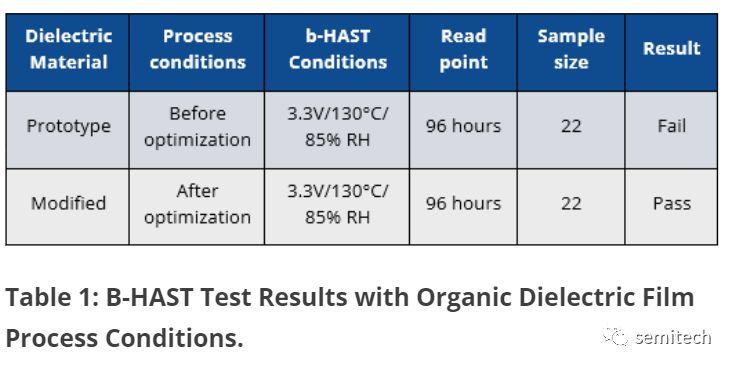

制作了两层具有组合结构电路的ETR以验证Cu离子迁移特性。在85%湿度和130°C条件下,对具有3.3 V偏压的组合电路进行了96小时的BHAST。在此测试中使用了原型有机介电材料。在BHAST后,大多数组合电路由于来自没有屏障层的ETR顶部的Cu离子迁移而短路(表1)。

在BHAST期间,有机介电材料内部的Cu离子迁移现象类似于金属的电沉积过程[9]。组合电路阳极处的Cu被3.3V阳极电位离子化,并通过有机介电材料内部的水分,随着温度的支持而迁移到组合电路的阴极。Cu离子在组合电路的阴极处通过阴极电位被还原为Cu。这一连锁反应导致了组合电路之间的树枝状Cu电极形成,从而引起了短路故障。最初,可以通过控制反应物的扩散来控制该反应。首先,通过控制工艺条件,防止水分吸附到聚合物内部。结果,水分吸收随着优化的工艺条件而减少。接下来,进行了介电材料改进,以防止Cu被阳极电位电离。因此,抑制了Cu的阳极反应和通过水分扩散的反应物。因此,如表I所示,使用改进的有机介电材料和优化的RDL工艺条件制备的样品通过了BHAST测试。这些改进的介电材料和优化的工艺条件被用于成功展示具有4层RDL的S-SWIFT封装的可行性。

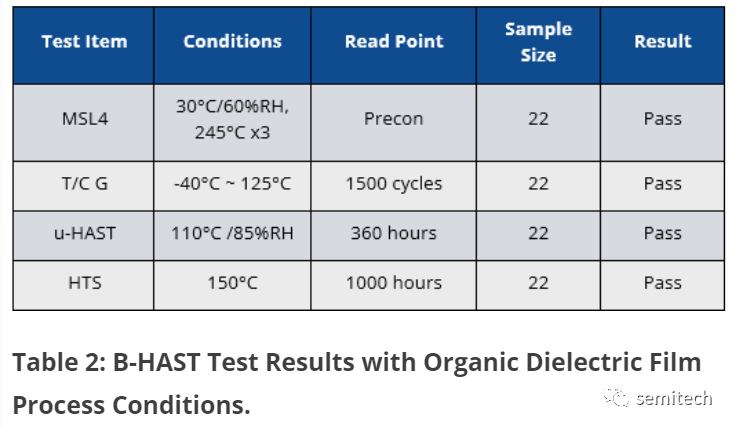

可靠性测试被用于评估S-SWIFT封装中的ETR结构。所有可靠性测试条件,包括湿度浸泡等级4(MSL4),温度循环测试条件G(T/C G),非偏压高加速应力测试(UHAST)和高温存储(HTS)测试都符合JEDEC标准。如表2所示,所有样品通过了T/C G 1500个周期、UHAST 360小时和HTS 1000小时的测试。

结论

嵌入式线路RDL已经成为先进的高密度风扇封装的RDL制造工艺,采用了一种具有减少周期时间和结构优势的新型光刻技术。它提供了一种有效的方法来实现具有小于2/1 μm线/空间和无捕获垫的多层RDL。由于RDL层的平整性,ETR的叠层能力已经确认可以达到6层。通过实施均匀涂覆、CMP和湿法腐蚀等创新的单元工艺技术,成功制备了ETR。通过修改介电材料和优化工艺条件的努力,改善了HAST中的可靠性。

最后,通过使用ETR技术和Flip Chip组装实现了ASIC和HBM的异构集成,成功演示了S-SWIFT封装。组装的单元通过了行业标准的器件级可靠性要求。

-

嵌入式

+关注

关注

5109文章

19314浏览量

310607 -

封装

+关注

关注

127文章

8184浏览量

143952 -

介电材料

+关注

关注

0文章

16浏览量

7159

原文标题:Amkor: 高密度扇出封装与细间距嵌入式线路RDL

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

嵌入式电子加成制造技术

嵌入式电子加成制造技术

应用于高密度电路板的表面粘着式自复式保险丝

探讨高密度小间距LED屏工艺

用于计算和超高密度嵌入式计算板的MIC95410YFL评估板

用于扇出型晶圆级封装的铜电沉积

高密度封装技术推动测试技术发展

高密度(HD)电路的设计 (主指BGA封装的布线设计)

如何看待高密度PCB设计的DFM规则

Cyntec高密度uPOL模块的特点

高密度封装失效分析关键技术和方法

Amkor:高密度扇出封装与细间距嵌入式线路RDL

Amkor:高密度扇出封装与细间距嵌入式线路RDL

评论