今天我们要介绍的时序分析概念是 spice deck 。平时用得可能比较少,是PT产生的一个spice信息文件,可以用来和HSPICE做correlation。我们平时使用PT做得是gate level的时序分析,如果想做transistor level的时序分析,那可以采用HSPICE做电路仿真。

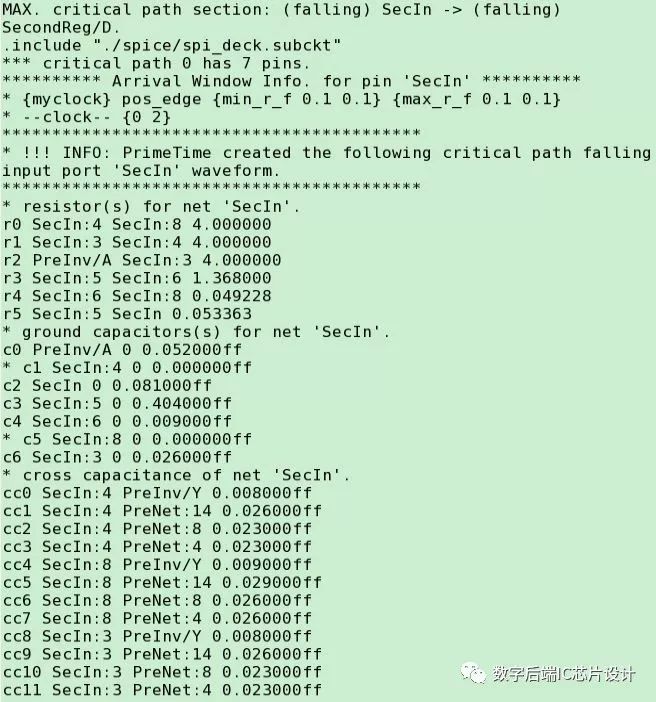

但是,如果要完全仿真整个网表是不大现实的,因为规模太大,速度难以接受。在PT里面,提供了一种方法,可以采用write_spice_deck命令来产生某一条timing path的spice网表文件,里面包含该条timing path上的resistors, capacitors信息。这对表征新工艺库的准确性是很有帮助的。如下图所示:

使用方法

write_spice_deck

pt_shell> write_spice_deck

-header header.spi \\ spice model信息文件

-output testcase.spi \\

-sub_circuit_file ./subckt.spi \\ spice subcircuit信息文件

[get_timing_paths -from A2 -to buf5/A] timing path

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

仿真器

+关注

关注

14文章

1017浏览量

83722 -

时序分析

+关注

关注

2文章

127浏览量

22565 -

SPICE仿真

+关注

关注

1文章

27浏览量

6418 -

时序分析器

+关注

关注

0文章

24浏览量

5277

发布评论请先 登录

相关推荐

时序分析概念之spice deck介绍

平时用得可能比较少,是PT产生的一个spice信息文件,可以用来和HSPICE做correlation。我们平时使用PT做得是gate level的时序分析,如果想做transistor level的

时序分析基本概念介绍<Operating Condition>

今天我们要介绍的时序分析概念是 **Operating Condition** 。也就是我们经常说的PVT环境,分别代表fabrication process variations(工

时序分析基本概念介绍&lt;generate clock&gt;

今天我们要介绍的时序分析概念是generate clock。中文名为生成时钟。generate clock定义在sdc中,是一个重要的时钟概念

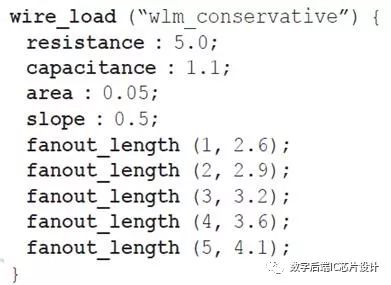

时序分析基本概念介绍&lt;wire load model&gt;

今天我们要介绍的时序分析基本概念是wire load model. 中文名称是线负载模型。是综合阶段用于估算互连线电阻电容的模型。

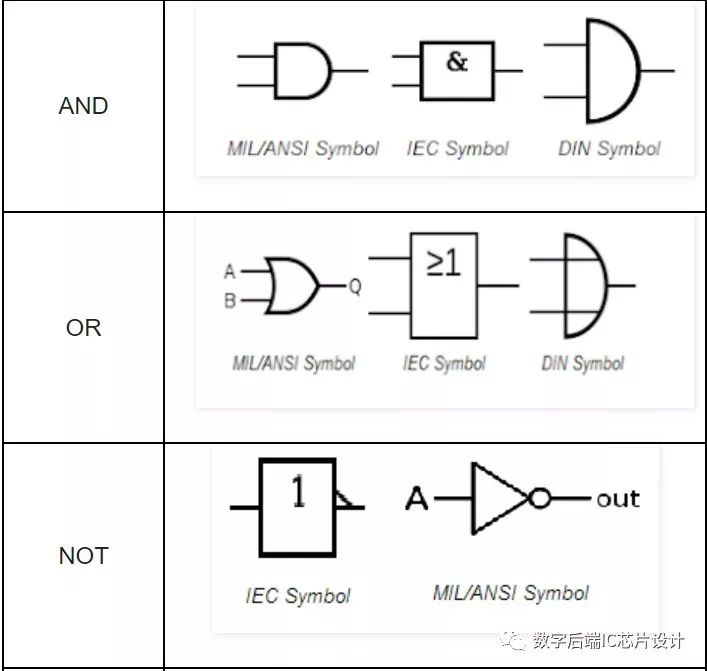

时序分析基本概念介绍&lt;Combinational logic&gt;

今天我们要介绍的时序分析概念是Combinational logic. 中文名组合逻辑单元。这是逻辑单元的基本组成器件。

时序分析基本概念介绍<spice deck>

时序分析基本概念介绍<spice deck>

评论