01

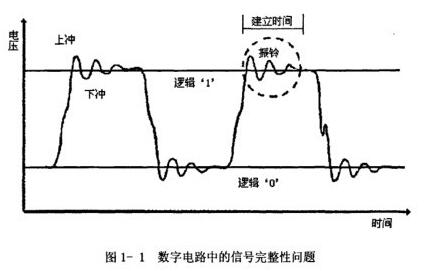

**概述**

串扰:即两条信号线之间的耦合引起的线上噪声干扰。之前的文章咱们说过,传输线可以等效为一段段RLC模型。走线上存在电感,当走线上流过电流,就会产生磁场,磁场在临近导体耦合,又会产生感应电动势,从而产生感应电流。另外,两导体间还会形成等效电容,当电压变化时就会有电流耦合到临近导体。

为了降低串扰带来的影响,走线上通常要满足3W原则,即两根平行走线中心间距保持3倍线宽(一般要求串扰值在信号的5%以内)。

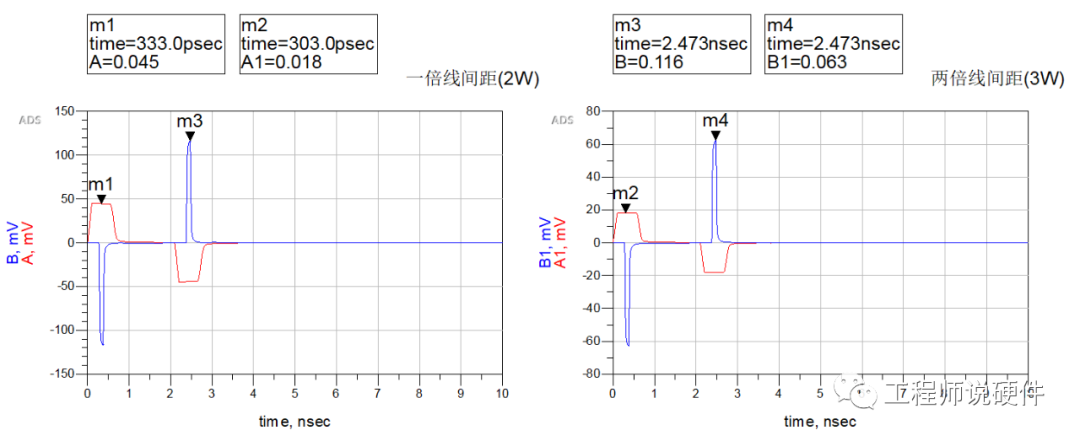

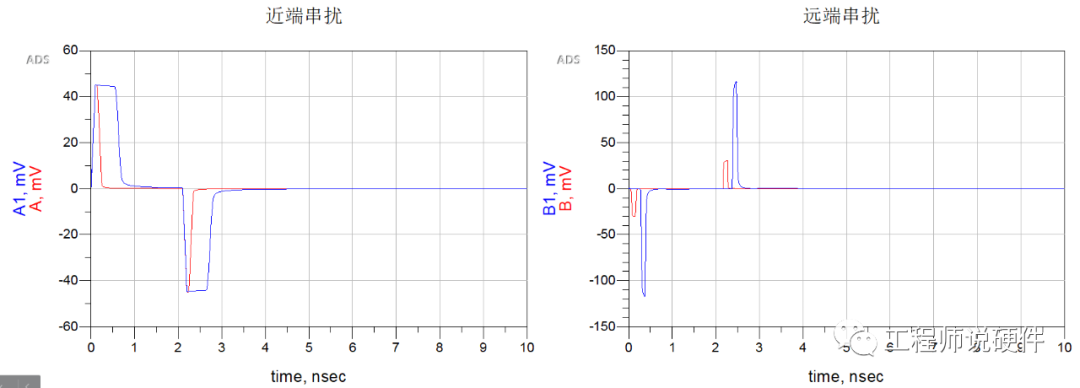

首先通过如下这个实验,带大家直观地认识串扰:

02

**串扰影响因素**

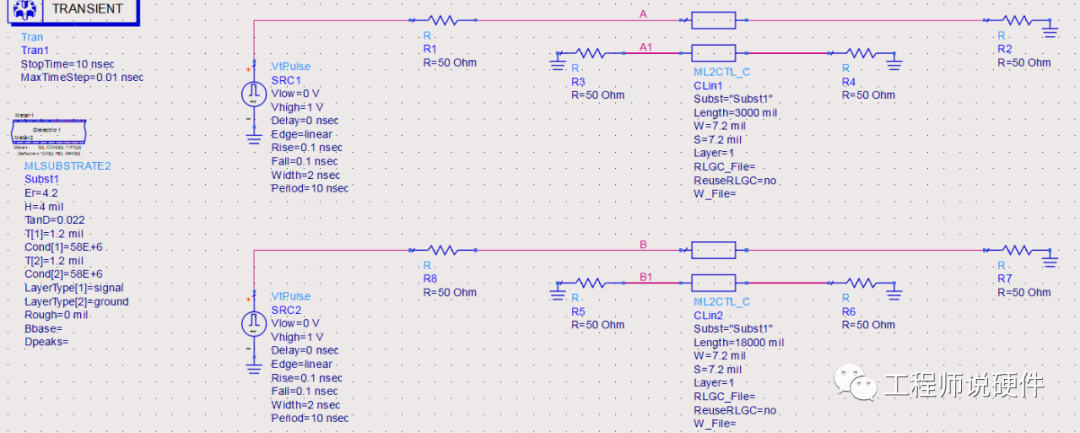

影响串扰的因素有平行走线长度、边沿时间、介质、线间距、阻抗和反射等,下面将通过一列仿真实验直观地介绍其影响。

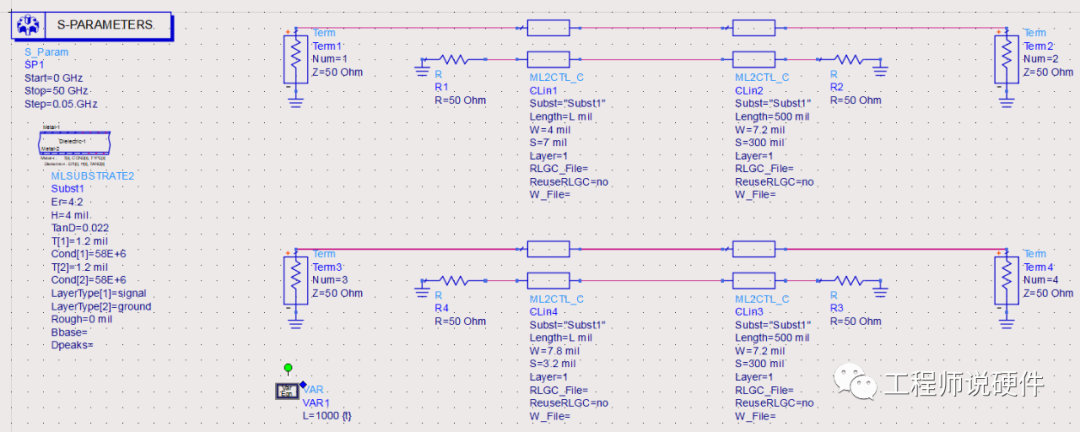

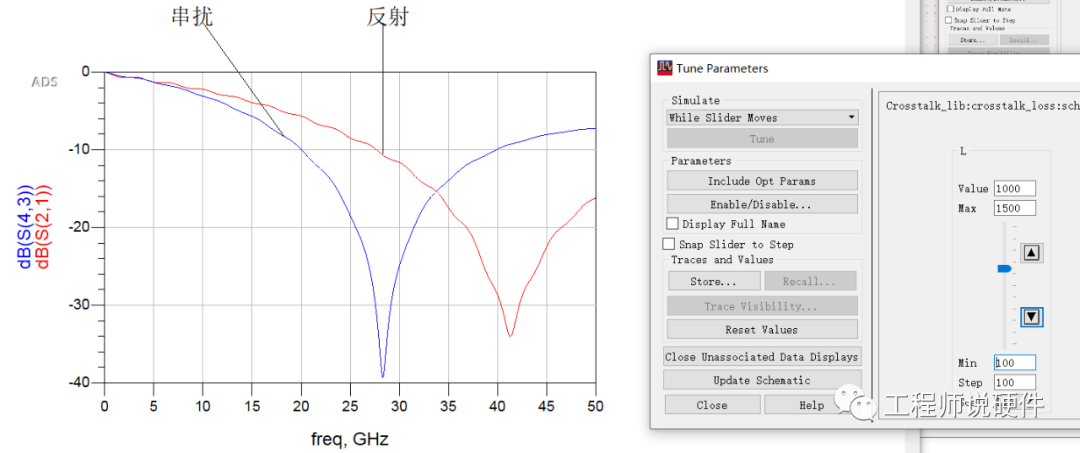

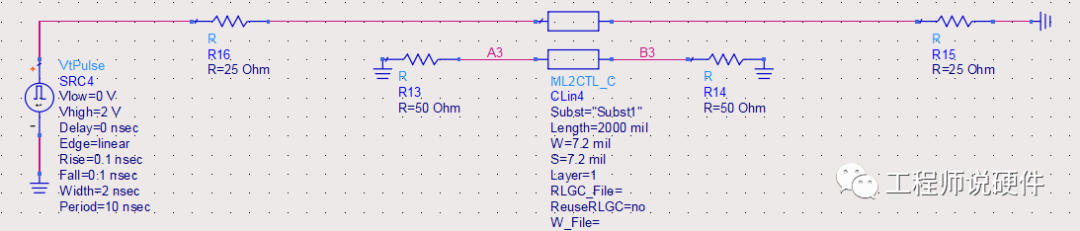

(1)对于有较长平行走线的区域,如果反射与串扰不能兼顾时,优先考虑串扰的影响。相同走线长度下,串扰带来的插损影响要比阻抗不匹配大的多。

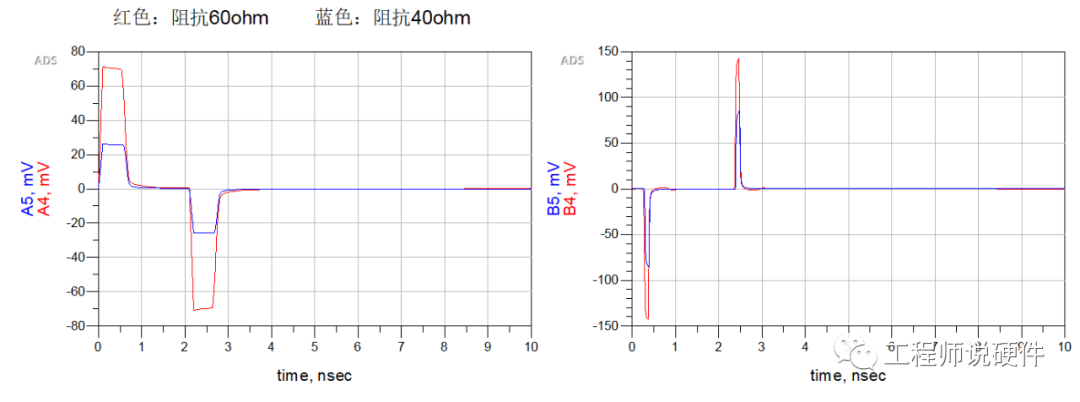

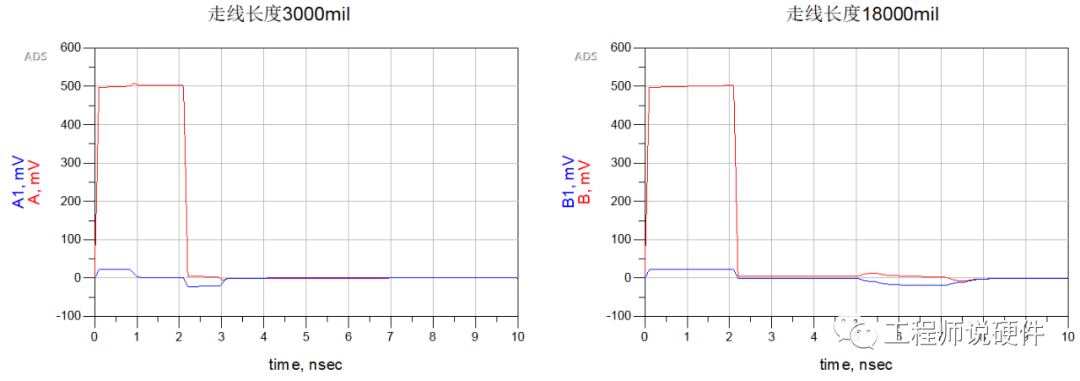

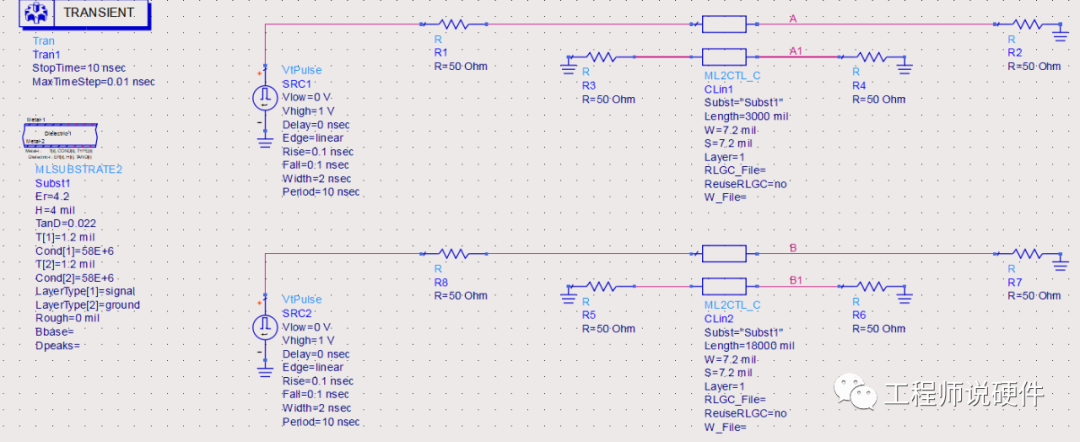

图3、4 ADS仿真:串扰和反射的影响对比

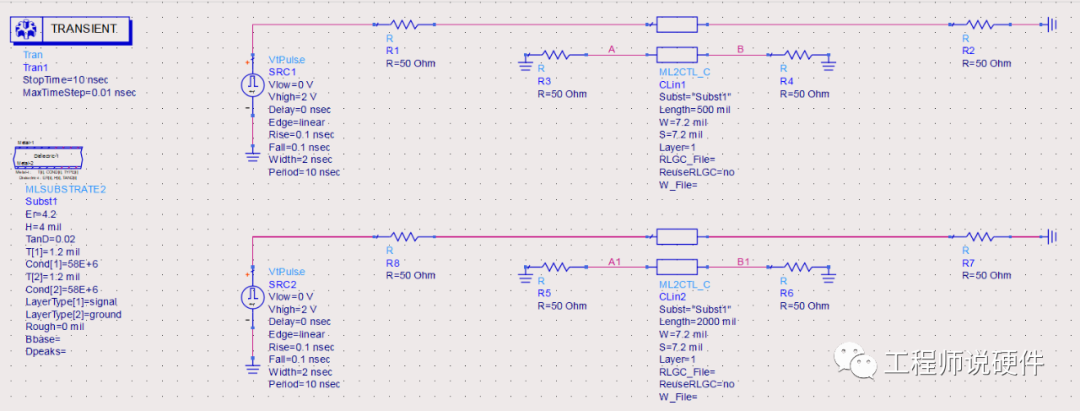

(2)在串扰到达饱和之前,增加平行走线长度会导致远端串扰幅度增加。

图5、6 ADS仿真:不同长度平行走线下的串扰幅度对比(2W线宽)

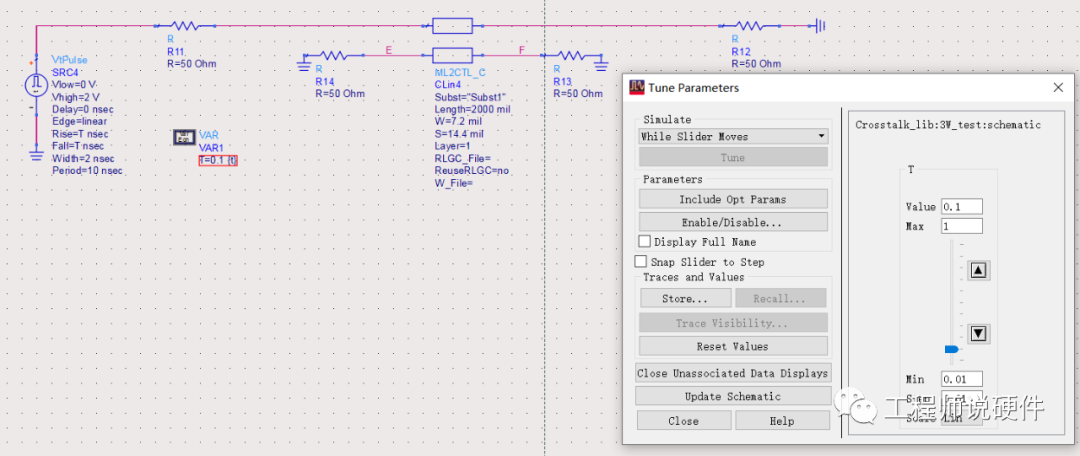

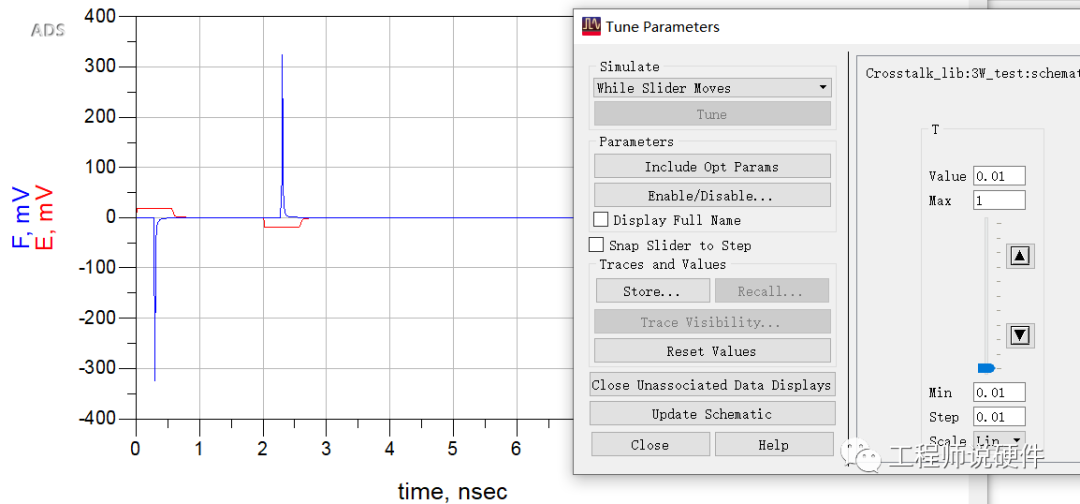

(3)边沿越陡,串扰幅度越大。

图7、8 ADS仿真:信号边沿对串扰幅度的影响

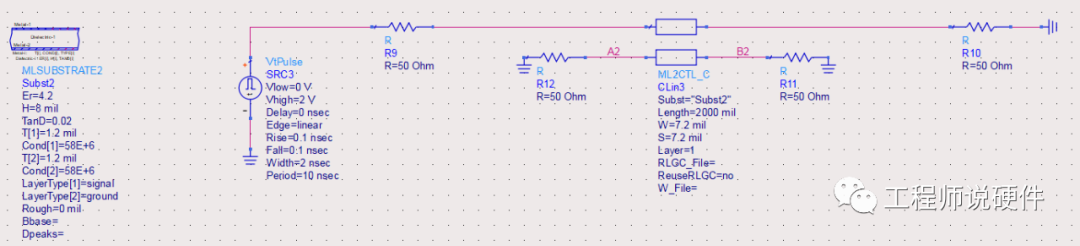

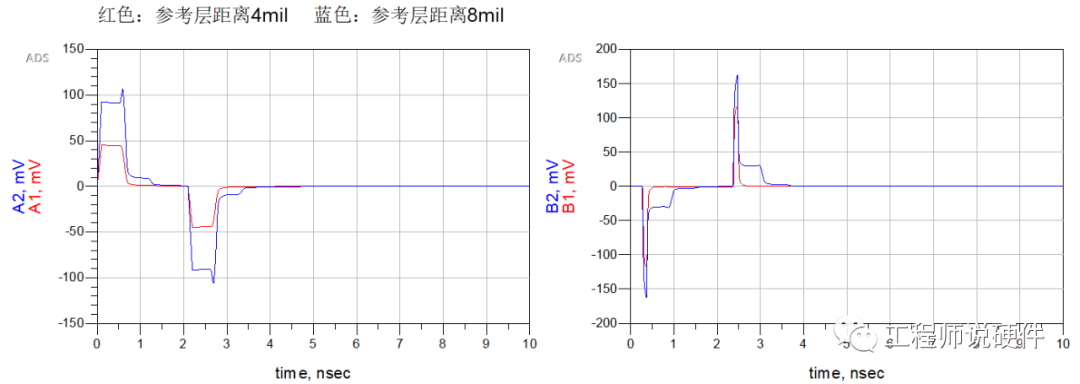

(4)信号层距离参考层越近,传输线和参考层耦合越紧密,临近线串扰越小。

图9、10 ADS仿真:到参考层的距离不同对串扰的影响

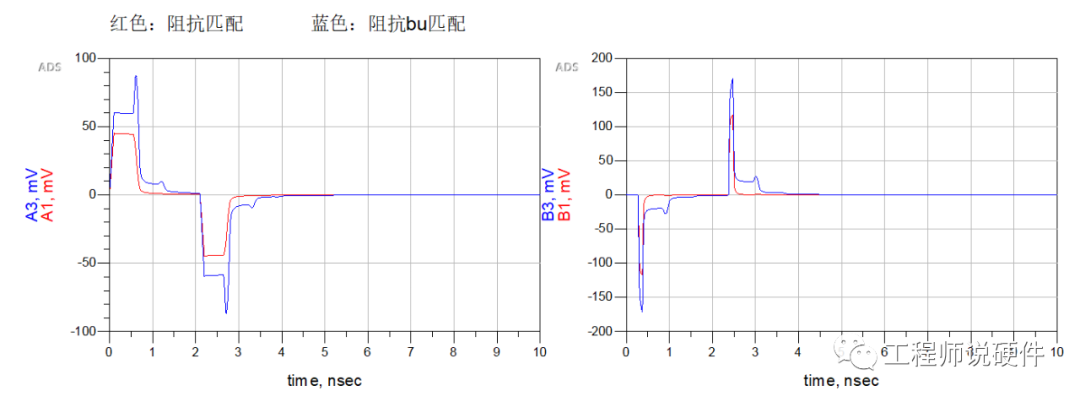

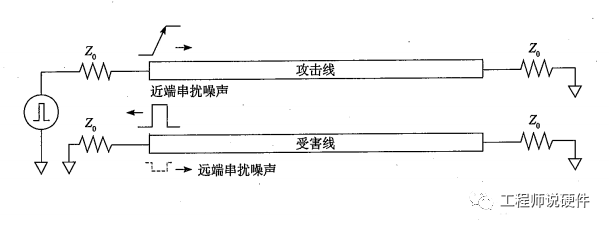

(5)如果线路中存在反射,反射的信号也会引起串扰。因此我们需要保证信号线阻抗的连续性,避免多次反射造成串扰的叠加。

图11、12 ADS仿真:阻抗不匹配增加串扰的影响

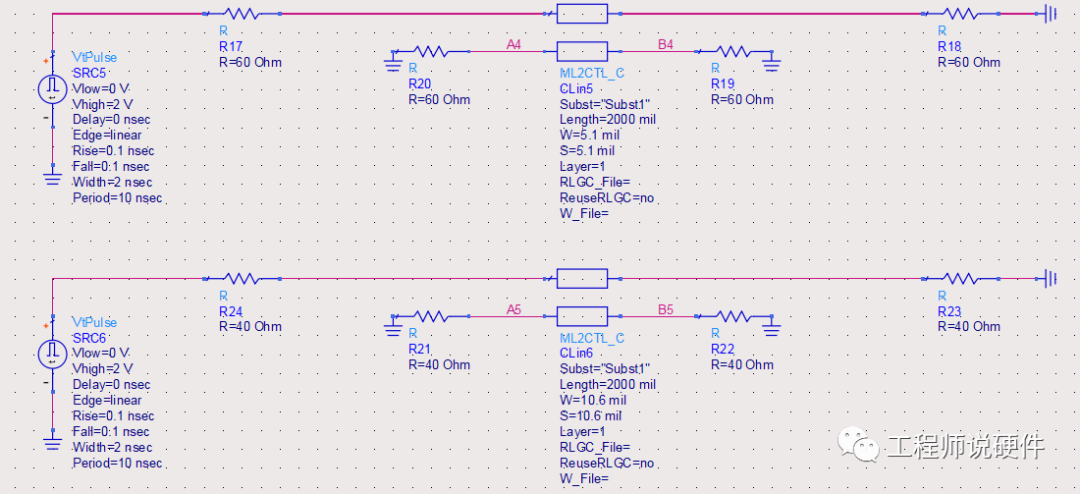

(6)两根平行走线阻抗越小,串扰也越小。

图13、14 ADS仿真:走线阻抗对串扰的影响

(8)信号线间距越大,串扰越小。概述中已演示案例,此处不在赘述仿真实验了。

03

**近端串扰和远端串扰**

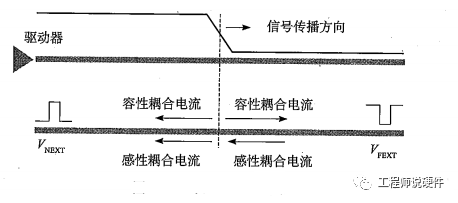

串扰值测量通常在受害线的两端,靠近源端的为近端(后向串扰),反之为远端(前向串扰)。

容性耦合的能量会向远端与近端传输,感性耦合则只朝着信号相反方向流动。因此,近端串扰的能量为容性与感性耦合之和(Ic+IL),而远端串扰则为容性与感性耦合之差(Ic-IL)。如下为近端和远端串扰的示意图。

图15、16 近端和远端串扰示意图

(1)信号在向前传播的时候,近端串扰持续产生,方向跳变沿相同,幅度稳定后不变,波形宽度逐渐增加。

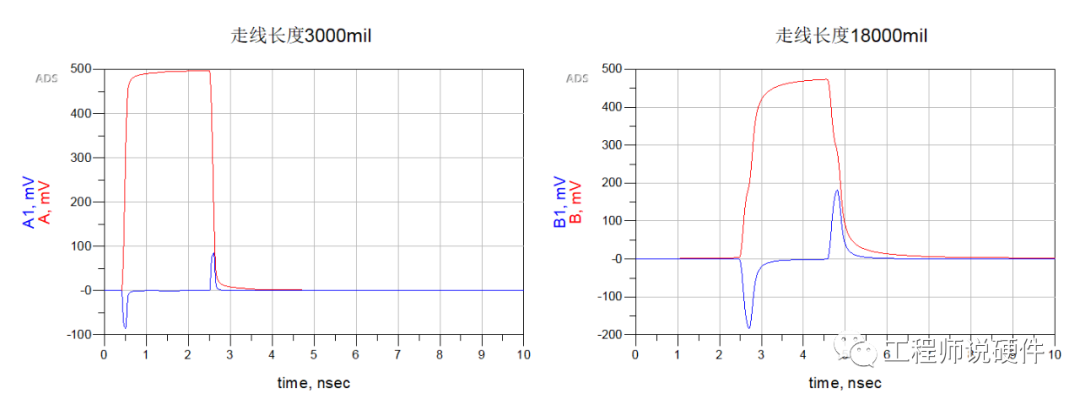

图17、18 ADS仿真:不同走线长度的近端串扰

(2)远端串扰随着信号向前传播,不断叠加,幅度逐渐增强(不会无限制增加,有饱和点)。远端串扰的波形宽度等于信号边沿时间。

图19、20 ADS仿真:不同走线长度的远端串扰

审核编辑:刘清

-

信号完整性

+关注

关注

68文章

1416浏览量

95609 -

耦合器

+关注

关注

8文章

727浏览量

59851 -

ADS仿真

+关注

关注

1文章

71浏览量

10504 -

RLC

+关注

关注

1文章

116浏览量

39010

原文标题:信号完整性基础--串扰(一)[20230706]

文章出处:【微信号:EMC_EMI,微信公众号:电磁兼容EMC】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

常见信号完整性的问题之PCB设计串扰的原因与Altium Designer中的串扰消除技术

【连载笔记】信号完整性-串扰和轨道塌陷

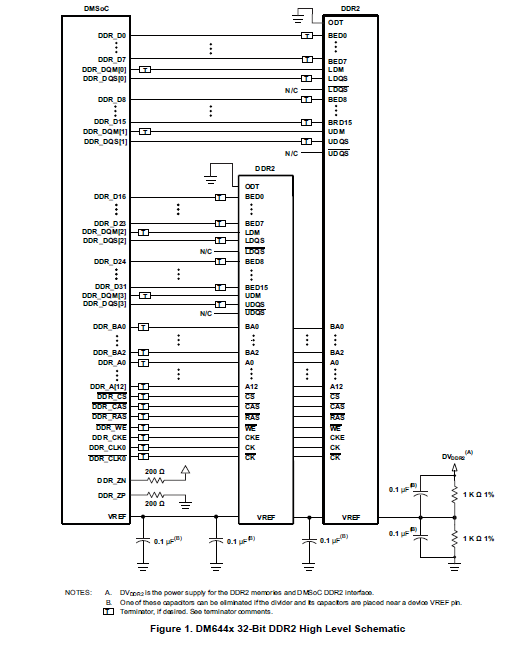

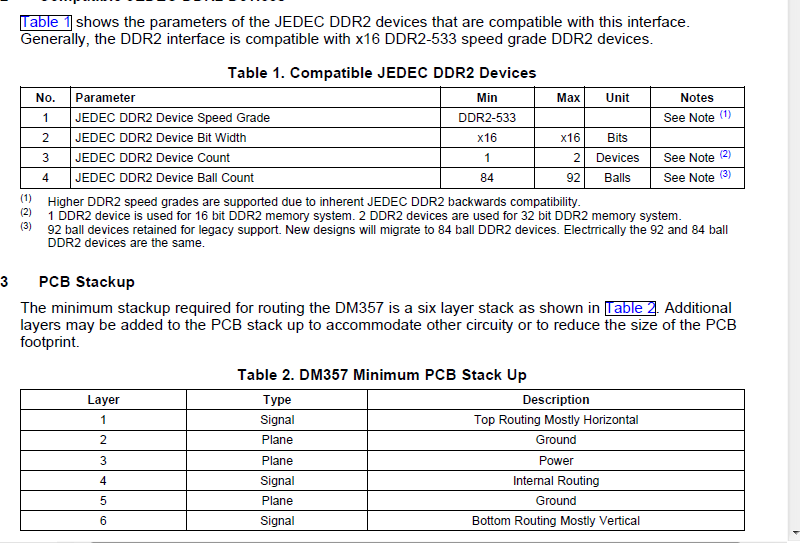

如何实现TMS320DM644x数字媒体系统芯片DMSo实施DDR2PCB布局

如何实现在TMS320DM357数字媒体系统芯片DMS实施DDR2PCB布局

PCB设计信号完整性与串扰问题分析

信号完整性基础-串扰

信号完整性基础-串扰

评论