什么是硬件加速引擎

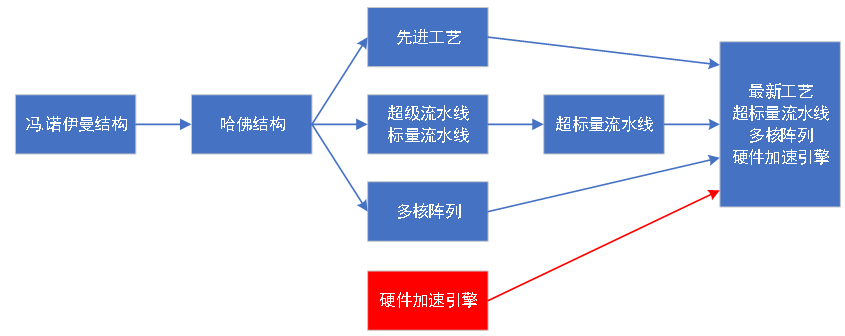

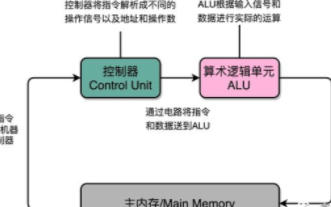

普通计算机用指令运算速度衡量计算性能,而超算则通常用浮点运算速度来衡量其性能。但不管是指令运算还是浮点运算,都脱离不了CPU进行流水线式的指令计算。尽管我们可以通过用先进工艺、采用超标量流水线结构处理器,甚至是多核的阵列来提升CPU的计算性能,但这仍然没有突破“重围”,我们一直在一亩三分地徘徊。

我们在个人电脑上打开过多的应用时,由于CPU数量及性能受限,无法承载过多的应用,电脑会逐渐变得很卡。但单纯提高CPU的性能,空间受限制,且代价很大。除非是超算中心等首先以性能为目标,对能耗比不那么敏感的应用,否则消费类芯片核心竞争力仍以能功耗及性能为王,承载到芯片上就是PPA(Power Performance Area)。

摩尔定律的终结,我们很难再单一的从CPU身上榨出更多的性能。如果我们将某些复杂耗时的计算,采用专用芯片实现,在完成后再将结果返回给CPU,这样我们就实现了专用的加速引擎。典型的以个人电脑为例,采用独立显卡的配置远比仅有集成显卡电脑有着更好的体验感,因为Nvdia/AMD显卡的GPU,专用图形图像加速运算,降低了CPU的负荷,提高了整机处理应用的能力。

至此,我们的主角终于上场了,世界的最后一块拼图,也终于完整了,如下图所示,为CPU计算加速的方法,终点是最新工艺下,集成硬件加速器的多核超标量流水线处理器。

而我们最后入场的观众,即上图中红色部分,就是硬件加速引擎。正如前文所述,显然从CPU的一亩三分地,已经很难再开出质变的花,但硬件加速引擎的引入,让我们进入了硬件加速的新时代。

我们再梳理一下新提出的概念:硬件加速引擎,也称为硬件加速器,是一种采用专用加速芯片/模块,替代CPU完成复杂耗时的大算力操作,其过程不需要或者仅少量CPU的参与。

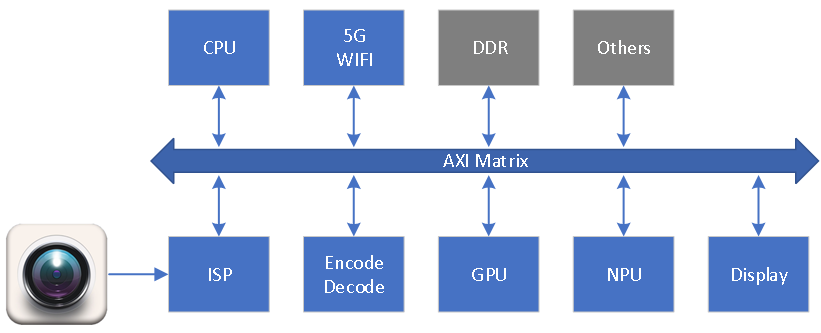

典型的以GPU、DSP、ISP、NPU为例,就是专用的硬件加速引擎。硬件加速引擎的出现,一方面提升了SOC的整体计算性能,另一方面也降低了同等应用场景,对CPU的性能需求。举例,apple在2021年WWDC上发布了采用自研SOC的全新Macbook系列产品,使用的就是最新自研的号称地表最强的M1芯片,其规模达到了160亿门晶体管,如下图所示:

M1采用了当时最新的5nm工艺制程,集成8核的CPU,号称在同等功耗下,达到了2倍目前CPU的最快性能。更为重要的是,M1还集成了众多专用的硬件加速引擎,协助CPU完成了很多复杂耗时的运算,统计分析主要如下表所示:

| 序号 | 硬件加速引擎 | 功能/性能详细描述 |

| 1 | GPU | 图像运算单元,集成128个执行单元,可同时执行24576个线程,运算能力高达2.6TFLOPS。 |

| 2 | Neural Engine | 16核神经网络加速引擎(NPU),专用卷积网络推理计算加速,每秒可以进行11亿万次操作。 |

| 3 | Media Encode & Decode Engine | 多媒体视频编解码引擎,硬件加速完成视频的编解码功能,支持AVS、H.264、H.265等制式。 |

| 4 | Advance Image Signal Processor | 先进的图像信号处理引擎(ISP),实现实时的图像采集、Demosaic、3A、2/3D降噪等图像处理功能。 |

勾勒了一个粗糙的M1的架构图(其实很多多媒体芯片也是类似的),如下所示,我们简单梳理一下相关模块的工作流程。

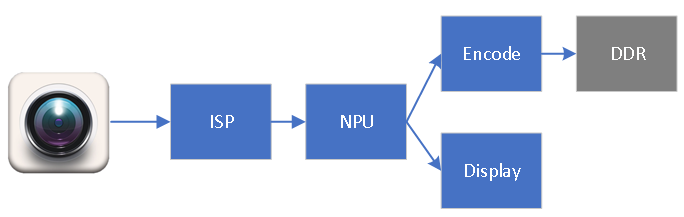

以一个AI人脸识别的视频拍摄的场景为例,整体计算的流水线如下图所示,当然每一步还需要CPU参与配置调度,以及DDR读写缓存。其中上半部分,采用ISP→NPU→Encode→DDR流水线,实现了实时AI人看脸识别视频的存储;下半部分,实现了实时人脸检测的显示。

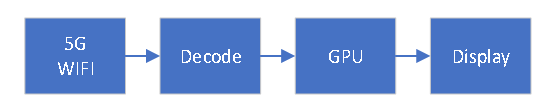

再以体验一个在线游戏为例,采用下图的流水线,实现了游戏的实时解码,图形图像的加速运算,以及实时显示功能。这个过程同样每个模块需要DDR参与读写,此外,除了少量CPU的配置及调度,CPU很少参与计算,主要由专用硬件加速引擎完成实时的运算。因此专业的事情,专用的模块做,CPU可以用来做更为复杂的操作,比如文件管理,资源优化等。

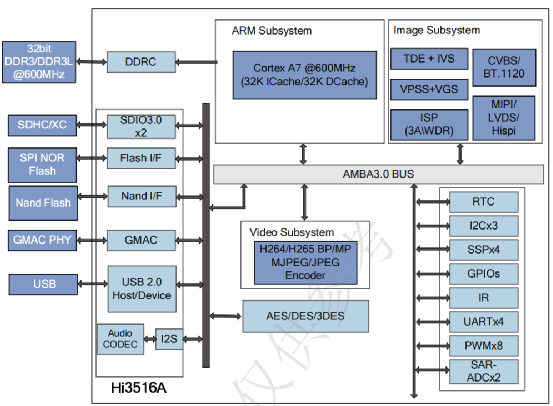

上述例子,CPU与硬件加速引擎协同工作,一起打造了一款号称地表最强的SOC。这里我们再举一个例子,以采用硬件加速引擎的方式,降低了产品对CPU的性能要求,从而采用低成本的ARM,在提升性的前提下进一步降低成本。如下图所示,为海思Hi3516A监控芯片的硬件架构框图。

该芯片采用单核A7内核作为处理器,主频运行在600MHz,框图左侧为SoC的高速模块,右下角为SoC的低速模块,中下部分AES/DES/3DES为加解密模块,右上角的CVBS/BT1120为显示接口,MIPI/LVDS/Hispi图像采集接口,以上这些组成了SoC的Boot最小系统,以及基本输入输出单元。

但这是一款IPC监控芯片,主要用以实现视频图像采集,编码传输等功能,为了减小CPU的开销,协同完成一些复杂的视频运算,Hi3516A集成了几个重要的硬件加速引擎,使得其在低码率,高图像质量,低功耗方面持续引领行业水平。如下表所示,为Hi3516A芯片继承的硬件加速引擎,主要如下:

| 序号 | 硬件加速引擎 | 功能/性能详细描述 |

| 1 | TDE | Two Dimensional Engine,硬件加速实现图形的绘制,大大减少对CPU的占用,同时又提高了DDR的利用率。 |

| 2 | IVS | Intelligent Video Engine,模块提供了常用的一些智能分析算法中的一些CV算子,采用硬件实现方式替代CPU进行OpenCV图像运算。 |

| 3 | VPSS+VGS | Video Processing Sub-System/Video Graph System,硬件加速实现图像显示后处理功能,包括降噪、缩放、裁剪、叠加、旋转等功能。 |

| 5 | ISP | 图像信号处理引擎(ISP),实现实时的图像采集、Demosaic、3A、2/3D降噪等图像处理功能。。 |

| 6 | Video Subsystem | 视频编码引擎,支持H.264、H.265等制式以及ROI编码,最大支持5M Pixel分辨率。 |

IPC芯片可以用规格较低的Cortex A9系列CPU,得益于芯片集成了如上表中专用的硬件加速引擎。采用专用计算模块完成了图像处理、视频编码、显示后处理等功能,使得CPU只需要参与配置及调度,同时才有了资源去处理复杂的操作系统任务。

我们总是不断在追求更快,所以我们穷尽一切办法去达成目标。硬件加速引擎在传统CPU无法实现质变的基础上,实现了计算能力的突破。硬件加速引擎虽然有其专用的局限性,但协同CPU处理,可以以更低的成本及功耗,实现更高的性能,这是当前也是未来计算芯片的大势所趋。

至此,相信你已经理解了硬件加速引擎的非凡意义,我们也可终于可以提出我们的主题——图像加速引擎。Hi3516A中的硬件加速引擎都是图像相关的,本书也将介绍一些基于图像算法方面的加速,就是我写本书的初衷。

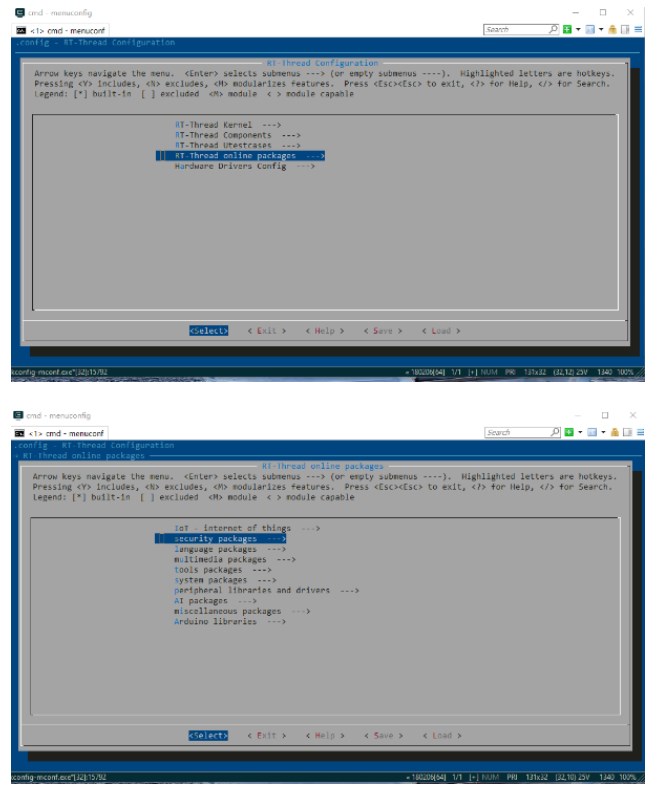

本书将从传统图像加速算法入手,从原理到实现,介绍图像算法的理论及设计,并且基于Matlab与FPGA开发,讲解如何进行硬件加速实现的流程方法。本书适合从事软件图像开发的朋友,可以提升你对图像算法硬件加速的认知;本书同样也事业FPGA开发的朋友,可以让你全流程了解如何采用FPGA加速实现一个图像算法。

在接下来的篇幅,我将从格式转换、滤波、增强、二值化、锐化、缩放等传统基础图算法入手,从原理到Matlab设计、FPGA加速实现进行由浅入深的详细介绍。接着,以深度学习LeNet为例,介绍如何在FPGA实现最简单的硬件加速卷积神经网络。最后,作为画龙点睛之笔,我们站上更高的层次,介绍一下传统ISP和新兴的AISP的基本理论概念,以及未来图像硬件加速的发展走向。

审核编辑:汤梓红

-

dsp

+关注

关注

553文章

7998浏览量

348842 -

芯片

+关注

关注

455文章

50771浏览量

423385 -

gpu

+关注

关注

28文章

4735浏览量

128917 -

计算机

+关注

关注

19文章

7492浏览量

87902 -

硬件

+关注

关注

11文章

3323浏览量

66210

原文标题:什么是硬件加速引擎?

文章出处:【微信号:数字芯片设计工程师,微信公众号:数字芯片设计工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

MPU6050简介

CAN通信总线接口和XFMC内存扩展接口

MPU6050相关资料分享

N32G4FR系列芯片用户手册

N32G457系列芯片用户手册

N32G452系列芯片用户手册

N32L40x系列芯片产品手册

N32G4FR系列芯片数据手册

N32G452系列芯片数据手册

基于MPU-3000™系列运动处理组件的三轴陀螺

基于VxWorks的硬件加速技术探讨

图像处理硬件加速引擎是什么 如何提高CPU芯片性能

什么是硬件加速引擎?

什么是硬件加速引擎?

评论