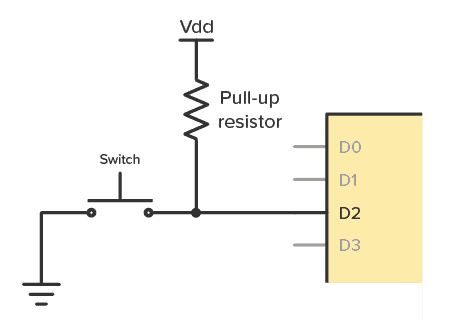

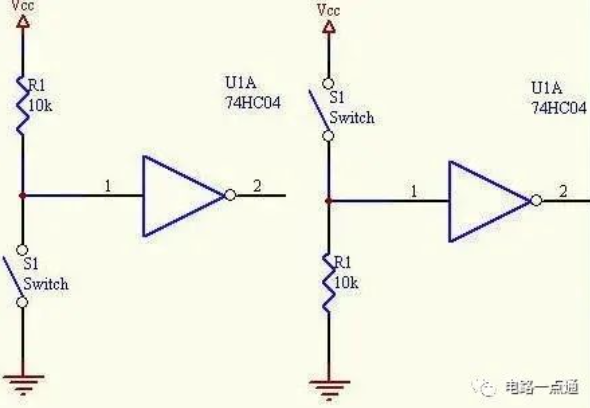

在构建电路时,常会使用到上拉电阻,我们经常在一些数字电路中看到它。它只是一个电阻,从输入端连接到电路的正电源VDD。如下图所示:

上拉电阻用于确保在未按下按钮时输入引脚处于高电平状态。如果没有这颗电阻,那么输入电压将是浮动的,并且会伴随着输入在HIGH和LOW之间随机变化的风险,此外它会产生噪声。

一、如何选择上拉电阻值?

规则一:值不能太高。

上拉值越高,输入电压越低。重要的是要让电压足够高,使芯片将其视为HIGH或逻辑1输入。例如,如果使用带有10V电源的CD4017,则输入端至少需要7V才能将其视为高电平。

规则二:也不能太小。

例如,如果选择100Ω,问题是按下按钮时会有大量电流流过它。例如,使用9V电源,接上100Ω的电阻,那么电流为90mA。这是不必要的功耗浪费,这也意味着电阻器需要承受0.81W的功率。值得注意的是,大多数电阻器只能承载高达0.25W的功率。

二、得出的结论

选择上拉电阻时的经验法则是选择至少比引脚输入阻抗(或内阻)小10倍的电阻值。通常,一个10kΩ的上拉值就可以解决问题。

三、上拉电阻如何工作?

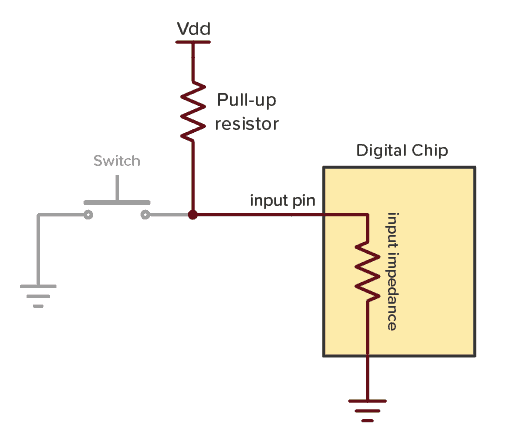

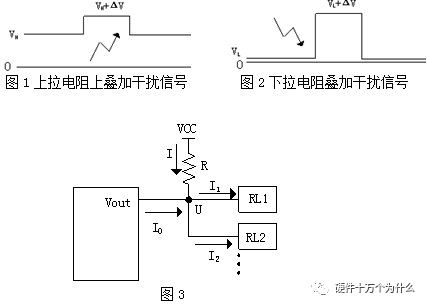

我们可以将集成电路 (IC) 的输入引脚视为具有接地的电阻器。这称为输入阻抗:

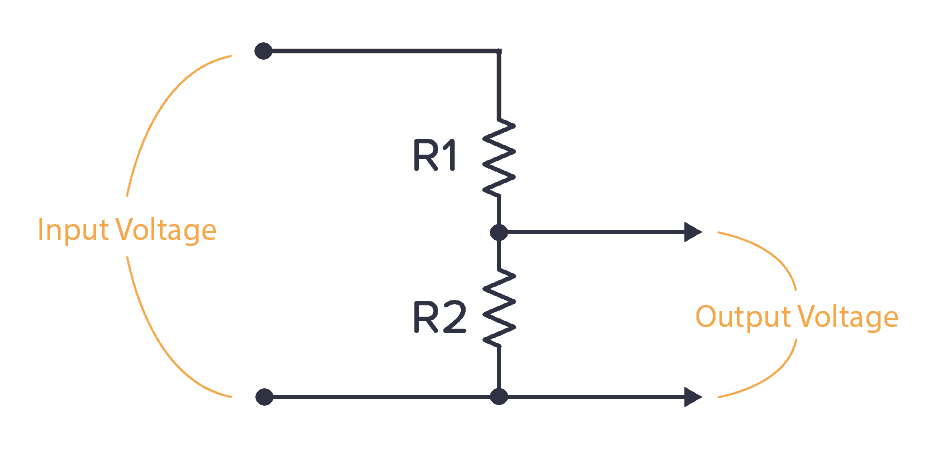

这两个电阻组成了一个分压器。如果查看标准分压器电路,可以看到上拉电阻为R1,输入阻抗为R2:

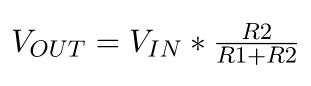

我们可以使用分压器公式找到未按下按钮时输入引脚上的电压:

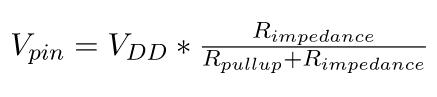

下面重命名了公式的组成部分以适应上拉示例。输入电压为上拉示例中的VDD 。输出电压是输入引脚上的电压。于是公式就变成了:

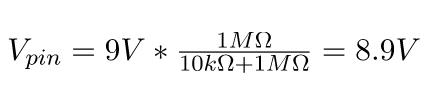

示例计算

假设您的芯片的输入阻抗为1MΩ(对于许多芯片来说,100kΩ到1MΩ是正常的)。如果您的电源是9V,并且您选择了一个10kΩ

的上拉电阻,那么输入引脚上的电压是多少?

输入引脚上的电压为 8.9V,足以充当高电平输入。

一般来说,如果坚持使用不超过输入阻抗十倍的上拉电阻器的经验法则,将确保必须具有至少90%的VDD电压输入引脚。

如何找到IC的输入阻抗?

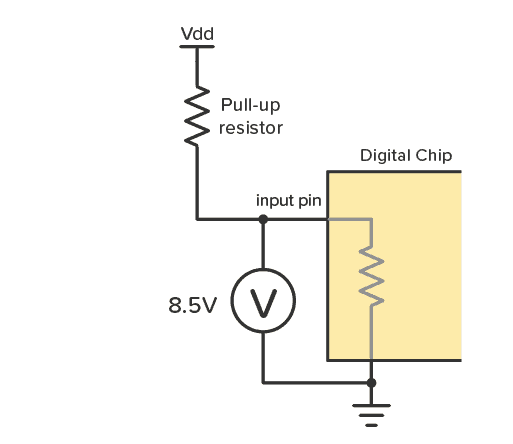

我们可以很容易地测量出芯片的输入阻抗。阻抗实际上是电阻的一个术语,它可以根据频率而变化。但是对于这种上拉情况,我们只处理直流电流。

将例如10kΩ的上拉电阻连接到芯片的输入端,并测量输入端的电压。

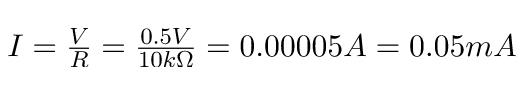

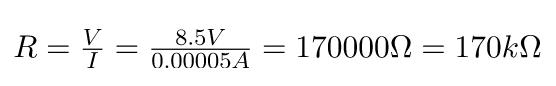

假设你测量时得到8.5V。那么,通过欧姆定律就能计算流过电阻器的电流。电阻两端的电压降为9V–8.5V=0.5V,因此将得到:

有0.05mA电流流过电阻器,因此也通过输入引脚下降到地。再次,使用欧姆定律找出电压降为8.5V和电流为0.05mA的物体的电阻:

输入阻抗为170kΩ。这意味着该输入的上拉电阻不应超过17kΩ。

-

上拉电阻

+关注

关注

5文章

360浏览量

30624 -

阻抗

+关注

关注

17文章

958浏览量

45981

发布评论请先 登录

相关推荐

上拉电阻如何工作?如何选择上拉电阻值?

上拉电阻如何工作?如何选择上拉电阻值?

评论