PCIe技术,数据交互的高速公路

PCIe总线的前身是PCI(Peripheral Component Interconnect)总线协议,由英特尔于1992年提出,并联合业界合作伙伴成立了名为PCI-SIG (PCI Special Interest Group)(PCI 特殊兴趣组J)的企业联盟,负责PCI总监的标准制定和推广。

PCI提出的目的是简化主板的总线接口,并提高数据传输总线的性能。由于PCI总线跟ISA总线都使用了并行总线设计,所以传输速度会受到影响。此外,PCI总线由于采用了带宽共享机制,因此在高负载下会出现设备之间会抢带宽的现象。最后,由于PCI不支持热插拔,因此也不能更好的支持更换磁盘的操作。

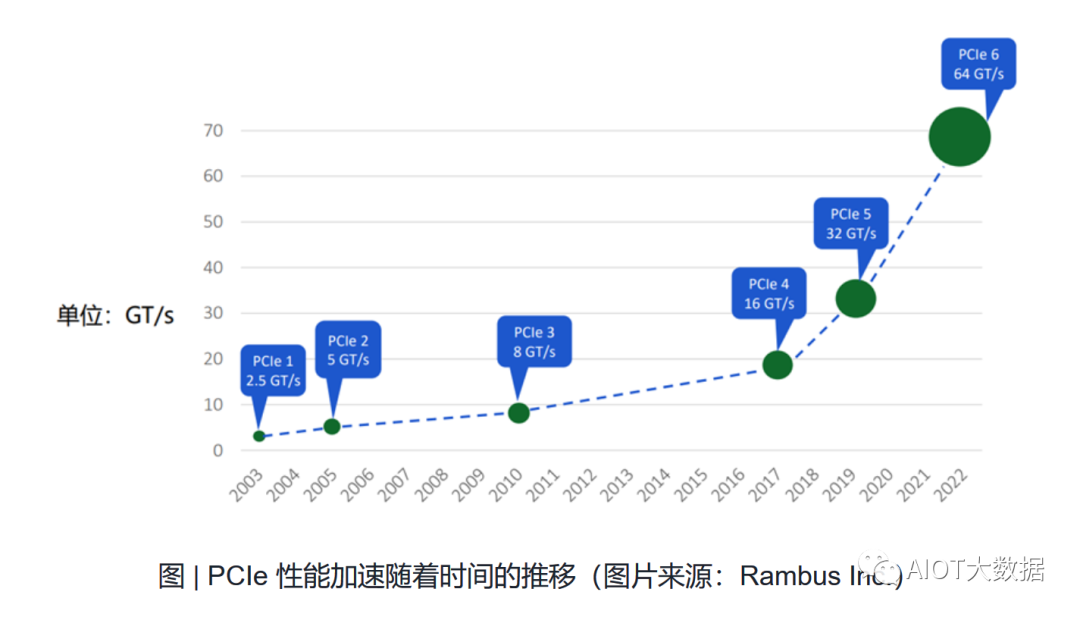

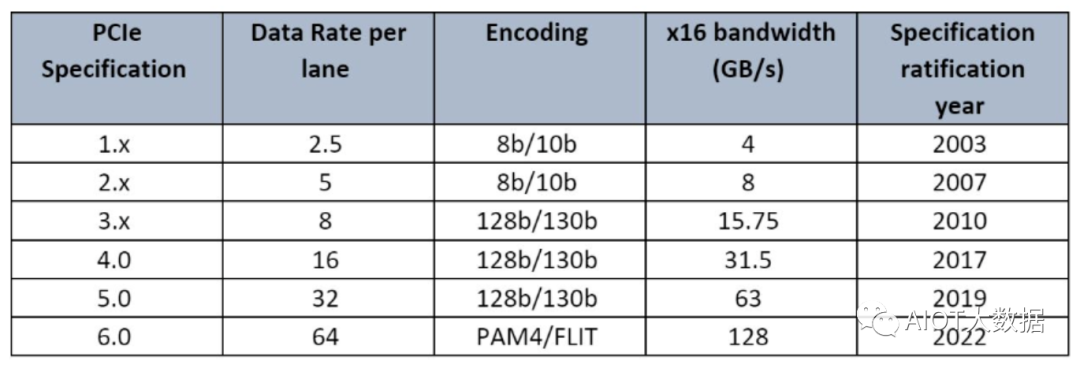

为了解决PCI总线的缺陷,2004年英特尔联合伙伴对PCI技术进行了升级,正式发布了PCI Express(简称PCIe)总线,并陆续推出了PCIe1.0、PCIe2.0、PCIe3.0、PCIe4.0、PCIe5.0和PCIe6.0规范,不断的进行带宽优化。

实际上,近两年火爆的CXL技术,其底层就是基于PCIe技术。随着大数据分析、视频渲染等技术的飞速发展,以及异构计算模式的兴起,对于CPU与GPU、CPU与DPU等之间数据交互的带宽提出了更高的要求。于是,PCIe 6.0 标准应运而生。

受到人工智能/机器学习(AI/ML)和数据中心、云、高性能计算等数据密集型应用的驱动,数据中心架构正在持续演进,这对PCIe接口提出了更高的要求。作为CPU与存储之间的连接通道,PCIe自推出以来始终扮演着重要的作用。随着大数据分析、视频渲染等技术的飞速发展,PCIe6.0标准于去年初正式发布,相比较上一代PCIe 5.0规范,带宽再次翻倍,达到了64 GT / s。

PCI Express 6.0 (PCIe 6.0) 规范由 PCI-SIG 于 2022 年 1 月发布。最新一代的 PCIe 标准带来了许多激动人心的新功能,旨在提高计算密集型工作负载的性能,包括数据中心、 AI/ML 和 HPC 应用程序。

虽然PCIe 5.0正在广泛流行并被主流设计所采用,但业界急切地等待PCIe 6.0的推出。好消息是PCIe 6.0带来了更高的性能和一系列新特性,包括64GT/s的数据速率,采用具有吞吐量和延迟优势的 FLIT,以及新的低功耗状态L0p,实现了真正的带宽扩展来降低功耗。

自 PCIe 3.0 以来,每一代新标准的数据速率都翻了一番。 PCIe 6.0 将数据速率提高到每秒 64 千兆传输 (GT/s),是 PCIe 5.0 的两倍。 对于显卡和网卡典型的 x16 链路,链路带宽达到每秒 128 GB (GB/s)。 与前几代产品一样,PCIe 6.0 链路是全双工的,因此它可以同时在两个方向上提供 128 GB/s 的带宽,总带宽容量为 256 GB/s。

PCIe 除了已经广泛扩展到服务器和 PC 之外,其规模使其对物联网、汽车、医疗和其他领域以数据为中心的应用程序具有吸引力。 也就是说,PCIe 6.0 的初始部署将针对需要尽可能高带宽的应用程序,这些应用程序可以在数据中心的核心找到:AI/ML、HPC、网络和云图形。

下图显示了 PCIe 规范随时间的演变:

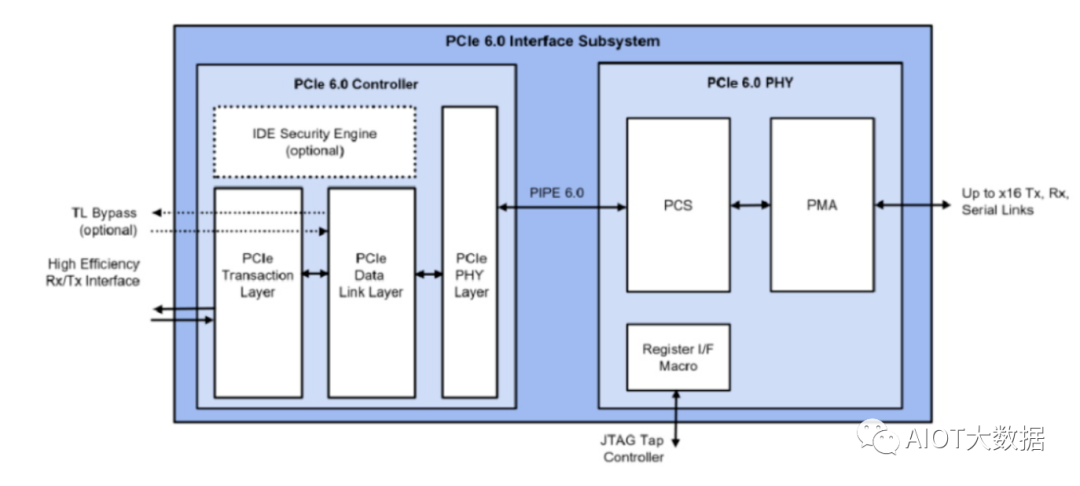

芯片设计周期通常都非常长,而通过采用PCIe 6.0接口子系统,可以降低芯片设计人员的设计复杂性。这是因为在过去,芯片设计人员需要把PHY和控制器单独拿来使用,同时还要重复一些冗杂的验证工作,而现在PCIe 6.0接口子系统集成了控制器和PHY,可以直接在其芯片中实施。

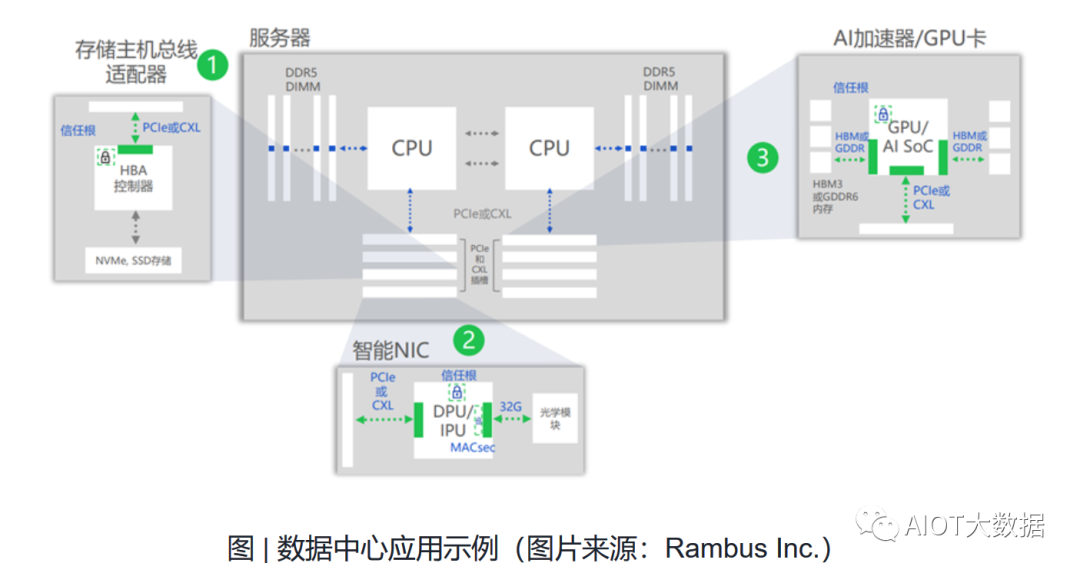

以数据中心三个应用为例,每个示例都有一个存储主机总线适配器、一个智能网卡和一个AI加速器或GPU卡。我们看到,PCIe PHY和控制器的组合提供了一个成熟的接口,可以从服务器主板上的PCIe插槽和物理接口连接到控制器芯片上。这三个例子都保证了PCIe或CXL接口是经过硅验证的,并且不会增加设计复杂性。

PCI Express(PCIe)6.0对于高性能计算、AI和存储SoC开发者来说,理解并考虑如何最好地应对即将面对的关键变化,以及由此带来的设计挑战变得至关重要。这些变化包括从非归零(NRZ)转换到脉冲幅度调制4(PAM-4)信号导致对噪声的敏感性增加,转向FLow控制器unIT(FLIT)导致控制器行为和性能的变化,PHY与控制器之间紧密集成的需求,以及针对互操作性和测试的规划。

确保顺利成功地过渡到PCIe 6.0,开发者需要考虑的PCIe 6.0的三个主要变化如下:

数据速率从32GT/s翻倍至64GT/s

从NRZ编码转换到PAM-4编码,以及由此带来的纠错影响

从传输的可变大小TLP到固定大小FLIT

前两项变化紧密相关,并且受到要传输PCIe 6.0信号的通道性质的影响。

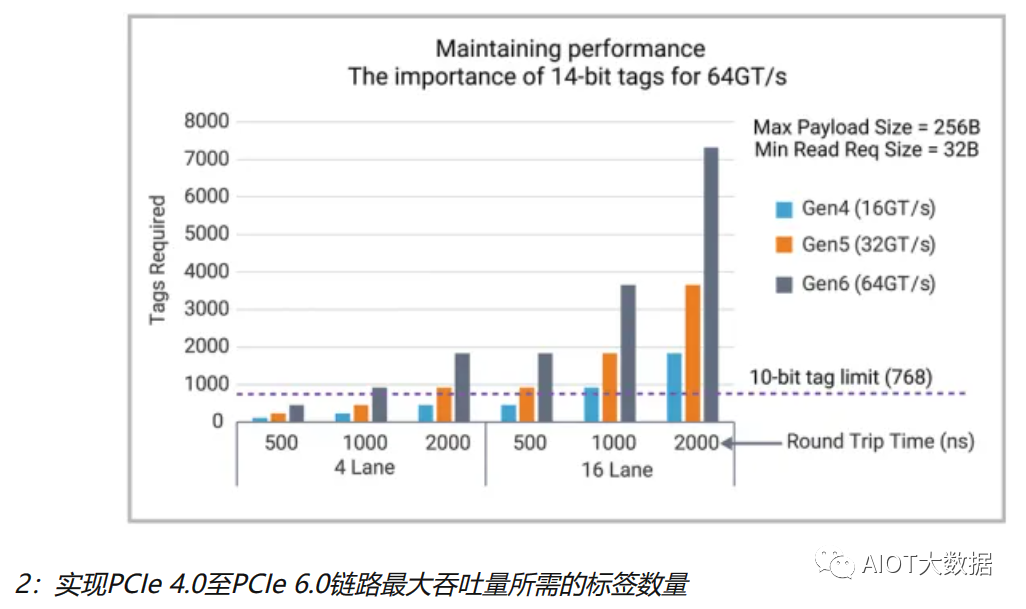

除了这三项变化之外,本文还将简要介绍其他一些新特性,例如旨在允许功率/带宽扩展的新的低功耗状态L0p,以及支持的标签数量从PCIe 5.0中的768个(10位标签)扩展到PCIe 6.0中的15,360个(14位标签)。

通道和PAM-4

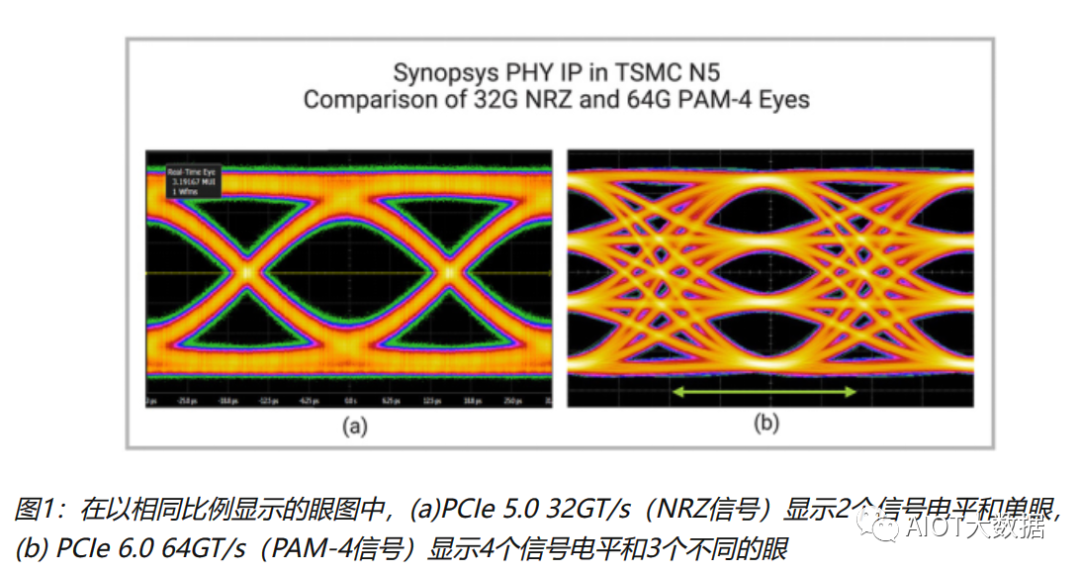

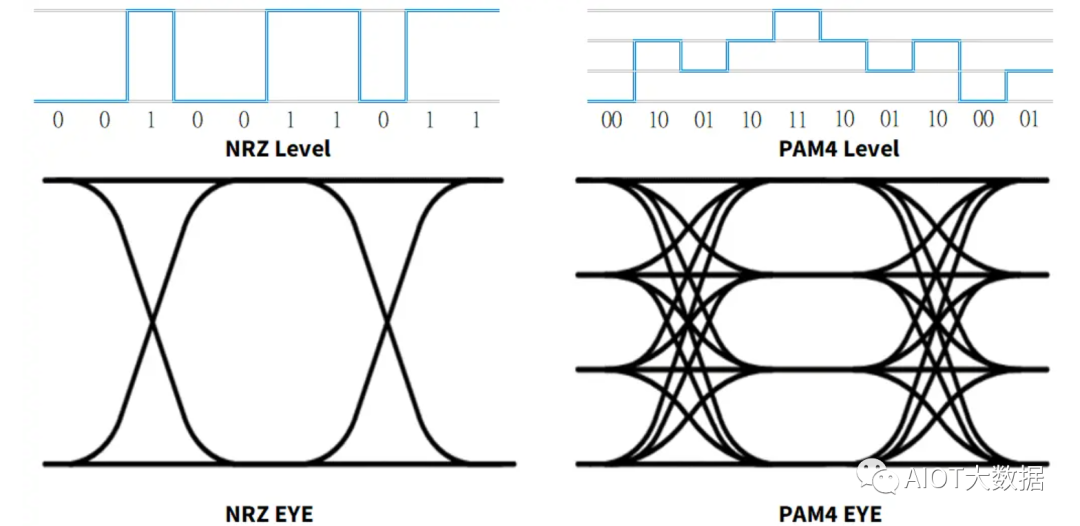

当数据速率从16GT/s加倍到32GT/s时,奈奎斯特频率也从8GHz加倍到16GHz,使得PCIe 5.0(第5代)的频率相关损耗比PCIe 4.0(第4代)严重得多。再加上电容耦合(噪声和串扰)的增加,使得PCIe 5.0通道成为最难处理的NRZ通道。如果PCIe 6.0仍然保留NRZ信号,则奈奎斯特频率将增加到32GHz,通道损耗大于60dB,这对于实际系统而言太大了,因此需要从NRZ更改为PAM-4信号。这一变化意味着发射和接收的信号现在有四个不同的电压电平,而不是两个,如图1所示。

图1(a)显示了使用NRZ信号的PCIe 5.0的眼图,包含两个电压电平和单眼。图(b)显示了使用PAM-4信号的PCIe 6.0的眼图,包含四个电压电平和三眼。图1中的两个信号具有相同的16GHz奈奎斯特频率和相同的单位间隔(UI)。这意味着他们基本上可以使用相同的PCIe 5.0通道,而不会让频率相关损耗变得更糟糕,如果使用64GT/s的NRZ信号,奈奎斯特频率为32GHz。这就是56G和112G以太网转换到PAM-4信号的原因,也是PCIe 6.0现在转换到PAM-4的原因,可以降低信号损耗。但是PAM-4的四个电压电平在一个UI中使用2bit编码,而NRZ是1bit编码,从而使数据速率提高了一倍。这听起来很棒,但是这里有一项重要的权衡因素。由于发射端(TX)的总体电压摆幅没有增加,因此PAM-4系统中每只眼的可用电压仅为NRZ的1/3。因此,信号在TX和接收端(RX)之间遇到的任何噪声都会对信号完整性造成更大的损害。

转变为PAM-4信号使得RX的工作更加困难,因为眼不仅在电压域要小得多(约 1/3),而且在时域也要小得多,而且这么多的转换必须嵌入同一个UI中。如图1 所示,这很明显。图1(b)底部的绿色箭头显示了NRZ眼的相对宽度,表明PAM-4 的眼宽度明显小于NRZ的眼宽度。因此,使用PAM-4时,时钟和数据恢复更加困难,需要更好的RX设计。PAM-4的大多数设计(包括即将推出的PCIe 6.0设计)将在RX中配置一个模数转换器(ADC),以更好地满足PAM-4的多电平信号需求以及对传统NRZ的支持。这意味着数字滤波是完全开放的,一个RX对另一个RX使用特定的数字信号处理(DSP)算法,再叠加针对不同通道的模拟和数字均衡的仔细平衡,将区分PHY性能。此外,更窄的PAM-4眼意味着PCIe 6.0上的TX抖动性能需要比PCIe 5.0上好2倍左右,开发者应该仔细考虑这些因素。

从NRZ信号转换为PAM-4信号还会显著影响封装和电路板设计,因为更改为四个电平信号会导致信噪比(SNR)立即退化9.6dB,因此正确管理噪声变得更加关键,即使奈奎斯特频率相同,封装和电路板设计中的串扰和回波损耗也比PCIe 5.0高。噪声敏感性增加意味着我们用于PCIe的1e-12误码率(BER)不可行,并且需要前向纠错 (FEC),因为PAM-4信令的BER将比1e-12高几个数量级,第一位误码率(FBER)的目标是1e-6。在其他标准(如以太网)中,使用强大的FEC来获得可接受的BER,但代价是带来100ns量级的大量额外延迟,这对PCIe来说是不可接受的。

由于FEC延迟和复杂性会随着需要纠正的符号数量的增加而增加,并且由于PCIe 6.0的延迟目标非常苛刻,因此使用了轻量级FEC,并与使用循环冗余码(CRC)检测错误的PCIe的重试能力相结合,以便数据包可以重新发送或重试。PCIe 6.0的轻量级FEC可以产生1e-6级的重试概率,并且与更强的CRC结合使用时,整个系统可以提供稳定、接近无误的性能,对往返时延的影响非常小(通常约为2纳秒)。这意味着开发者可以使用与PCIe 5.0基本相同的延迟预期进行设计,对于许多情况,例如大于128字节(32DW)的事务层数据包(TLP),相对于PCIe 5.0将获得显而易见的实际延迟改进。

FLIT

开发者需要考虑的另一个重要问题是转换到使用FLIT作为数据交换单元,而不是使用可变大小的TLP。由于PAM-4编码的更改和FEC需要将误码率提高到可接受的水平,因此这是必要的,这样CRC和重试机制可以让路给可接受的错误率和系统延迟。FEC仅适用于固定大小的数据包,因此PCIe 6.0采用了256字节FLIT作为标准大小的数据传输单元。为了保留现有通道的PCIe 5.0,需要对PAM-4进行更改,这需要添加FEC,相应地需要转换到FLIT。使用FLIT对系统有影响,因为一些FLIT可能有来自多个TLP的数据,而其他FLIT可能只包含TLP的一部分,并且底层TLP的大小仍可以在0到4096B(1024个DWORD)之间变化。

另一个影响是,一旦设备进入FLIT模式(例如,通过协商必须支持FLIT的PCIe 6.0链路进入),则无论链路质量有何变化,它都必须保持FLIT模式。因此,如果由于通道不稳定而需要降低链路速度,则新协商的较低数据速率将保持FLIT模式。这意味着在PCIe 6.0中,需要支持的所有可能的速度都有FLIT模式。

随着在PCIe 6.0中引入新的FLIT模式,TLP和数据层数据包(DLP)包头格式发生了变化,应用程序需要理解并正确处理这些变化。例如,对于PCIe 6.0,FLIT包含自己的CRC,因此数据链路层数据包(DLLP)和TLP不再需要像在PCIe 5.0和前几代中那样的单独CRC字节。此外,由于FLIT的大小固定,因此无需使用前几代(非FLIT模式)中的PHY层成帧令牌。与PCIe 5.0相比,这提高了带宽效率。

新的低功耗状态用于FLIT模式的L0p

PCIe 6.0引入了一种新的低功耗状态,称为L0p,允许PCIe 6.0链路在不中断数据流的情况下扩展带宽利用率,从而降低功耗。在前几代中,为了改变链路宽度,整个链路重新训练时,流量会中断几微秒,但L0p允许链路关闭通道,从而降低功耗,同时始终保持至少一个通道处于活动状态,即使其他通道正在进行链路训练。需要注意的是,这种新的低功耗模式仅在FLIT模式下可用,而L0s支持非FLIT模式。

这种新的低功耗模式是对称的,这意味着TX和RX一起缩放,并且支持FLIT模式的重定时器也支持这种模式。在处于L0p期间空闲通道的PHY功耗预计与关闭通道时的功耗相近。

PCIe 5.0~6.0相比PCIe 1.0~4.0速率高,SI、PI要求也有提高。电源方面,插卡最大功耗可提升至600W,将在6.0 CEM中更新;信号方面为保证信号完整性要求使用表贴连接器;互连通道方面,与PCIe 5.0类似,要求主板支持约12 inch,插卡支持约3-4 inch,可以想象下,如果PCIe 6.0仍旧采用NRZ调制格式,64GT/s速率奈奎斯特频点在32GHz,那么通道IL将小于-60dB(参考下图通道仿真结果),很难通过现有技术实现该信号的高频补偿,考虑实现成本和技术复杂度,采用高阶调制PAM4是种不错选择,相比PCIe 5.0奈奎斯特频率不变,当前可用板材下可传输相似距离。

在64GT/s下保持性能

为了在PCIe系统中实现最佳性能,开发者需要确定系统必须处理的未发布请求(NPR)的最大数量,以保持数据畅通,这取决于有效负载大小以及总往返时间(RTT)。该数量转换为可用标签的数量,并且是必须根据系统需求正确设置的控制器属性。对于PCIe 6.0,随着数据速率再增加一倍,以前的768个标签限制已经远远不够,因此标签数量最大值急剧增加,变为基于14位的15,360个标签。这样即使在往返时间较长的情况下也可以实现高效的性能,并且具有很大的余量,可以在将来实现更快的数据速率。

图2显示了各种RTT的PCIe 4.0、5.0和6.0数据速率所需的标签数量,以保持256B 有效负载和32B最小读请求大小的最大吞吐量。如图2所示,PCIe 5.0的768个标签限制远远不足以支持大多数PCIe 6.0系统的性能。这应该在作为系统片上(SoC)设计的一部分的PCIe 6.0控制器的配置过程中进行仿真和验证,以确保能够实现预期的性能。

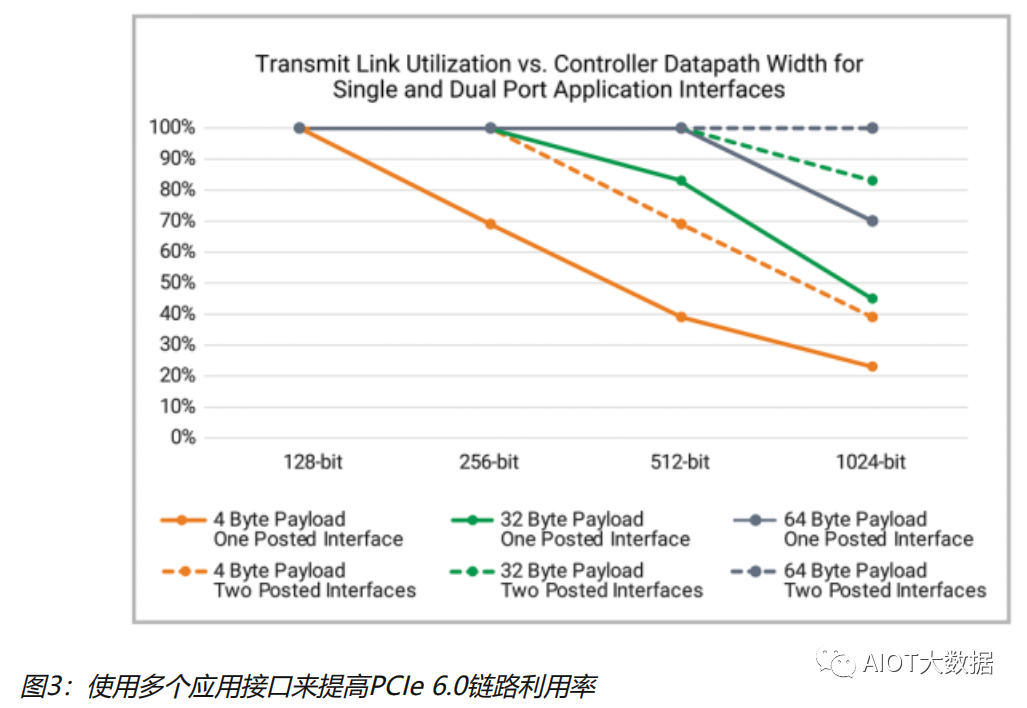

要考虑的第二个因素是如何确保应用能够有效地利用PCIe 6.0的大量可用带宽。通常,应用程序通过带有3个独立接口的控制器连接到PCIe:分别用于已发布、未发布和已完成事务。对于64GT/s PCIe 6.0,各种情况的分析表明,使用单个接口将导致链路利用率或带宽效率(实现的带宽相对于理论带宽)的显著损失。对于较小的数据路径宽度和较小的负载大小,此问题最为严重。

如图3所示,对于传统的单应用接口和双应用接口(用于已发布事务),PCIe 6.0 在各种数据路径宽度和有效负载大小下的传输链路利用率。在1024b数据路径的32字节有效负载的情况下,使用单个已发布接口而不是两个接口导致链路利用率下降54%。这意味着在这种情况下,使用带有单个应用接口的控制器将获得相当于PCIe 5.0的性能。

PHY和控制器集成

为了实现最佳性能、最低延迟和简化集成,通过单一供应商来实现PHY和控制器IP的完整解决方案是有利的。如果这不可能,PIPE接口的细节就比较关键。PIPE 5.x 接口规范不支持PCIe 6.0,因此必须指定较新的版本PIPE 6.0。现在看来,PCIe6.0 的大多数设计将采用基于新PIPE 6.0规范的SerDes架构PIPE接口。这简化了PHY 设计,还使PCIe 6.0PHY在推出时能够支持CXL 3.0的低延迟要求。

在PCIe 6.0中,仍然需要权衡数据路径位宽和PIPE接口处时序能够收敛的频率。对于要求最大的PCIe 6.0带宽和16通道配置的应用,只有两个可行的选择。为了使时序能够收敛在1GHz,需要使用64b PIPE,这又需要1024b PCIe 6.0控制器架(16 通道x64b=1024b)。这是PCIe 6.0的一个新特性,因为前代PCIe没有1024位架构可用。

另一个选择是使用32位PIPE并坚持使用512位架构。这意味着在PHY控制器接口上以2GHz来收敛时序。虽然大多数SoC开发者不太可能首选这种架构,但如果开发者想要在非常快的CMOS过程中实现最小的延迟,那他们就有可能会这么选择,因为将bit时钟的周期时间减半,可以提供比1GHz时序更小的延迟。

测试和调试注意事项

对于量产设备,64GT/s速率的生产测试需要能够验证链路的快速测试,此类测试通常使用内置环回模式、数据图形发生器和接收器(集成在PHY和控制器IP中)。在PHY中支持PAM-4的环回比NRZ更复杂,但很重要,应将其视为可测试性解决方案的一部分。

对于实际硅片中的调试和质量监测,能够监测硅片中的FBER对于一个系统的实际链路质量也非常有益。可以与内置scope功能结合使用,通常合并入PCIe 6.0 PHYIP,以获得对TX和RX之间更详细的理解。

像PCIe 6.0这样的新规范需要进行更鲁棒的系统测试,针对调试、错误注入和统计监测功能提供内置控制器支持非常重要。这有助于不确定是否能够正确地开发固件和软件,以预测可能遇到的任何潜在的实际系统问题。

PCIe 6.0先行者——固态存储

要实现这种未来科技,增加数据带宽非常重要。带宽也就是单位时间内网络从某一点到另一点所能通过的”最高数据率”,常用的单位是bps,即每秒多少比特。随着高性能计算(HPC)、超大规模数据中心、人工智能/机器学习(AI/ML)、自动驾驶、物联网(IoT)等领域对先进应用的需求不断增加,带宽需求曲线依旧呈现不断上扬的趋势。

新的PCI Express (PCIe )6.0规范正是一种能够辅助开发者们实现未来科技的关键技术。PCIe 6.0堪称是迄今为止最重要的PCIe协议创新。

PCle 6.0是如何实现带宽飞跃的?

PCIe 6.0的带宽是上一代的2倍,具有以下特性:

每个引脚的数据传输速率可高达64GT/s

通过新的低功耗状态提高电源效率

经济高效的性能

高性能的数据加密与完整性

向后兼容之前的版本

PCIe 6.0实现带宽飞跃的一种方式就是改变电气信号调制方案,即从传统的不归零(NRZ)信号转变为使用脉冲幅度调制技术的四电压电平(PAM-4)信号。

在前几代PCIe中,NRZ位在每个单位时间间隔(UI)中是以1或0的形式串行传输的。而采用PAM-4时,则可以在与NRZ相同的单位间隔中获得四个值。由此,无需让信号速率加倍,即可实现数据速率翻倍。四个电压电平将生成三个眼图,而眼图高度和眼图宽度则有所减小。为了减少信号中的错误,PCIe采用了格雷编码,即一次只改变一位。对于模拟信号,预编码有助于减少错误。而对于数字信号,前向纠错(Forward Error Correction)可降低误码率。

但是,这样难道不会显著增加延迟吗?

并不会。因为PCI-SIG提出了一种简洁的方式来实现轻量级FEC,它利用了现有的重试机制,因此不会导致延迟问题。

与PCIe 5.0相比,PCIe 6.0可提供更高的带宽(2x),但由此增加的延迟却几乎为零。

流量控制单元很重要

在PCIe 6.0中,事务传输层概念(the transaction layer concepts)使用了与前几代相同的命令。新的包头格式虽然在根本上与前几代并无不同,但组织结构却更为精简。新的包传送方法让协议彻底重组,这种重组不仅支持更高的带宽,系统还可以通过共享流量控制授权等功能对带宽进行处理。

PCIe 6.0使用流量控制单元(FLIT)来传输数据,无需编码。以2.5G为例,由于编码的原因,8位数据在线路上会变成10位。对于8G而言,128位数据在线路上会变成130位。另一方面,FLIT完全无需进行编码。这意味着每个1位数据在线路上也是1位。因此,PCIe 5.0中通过编码执行的功能和特性,在PCIe 6.0中将由于扰码多项式以及 FLIT 包头的更改而被涵盖。

PCle 6.0通道可进入“睡眠”

PCIe 6.0所需的低功耗状态是新的L0p,虽然L0p可以向后兼容前几代的L0s,但64GT/s的FLIT模式速率还是要求使用 L0p。这种新的低功耗状态的创新之处在于,一些通道可以进入睡眠状态(相当于电气闲置),而数据可以继续在非闲置通道上进行传输。要支持L0p,还需要支持FLIT模式的重定时器。L0p的优势在于开发者可以根据实际使用的带宽来扩展电源。

保护数据和系统的安全

互联程度越来越高,数据和系统漏洞的攻击面就越大,攻击者的动机现在也越来越难以揣测。正因如此,越来越多的法律法规还要求电子系统具有更高的安全性。在此背景下,PCIe 6.0采用了数据完整性和安全保护机制,其在安全方面的亮点主要体现在以下三个方面:

数据对象交换(DOE)

这不是一种性能模式,而是一种安全模式,也并非出于高性能目的,这是一个PCIe用于增强其他领域安全性的低级别构建模块。DOE是一种基于配置空间寄存器来传输主要加密数据和密钥的简单机制,它与应用逻辑紧密结合。

组件测量和认证(CMA)

借助此安全功能,设备中的固件可为设备提供加密签名。收到CMA报告时,开发者可以验证签名是否准确。如果不准确,他们就需要解决相应的安全问题。

完整性和数据加密(IDE)

这一安全措施主要是为了防止物理访问攻击。这项保护是为了防止有人嗅探PCIe 6.0 FLIT数据包,并对数据包进行插入和删除操作。这一安全保护机制有两种模式:第一种是Link IDE,相应的数据将在发送端加密,然后在直连设备的接收端解密。第二种是选择性IDE,相应的数据包将通过交换机传输,在请求者那里加密,并经过若干中间设备中转后在请求完成时解密。由于这种安全模式作用于PCIe的“核心”数据包级别,因此它需要与控制器紧密结合,以便以64GT/s的速率高效地实现加密和解密功能,同时将延迟影响降至最低。此外,开发者还需要有多个管道化AES-GCM加密引擎来满足吞吐量要求。

PCIe 5.0与PCIe 6.0在安全特性方面的主要区别在于带宽扩展、对FLIT模式的支持,以及对新包头格式的支持上。另外还有一些安全特性即将推出,它们将同时支持PCIe 5.0和PCIe 6.0。可以这么说,随着安全形势的变化,安全防护措施也会不断发展和完善。

PCle 6.0先行者:固态硬盘

虽然PCIe 4.0和PCIe 5.0正在普及,但固态硬盘(SSD)已经开始率先采用PCIe 6.0。

▲ PCIe是超大规模数据中心机架单元盒中的实际接口。这是一个盒内(计算)的示例:PCIe 是CPU、GPU、SSD、加速器和智能NIC应用的主要接口,并通过CXL保持缓存一致性。

以上图为例,仔细观察图中机架单元的盒内结构,就会发现CPU与加速器及SSD相连,而加速器与智能网卡(NIC)相连,这些都属于PCIe插槽。在从PCIe 5.0过渡到PCIe 6.0时,U.2外形尺寸将逐步被淘汰,PCIe 6.0很可能支持U.3、EDSFF(企业和数据中心标准外形尺寸)和OCP(开放计算项目)3.0。

由于SSD SoC与NVMe(非易失性内存主机控制器接口规范)或闪存以及根联合体处理器相连,因此带宽要求会非常高。但SSD会受限于SSD插槽的带宽,而后者又受PCIe数据速率控制,这意味着SSD在同一通道下可获得双倍带宽,而这也是SSD率先采用PCIe 6.0的原因所在,对于开拓市场,优势很明显。同时,面向根联合体处理器的生态系统也已成形。

在Meta的推动下,开放计算项目(OCP)正在开发一种可用于所有接口的通用外形尺寸。NIC、SSD及其他组件一直都有自己的外形尺寸,而OCP的愿景就是让所有这些接口都使用一种通用外形尺寸。参与Meta生态系统的公司正在开发采用OCP 3.0外形尺寸的设备,而PCIe 6.0将会支持该外形尺寸。

-

AI

+关注

关注

87文章

30736浏览量

268896 -

PCIe

+关注

关注

15文章

1234浏览量

82586 -

人工智能

+关注

关注

1791文章

47186浏览量

238267

原文标题:技术前沿:PCIe6.0助力AI人工智能应用

文章出处:【微信号:AIOT大数据,微信公众号:AIOT大数据】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

PCIe6.0助力AI人工智能应用

PCIe6.0助力AI人工智能应用

评论