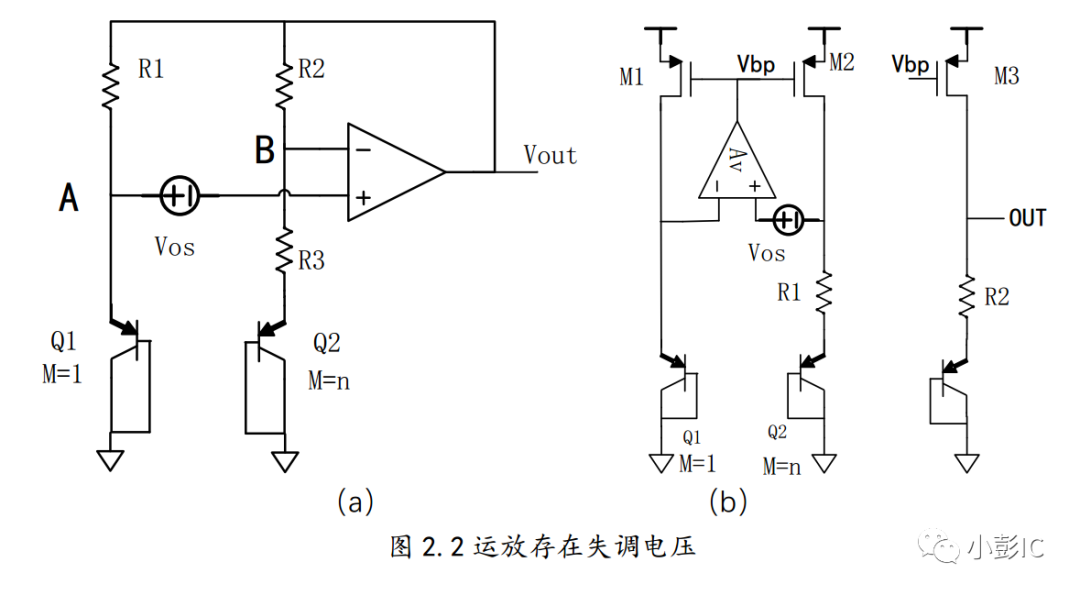

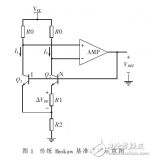

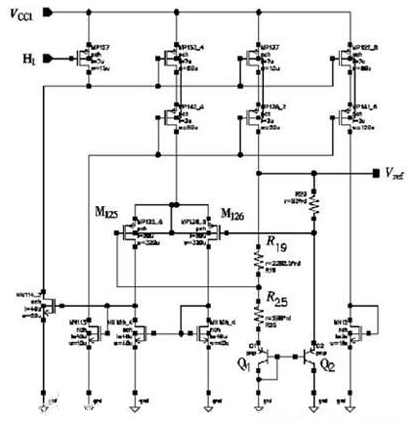

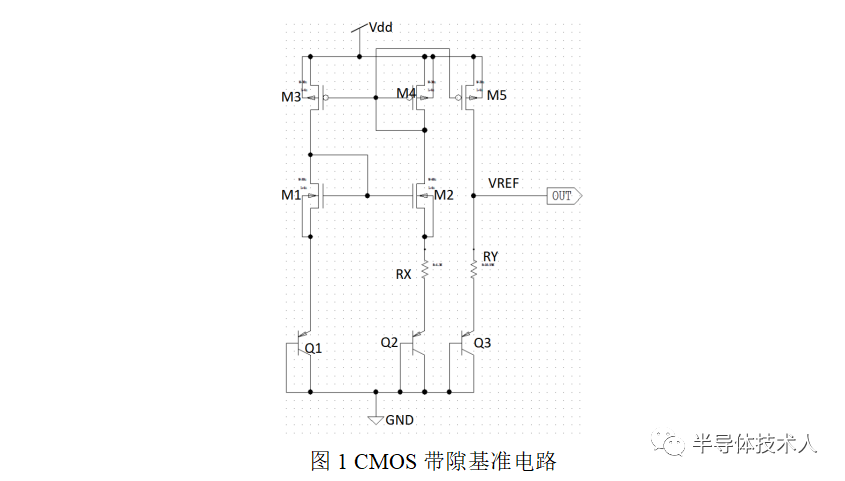

如图2.2(a)是两种常见的bg结构,对于这两个bg模块的输出电压误差来源:

- 60%来自于运放的offset

- 30%来自于prosess

- 10%来自于mismatch(对于2.2(a)是R1和R2、2.2(b)指的是M1和M2)

以上为其电路设计师的经验数据,仅供参考。

EA的offset是影响bg误差的主要因素,本文只计算EA的offset对bg的影响

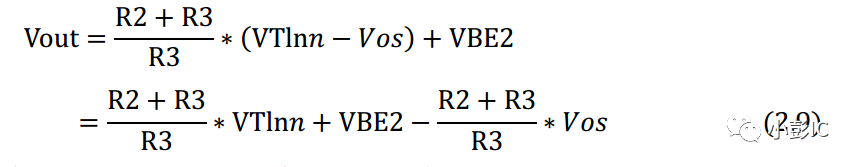

对于图 2.2(a)(忽略失调电压给两个三极管造成的电流误差)

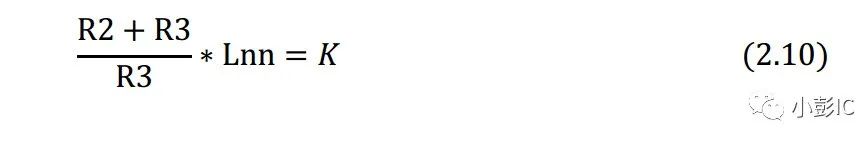

假设 VBE 的温度系数绝对值是 VT 温度系数的 K 倍,也就是

式2.9就可以表示成:

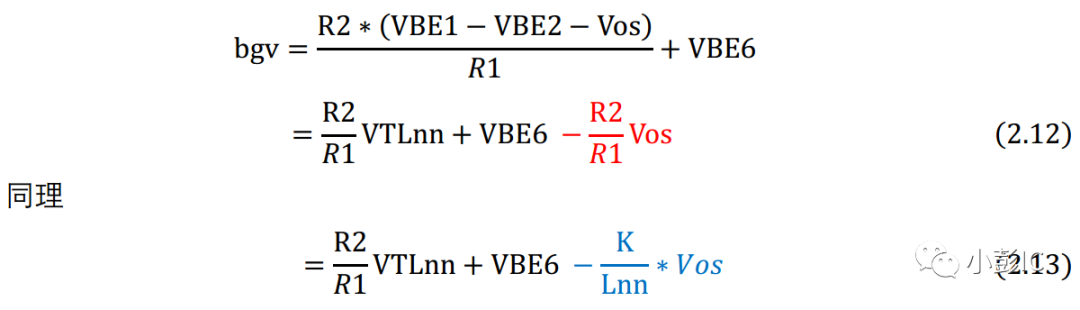

对于图 2.2(b)(忽略M1和M2电流镜的电流误差)

根据2.13和式2.11,可以得到结论(实际上是片面结论):

同样的EAoffset,对bg的输出电压影响一样(实际上是错误的)

下面来分析并通过仿真证明错误的

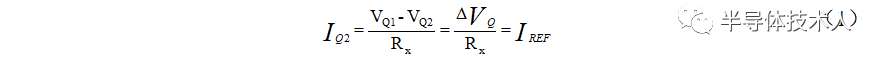

由于本系列文章没有分析bg的工作原理所以在这里补充(如有需要欢迎留 言):

bandgap电路的两个主要前提条件是

- 两个pnp的电流完全相同

- 运放的输入两点也就是(a)图的A点和B点电压完全相同

对于(a)(b)两幅图

如果不考虑每路电流的失配, 运放失调电压的影响对于以上两种拓扑结构的影响是一样的,如果考虑电流失配呢?直观感受是 (a)图的运放除了运放的角色,还担任电流镜的角色,所以(a)图的运放失配还会影响 BG 的温度曲线。

仿真电路以及仿真结果:

在没有手动加入失调电压Vos的时候,设置好两幅图的其他工作条件相同(工作点、系统误差、pnp个数以及比例、并设置好电阻比例)

图(a)

仿真结果

如果不考虑电流的失配,两种结构运放的 Vos 对 bgv 的影响一样,已经通过计算证明。但要考虑图 2.2(a)Vos 引起的电流失配, Vos 还会影响 bgv 的温度曲线,如图2.3 红色的曲线,可知 2.2(a) Vos 对的 bgv 的影响较大,也会改变 bg 的温度曲线。

失调电压结论 :

图 2.2(b) Vos 只对 bgv 的值有影响,没有影响 bgv 的温度曲线的形状,图 2.2(b), 不仅对 bgv 的值有影响,也影响了 bgv 的温度曲线形状。

-

三极管

+关注

关注

143文章

3633浏览量

122872 -

电流镜

+关注

关注

0文章

44浏览量

17380 -

输出电压

+关注

关注

2文章

1182浏览量

38545 -

带隙基准电路

+关注

关注

0文章

14浏览量

10771 -

PNP管

+关注

关注

1文章

28浏览量

7621

发布评论请先 登录

相关推荐

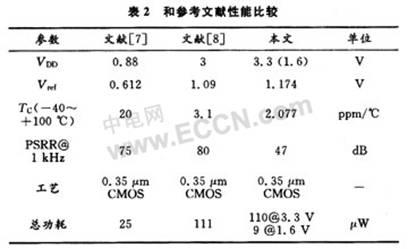

低温漂CMOS带隙基准电压源分析

14位Pipeline ADC设计的带隙电压基准源技术

CMOS带隙基准电压源曲率校正方法

带隙电压基准源的设计与分析

带隙基准电压模块之EA offset影响分析

带隙基准电压模块之EA offset影响分析

评论