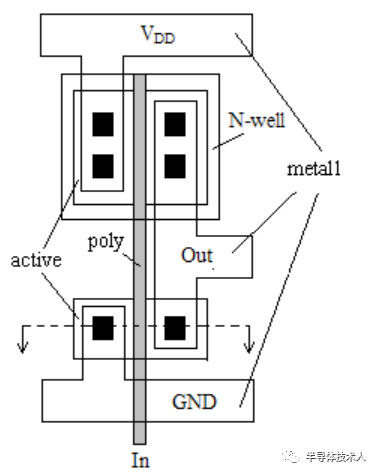

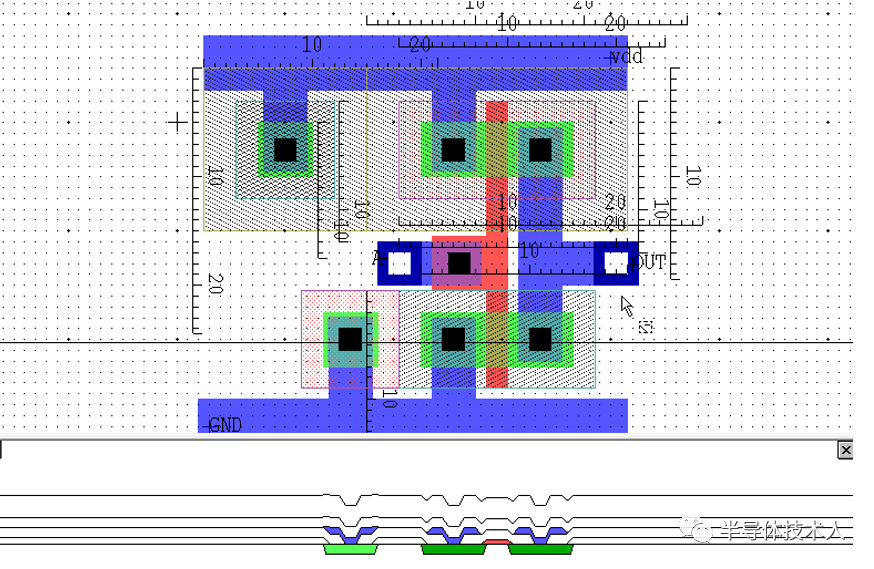

1 下图为一个采用N阱CMOS工艺的版图。

(1)从版图中提取逻辑图。

(2)此版图中应用了哪几种类型的设计规则?

设计规则:最小宽度,最小间距,最小包围,最小延伸。

(3)画出虚线处的剖面图,并在图中标出场氧和栅氧的位置。

CMOS工艺是在PMOS和NMOS工艺基础上发展起来的。CMOS中的C表示“互补”,即将NMOS器件和PMOS器件同时制作在同一硅衬底上,制作CMOS集成电路。CMOS集成电路具有功耗低、速度快、抗干扰能力强、集成度高等众多优点。CMOS工艺已成为当前大规模集成电路的主流工艺技术,绝大部分集成电路都是用CMOS工艺制造的。

CMOS中既包含NMOS晶体管也包含PMOS晶体管,NMOS晶体管是做在P型硅衬底上的,而PMOS晶体管是做在N型硅衬底上的,要将两种晶体管都做在同一个硅衬底上,就需要在硅衬底上制作一块反型区域,该区域被称为“阱”。根据阱的不同,CMOS工艺分为P阱CMOS工艺、N阱CMOS工艺以及双阱CMOS工艺。其中N阱CMOS工艺由于工艺简单、电路性能较P阱CMOS工艺更优,从而获得广泛的应用。

-

集成电路

+关注

关注

5381文章

11381浏览量

360842 -

晶体管

+关注

关注

77文章

9633浏览量

137834 -

CMOS工艺

+关注

关注

1文章

58浏览量

15663 -

NMOS管

+关注

关注

2文章

120浏览量

5395 -

PMOS管

+关注

关注

0文章

82浏览量

6612

发布评论请先 登录

相关推荐

13um应变补偿多量子阱SLD台面制作工艺的研究

版图设计工程师-上海

版图设计工程师-上海

版图设计工程师-上海

版图设计-上海

高薪诚聘IC版图工程师

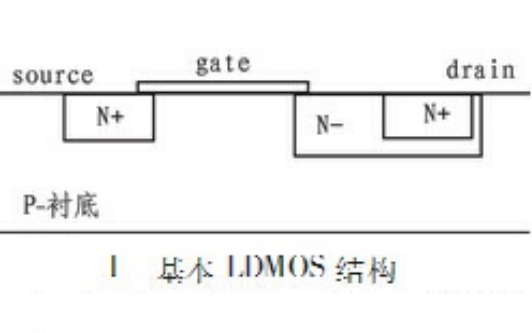

如何使用深阱工艺提高LDMOS的抗击穿能力

模块工艺——双阱工艺(Twin-well or Dual-Well)

基于CMOS工艺的RS422全工收发器芯片的原理及其电路版图设计

双阱工艺的制造过程

N阱CMOS工艺版图

N阱CMOS工艺版图

评论