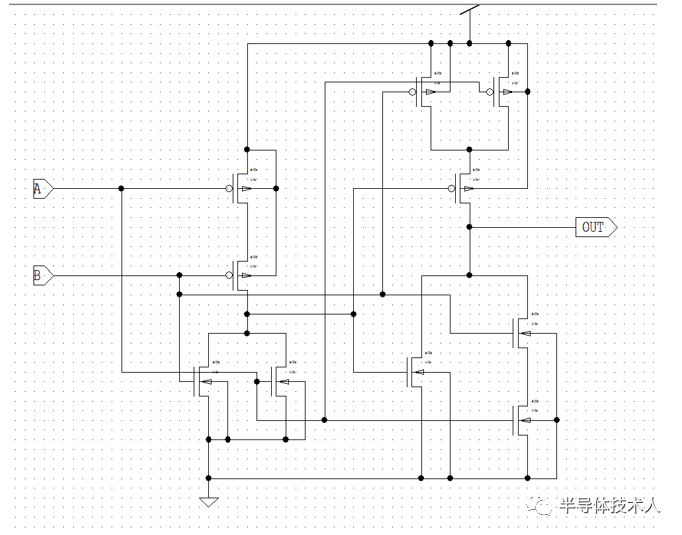

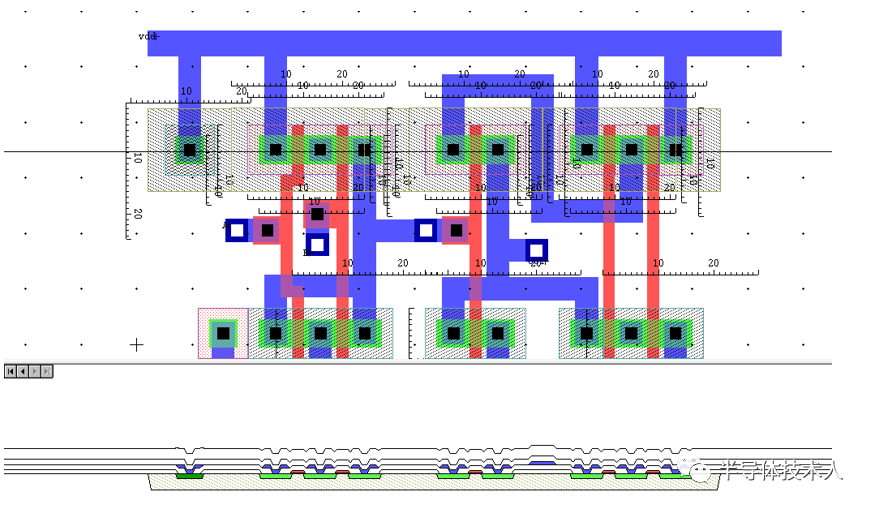

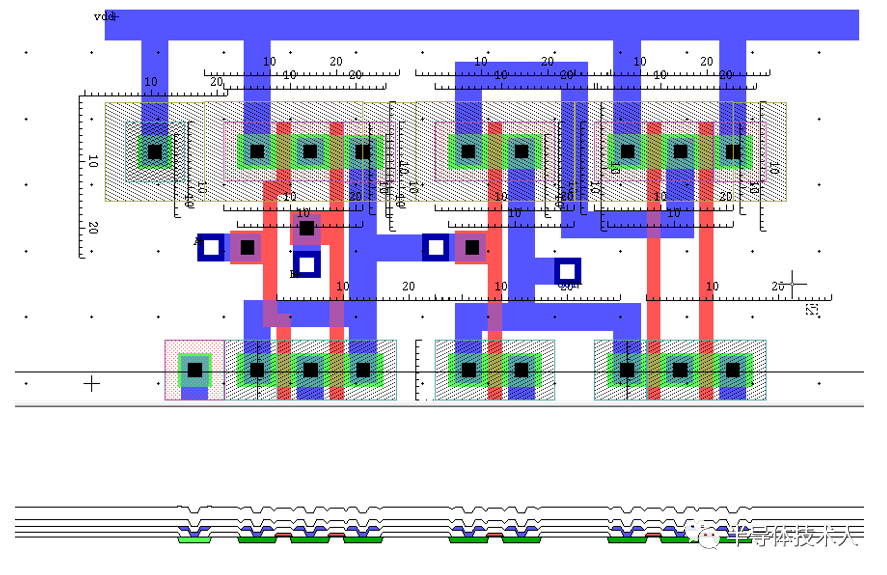

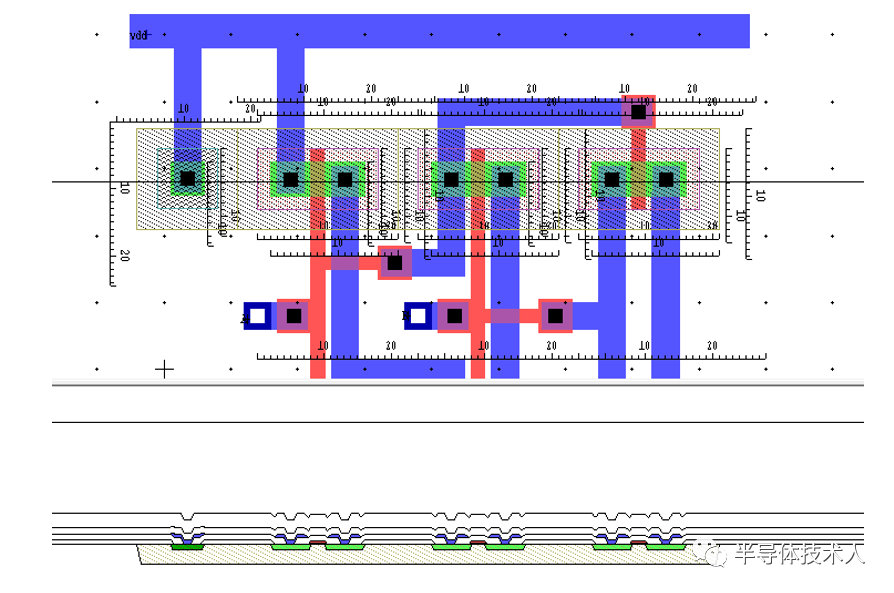

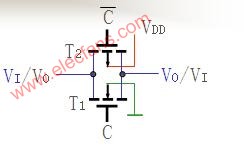

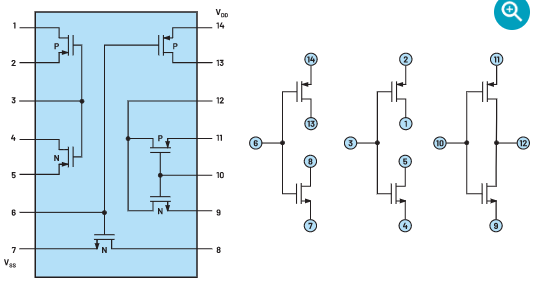

1、用CMOS传输门实现一个异或门电路。

(1)

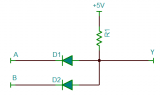

(2)

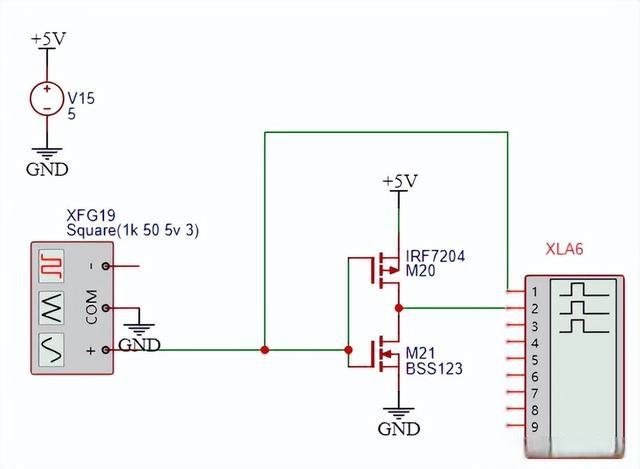

2、用CMOS传输门实现一个双路开关电路,在电路上标明输入端和输出端,并写出输出的逻辑表达式。

3、说明采用CMOS传输门比采用单独的PMOS管或NMOS管的优势是什么?

利用PMOS管对高电平的传输性能好,而NMOS管对低电平的传输性能好,从而使信号可以获得全摆幅的传送而没有电平损失。

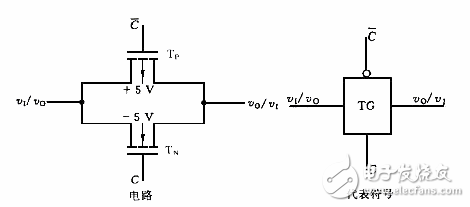

CMOS传输门:

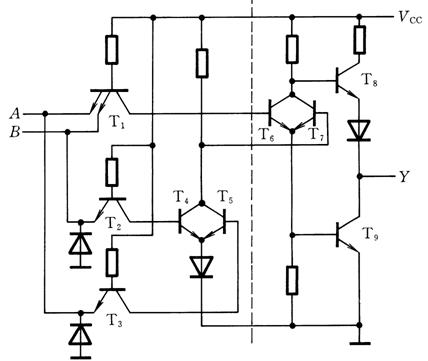

CMOS传输门(Transmission Gate)是一种既可以传送数字信号又可以传输模拟信号的可控开关电路。CMOS传输门由一个PMOS和一个NMOS管并联构成,其具有很低的导通电阻(几百欧)和很高的截止电阻(大于10^9欧)。

TP和TN是结构对称的器件,它们的漏极和源极是可互换的。设它们的开启电压|VT|=2V且输入模拟信号的变化范围为-5V到+5V。

为使衬底与漏源极之间的PN结任何时刻都不致正偏,故TP的衬底接+5V电压,而TN的衬底接-5V电压。两管的栅极由互补的信号电压(+5V和-5V)来控制,分别用C和!C表示。传输门的工作情况如下:当C端接低电压-5V时TN的栅压即为-5V,vI取-5V到+5V范围内的任意值时,TN不导通。同时、TP的栅压为+5V,TP亦不导通。可见,当C端接低电压时,开关是断开的。

为使开关接通,可将C端接高电压+5V。此时TN的栅压为+5V,vI在-5V到+3V的范围内,TN导通。同时TP的棚压为-5V,vI在-3V到+5V的范围内TP将导通。由上分析可知,当vI<-3V时,仅有TN导通,而当vI>+3V时,仅有TP导通当vI在-3V到+3V的范围内,TN和TP两管均导通。

进一步分析还可看到,一管导通的程度愈深,另一管的导通程度则相应地减小。当一管的导通电阻减小,则另一管的导通电阻就增加。由于两管系并联运行,可近似地认为开关的导通电阻近似为一常数。

-

CMOS

+关注

关注

58文章

5746浏览量

236186 -

门电路

+关注

关注

7文章

199浏览量

40274 -

模拟器

+关注

关注

2文章

884浏览量

43449 -

NMOS管

+关注

关注

2文章

121浏览量

5560 -

PMOS管

+关注

关注

0文章

84浏览量

6741

发布评论请先 登录

相关推荐

用CMOS传输门实现一个异或门电路

用CMOS传输门实现一个异或门电路

评论