摘要

在涉及射频(RF)的硬件测试中,选择可配置、已校准的可靠信号源是其中最重要的方面之一。本文提供了基于Raspberry Pi的高度集成解决方案,其可用于合成RF信号发生器,输出DC至5.5 GHz的单一频率信号,输出功率范围为0 dBm至-40 dBm。所提出的系统基于直接数字频率合成(DDS)架构,并对其输出功率与频率特性进行了校准,可确保在整个工作频率范围中,输出功率保持在所需功率水平的±0.5 dB以内。

简介

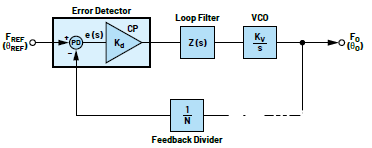

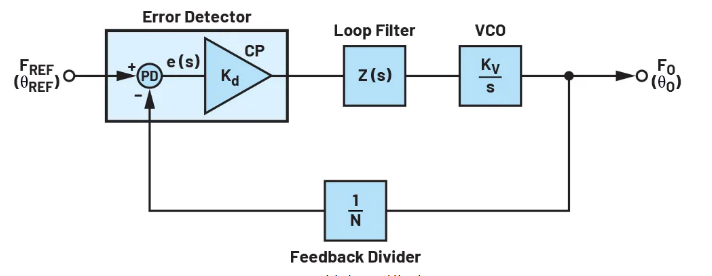

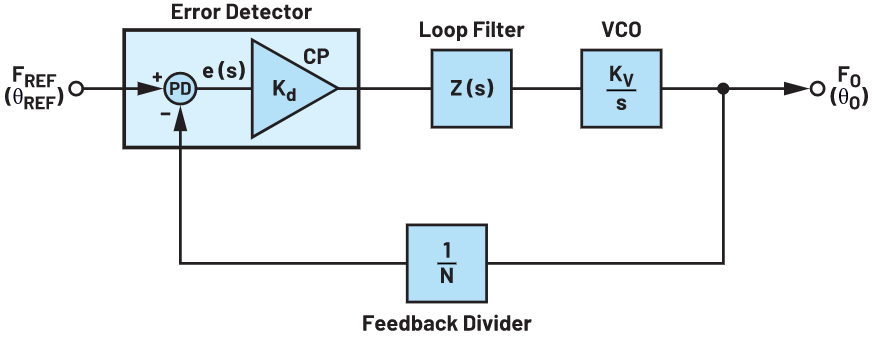

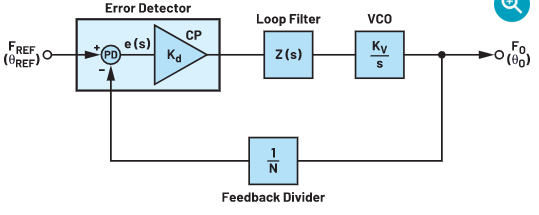

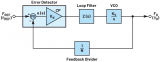

RF信号发生器,尤其是微波频率的RF信号发生器,以前通常是基于锁相环(PLL)频率合成器1来构建。PLL支持从低频参考信号生成稳定的高频信号。图1显示了一个基本PLL模型。该模型由反馈系统(其中包括一个包括一个电压控制振荡器(VCO)用于改变输出频率)、误差检测器(用于比较输入参考频率和输出频率)以及分频器组成。当分频器的输出频率和相位等于输入参考的频率和相位时,环路被认为处于锁定状态。2–5

图1.基本PLL模型

根据应用的不同,DDS架构作为频率合成器可能比PLL提供了一种更好的替代方案。。图2显示了一个典型的基于DDS的信号发生器。调谐字应用于相位累加器,由后者确定输出斜坡的斜率。累加器的高位经过幅度正弦转换器,最终到达DAC。与PLL相比,DDS的架构具有明显的优势。例如,DDS数字相位累加器可实现比基于PLL的频率合成器更精细的输出频率调谐分辨率。

图2.基于DDS的典型信号发生器

PLL切换时间是其反馈环路建立时间和VCO响应时间的函数,由于自身性质的限制,其速度较慢,而DDS仅受数字处理延迟的限制,因此具有更快的切换速度。在电路板尺寸方面,DDS的面积更小,便于系统设计,许多硬件RF设计难题也迎刃而解6。

下一部分将讨论CN0511。一款基于DDS架构的完整DC至5.5 GHz正弦波信号发生器的总体系统设计。接下来将讨论矢量信号发生器架构及其规格。而后将重点讨论系统时钟,包括时钟参考要求以及时钟管理单元和矢量信号发生器之间的电路连接。也会涉及电源架构和系统布局,并进一步说明整体系统如何实现高功率效率和合理的散热性能。随后的“软件架构和校准”部分将围绕系统软件控制和校准展开讨论。该部分将解释软件提供的灵活控制以及如何校准输出功率。最后一部分将说明整体系统性能,包括系统相位噪声、校准输出功率和系统的热性能。

系统级架构和设计考量

A:系统级设计

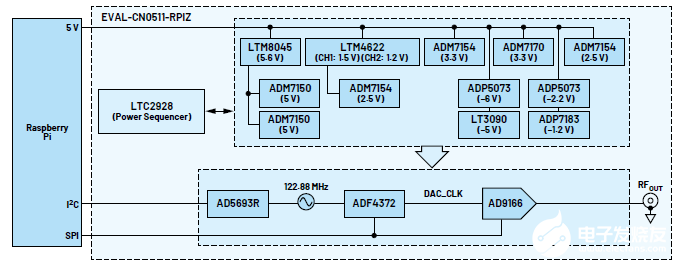

图3所示系统是基于DDS架构的完整DC至5.5 GHz正弦波信号发生器。四开关DAC核心和集成输出放大器在整个工作频率范围内提供极低的失真,并配有50Ω的输出匹配终端。

板载时钟解决方案包括参考振荡器和PLL,因而无需外部时钟源。所有电源均来自Raspberry Pi平台板,其具有超高电源抑制比(PSRR)稳压器和无源滤波功能,可使大幅减小电源转换器对RF性能的影响。

图3.CN0511:基于RPI的频率合成RF信号发生器

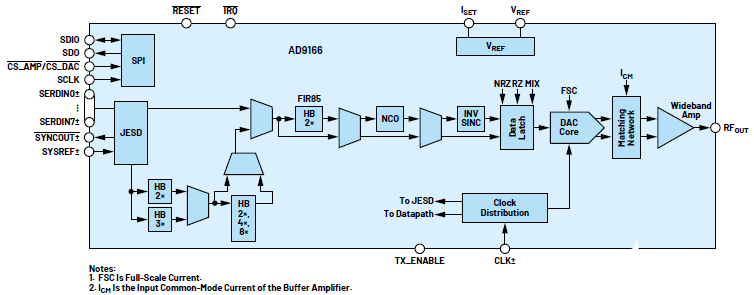

图4.所用矢量信号发生器(AD9166)的功能框图

图5.ADF4372 RF8x输出级

图3所示架构可用于雷达、自动测试、任意波形发生器和单音信号发生器等各种应用。而本文中实现了单音信号发生器应用。以下小节将讨论CN0511包含的主要集成器件。

B:矢量信号发生器

如图4所示,所使用的DC至9 GHz矢量信号发生器包含一个6 GSPS(1倍不归零模式)DAC、8通道、12.5 Gbps JESD204B数据接口以及一个具有多个数控振荡器(NCO)的DDS。同时该器件是高度可配置的数字数据路径,包括插值滤波器、反SINC补偿和数字混频器,支持灵活的频谱规划。

图4所示系统利用DAC的48位可编程模数NCO以非常高的精度(43 μHz频率分辨率)实现了信号的数字频移。该DAC的NCO仅需要SPI写入接口速度达到100 MHz即可快速更新频率调谐字(FTW)。SPI还支持配置和监控该DAC中的各种功能模块。本设计未使用JESD通道,器件仅在NCO模式下使用。

图4中的矢量信号发生器集成了单端、50 Ω匹配的输出RF放大器,因此无需采用复杂的RF输出电路接口。表1显示了AD9166的主要规格和在各种条件下的性能。

表1.AD9166主要规格

| 参数 | 值 | 条件 |

| 频带平坦度 | DC至9 GHz | |

| SFDR | –83 dBc | 51 MHz信号音 |

| -66 dBc | 451 MHz信号音 | |

| -38 dBc | 4051 MHz信号音 | |

| 功耗 | ~4 W | 5000 MHz信号音 |

| 相位噪声 | -134.8 dBc/Hz | 3600 MHz信号音;10 kHz偏移 |

| 封装 |

324引脚BGA (15 mm × 15 mm) |

C:系统时钟

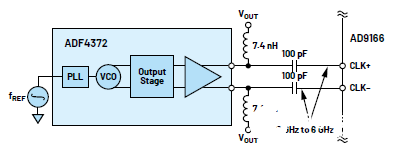

图2中的系统使用了ADF4372 PLL(见图5),这是一款集成VCO的宽带频率合成器,当与外部环路滤波器和外部参考频率一起使用时,可以作为小数N分频或整数N分频频率合成器。此外,VCO频率可进行1、2、4、8、16、32或64分频,因此用户可以在RF8x产生低至62.5 MHz的RF输出频率。

时钟源的质量(例如其相位噪声和杂散特性)以及其与高速DAC时钟输入的接口,会直接影响交流性能。因此,相位噪声和其他频谱内容将会被直接调制到输出信号上。为实现最佳整数边界杂散和相位噪声性能,ADF4372使用了单端参考输入信号,然后将其倍频以产生用于高速DAC的时钟,如图6所示。

图6.ADF4372和AD9166之间的电路连接

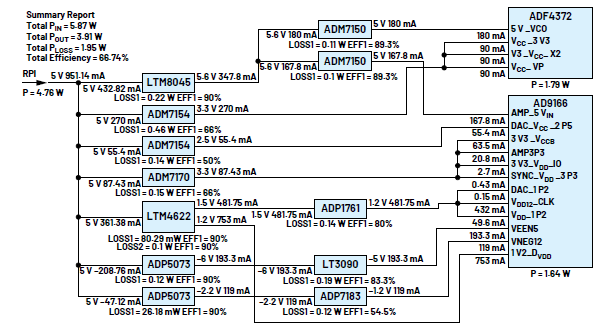

D:电源架构

CN0511的系统电源树如图7所示,基于系统负载要求将其效率提高到90%,分别使用了LTM8045、LTM4622和ADP5073开关稳压器,。并选用ADM7150、ADM7154和ADP1761等低压差线性稳压器(LDO)来为DAC、放大器、PLL和VCO供电,其有超低噪声和高PSRR性能,可实现最佳相位噪声性能。

使用电源时序控制器LTC2928来确保高速DAC按正确顺序上电,避免损坏其内部电路。该电源时序控制器IC可监测和管理四个电压轨,并具有控制各电压轨的上电时间和其他监控功能,其中包括欠压和过压监控与报告功能。

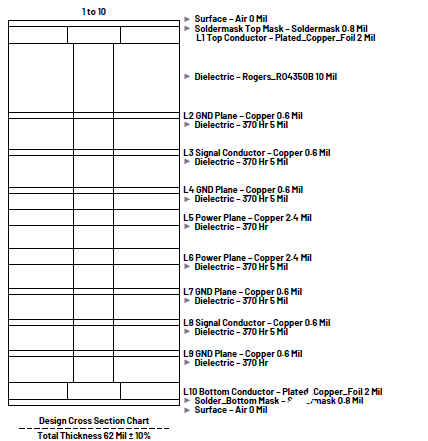

E:布局考虑

对于这种需要极高性能和较高输出频率的应用,PCB(印刷电路板)材料的选择会对结果有很大影响。图8显示了推荐的CN0511 PCB叠层,它在包含RF走线的层上使用Rogers 4350电介质材料,最大程度上减少3GHz以上的信号衰减,并确保在RF输出处获得最佳的信号完整性。

图8.推荐的PCB横截面和叠层

热性能与PCB设计和工作环境直接相关。为改善设计的散热性能,在PCB散热焊盘上打了散热通孔。

图7.系统电源树

软件架构和校准

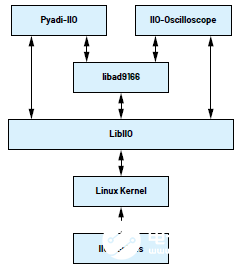

A:软件控制

在任何涉及信号发生器的应用都希望能够轻松灵活地控制仪器设备。因为它只需要将一张带有Kuiper Linux镜像的SD卡插入Raspberry Pi,因而可以认为CN0511是即插即用的。Kuiper Linux镜像包含控制信号发生器所需的所有必要软件。有两种方法可改变输出功率和频率:使用PyADI-IIO模块写入代码,或使用IIO-Oscilloscope图形用户界面(GUI)输入所需的输出。

PyADI-IIO是ADI硬件的Python抽象模块,带有工业输入/输出(IIO)驱动程序。此模块为控制硬件提供了简单易用的Python方法和属性。通过非常简单的Python代码行即可控制该板,这些代码可以在本地或远程运行。可以使用简单的for循环和一些延迟来创建任何频率扫描,用于测试其他设备。

IIO-Oscilloscope是一个跨平台GUI应用程序,需要用户输入输出功率幅度和频率作为参数。

PyADI-IIO和IIO-Oscilloscope这两个模块均提供了结温传感器的输出:一个在PLL IC内,另一个在矢量信号发生器IC内。图9展示了这两个软件模块以及与CN0511板通信所需的其他组件(libAD9166、LibIIO和Linux内核)。图9中显示的libAD9166是在Kuiper镜像上预装的另一个库,用于准确控制输出功率,包含输出校准功率所需的C++代码,并特定使用于该板。关于如何实现校准的理论将在B节:输出功率校准中继续讨论。

图9.通过PyADI-IIO和IIO-Oscilloscope与设备通信所需的软件组件框图

B:输出功率校准

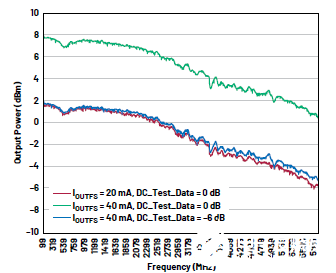

在信号发生器应用中,频带平坦度是一个关键参数。在该系统中,输出功率与频率的关系特性主要由矢量信号发生器的输出决定。随着频率提高,输出阻抗从其直流值开始减小。输出阻抗的这种变化以及负载处的任何阻抗失配都会直接影响输出功率。此外,可预测的sinc滚降也会影响输出功率的频率响应。图10讨论并显示了测得的未校准输出功率与频率的关系。为了克服这些不利因素,我们对输出功率与频率的关系进行了软件校准。

用于校正输出功率的旋钮包含了AD9166的两个寄存器:设置满量程电流的10位寄存器Ioutfs_reg(地址0x42和0x41)和设置满量程电流的16位寄存器Iout_reg(地址0x14E和0x14F)。这两个寄存器负责控制AD9166 DAC的输出电流,这也是AD9166放大器的输入(图3)。

Ioutfs_reg提供大约10 dBm的输出功率动态范围,这是用于调整图10所示不必要特性的理想值。

图10.输出功率与频率的关系:未校准的输出功率

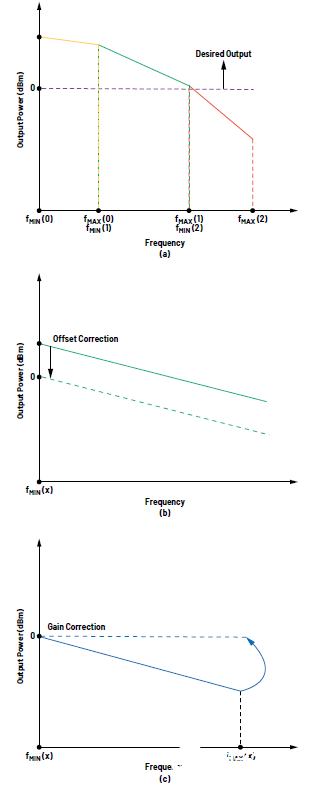

从测量结果来看,每个PCB样片都显示出图10所示的相同形状特性,只是偏移存在差异。考虑到这一点,我们开发了两个校准例程。第一个校准程序只需执行一次,用于获取校准整个形状所需的参数,使其平坦化,;第二个程序则用于校正不同板之间的偏移误差,并作为每片板的生产测试运行。两个校准例程均通过输出测量、计算和基于计算的寄存器调整来完成。

第一个校准例程的主要设计思路如图11所示。首先,图10中的整个特性曲线被分成多个频率区间,这些区间可以用从fmin[x]到fmax[x]的线段来近似表示,其中x是区间的索引,x ∈ [0, 31],并且x为正整数。实际设计选择了31个区间,但为了更好地举例说明,图11a中只显示了三个区间。对于每个区间,需要获得两个常数:一个是用于偏移校正的Offset_correction(图11b);一个是用于增益校正的Gain_correction(图11c)。还需要存储参数fmin[x]以跟踪区间。

图11.校准例程的可视化举例:(a) 将特性曲线分成多个部分;(b) 对每个部分进行偏移校正;(c) 对每个部分进行斜率校正。

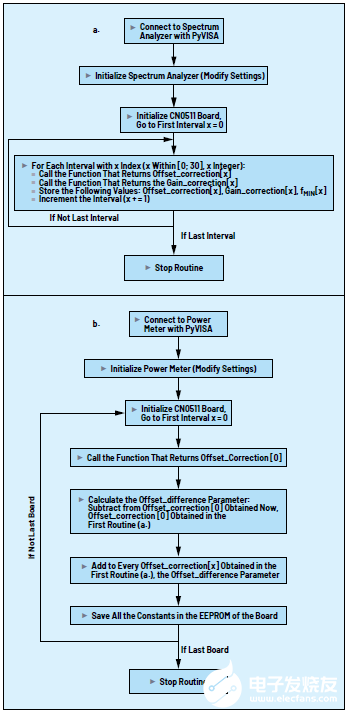

图12a为第一个校准例程的工作原理伪代码流程图。为完成此算法,需要使用非常精确的频谱分析仪来测量输出功率(使用Keysight E5052B/R&S FSUP)。第一个例程(图12a)产生的参数用于第二个校准例程,如图12b所示。

图12.伪代码流程图:(a) 只运行一次的第一个校准例程;(b) 在每个CN0511板上运行的第二个校准例程。

第二个校准例程(图12b)是针对生产测试中每个PCB样片运行的,并为每个区间的Offset_correction参数增加同一常数。在第二个例程结束时,对于每个区间,修改的参数Offset_correction[x]、Gain_correction[x] 和fmin[x]都将存储在电路板的EEPROM中。当电路板工作时,这些参数将在软件中进一步使用。

为设置校准输出功率,软件使用公式1来计算调整频率fx处的输出功率的Ioutfs_reg寄存器值,以。fx是区间x内的频率:fx ∈ [Fmin[x], fmax[x]),fx为实正数,fmin[x]是索引为x的区间的最小频率。

如公式1所示,电路板上必须为每个x区间存储三个参数,以便进行输出校正:即Offset_correction[x]、Gain_correction[x]和fmin[x]。

系统性能

A:校准输出功率

图13显示了CN0511在几种不同输出功率水平下的宽带补偿频带平坦度。对于设置在0 dBm和-40 dBm之间的任何输出功率,从DC到5.5 GHz的整个频带内的精度为±0.5 dBm。

图13.校准输出功率与频率的关系

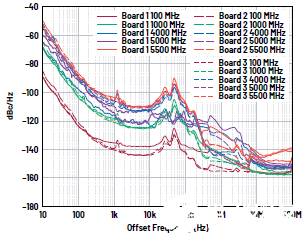

B:相位噪声

时钟源的质量以及其与AD9166时钟输入端的接口会直接影响相位噪声性能。在指定频率偏移处的相位噪声和杂散会被直接转为输出信号。图14显示了经过测量的单边带(SSB)相位噪声与频率偏移的关系。所有数据都是在输出功率设置为满量程的情况下收集的。使用板载122.88 MHz CMOS压控晶体振荡器用作系统时钟参考。

图14.系统相位噪声性能

C:热性能

根据应用和配置,高速DAC的功耗可能接近4 W。该器件使用裸露芯片封装来降低热阻并允许芯片直接散热。使用带风扇的机械散热器来散发封装的热量。在安装散热器的情况下,LTM4622在25°C的环境温度下显示出的最高温度读数约为60.6°C。

结论

本文提出了一种高频、低失真、低噪声的信号源。所介绍的系统是一种采用基于高速DAC的DDS架构的低成本RF信号频率合成器解决方案,通过使用基于DDS技术的矢量信号发生器,该系统较之简单PLL的有多项优势,例如简单化、低失真、高分辨率调谐、近乎瞬时的跳频、相位和幅度调制。

DDS架构的多项优势使得调整和校准输出功率以及微调输出频率成为可能。在系统中添加校准例程可为用户提供从DC到5.5 GHz的输出参考信号音,精度为±0.5 dBm,动态范围为0 dBm到-40 dBm。对于实验室仪器而言,这是一种近乎理想的解决方案。

-

DDS

+关注

关注

21文章

636浏览量

153023 -

信号发生器

+关注

关注

28文章

1482浏览量

109101

发布评论请先 登录

相关推荐

基于Raspberry Pi的合成射频信号发生器的实现

微型DDS信号发生器

泰克全新RF信号发生器系列叙述

DDS函数信号发生器是什么_DDS函数信号发生器原理及使用方法

DDS函数信号发生器是什么_DDS函数信号发生器简单介绍

使用基于Raspberry Pi的DDS信号发生器实现精确RF测试

使用基于Raspberry Pi的DDS信号发生器实现精确RF测试

如何使用基于Raspberry Pi的DDS信号发生器实现精确RF测试

使用基于Raspberry Pi的DDS信号发生器实现精确RF测试

使用基于Raspberry Pi的DDS信号发生器实现精确RF测试

评论