中国汽车工业协会最新数据显示,2022年1月至11月,新能源汽车产销分别完成625.3万辆和606.7万辆,同比均增长1倍,市场占有率达到25%。由此可见新能源汽车的发展已经进入了快车道。在这里我们注意到,由于里程焦虑和快速充电的要求,800V 电池母线系统获得了不少的OEM或者Tier1的青睐。谈到800V母线系统,让我们聚焦到其中的核心功率器件碳化硅功率模块,由于碳化硅得天独厚的优势,使得它非常适合用来制造高耐压、高结温、高速的MOSFET,这三高恰好契合了800V母线系统对于核心的功率器件的要求。安森美(onsemi)非常看好800V母线系统的发展,有一些研究机构,预测截至到2026年,SiC在整个功率器件市场的占比将达到12%以上。

安森美在碳化硅的领域涉足甚早,最早从2004年就开始SiC器件的研发。但是安森美是从2021年收购了GT Advanced Technologies (GTAT)之后开始全方位在碳化硅领域的投入,无论是资金,人力物力以及客户和市场。收购了GTAT之后,开始了安森美在碳化硅领域的垂直整合供应链——从晶体到系统之路!接下来我们将对两个碳化硅的关键的供应链衬底和外延epi进行分析和介绍,这样大家会对于安森美在碳化硅的布局和领先优势会有进一步的了解。

安森美碳化硅全垂直整合的供应链——从晶体到系统

供应链从我们位于新罕布什尔州哈德逊的工厂生长单晶SiC粉材料开始。在衬底上生长一层很薄的外延层,然后经过多个复杂的器件加工步骤生产出芯片,然后将芯片来封装成最终产品。整个制造流程端到端垂直整合,具有全面的可靠性、可追溯性以及完善的质量测试,以确保产品零缺陷的要求。

全垂直整合的供应链,在目前的供应链体系里具有相当的优势,如产能易于扩展、品质优和成本控制,尤其是目前碳化硅的整个供应链的每一个环节都不是那么容易可靠的高质量的量产,这个和硅的供应体系下是不太一样的。在硅的供应链里,硅片(衬底)通常会被交给第三方来生产,第三方的质量、成本和良率都做的相当不错。接下来我们会对衬底和外延的生产进行展开,这样大家就会明白为什么安森美选择在碳化硅领域选择了全垂直整合的供应链模式。这也使得安森美成为了目前全球为数不多具有从衬底到模块、到系统能力的公司。

晶体/衬底(substrate)

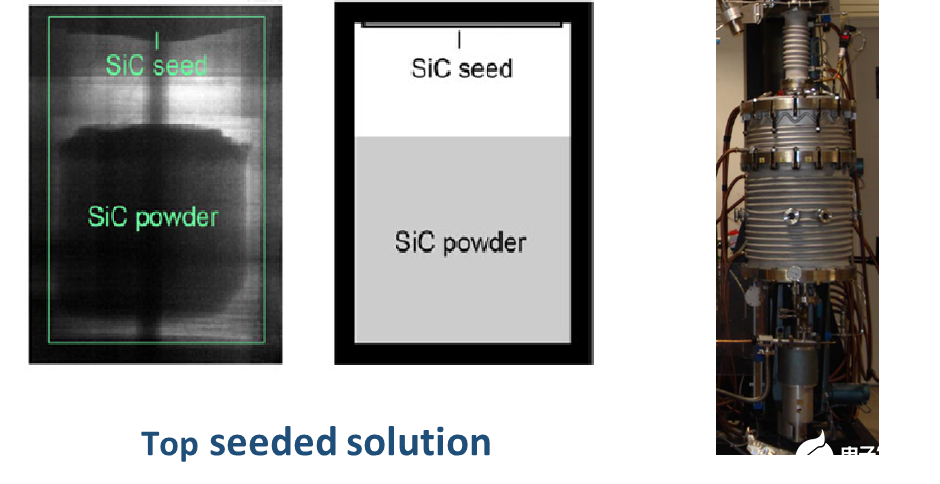

我们的芯片都是在衬底的基础上长上一层薄薄的外延,然后才拿去制作芯片。那衬底又是怎样生产制造出来的呢?这里涉及到两个步骤,首先是将碳化硅粉放到长晶炉里生长成晶体得到碳化硅晶锭,碳化硅晶锭需要打磨抛光,然后送去切割,并经过抛光这样得到了我们生产器件需要的晶圆衬底。图一是一个长晶炉的示意图和实物照片。

图一长晶炉示意图和实物

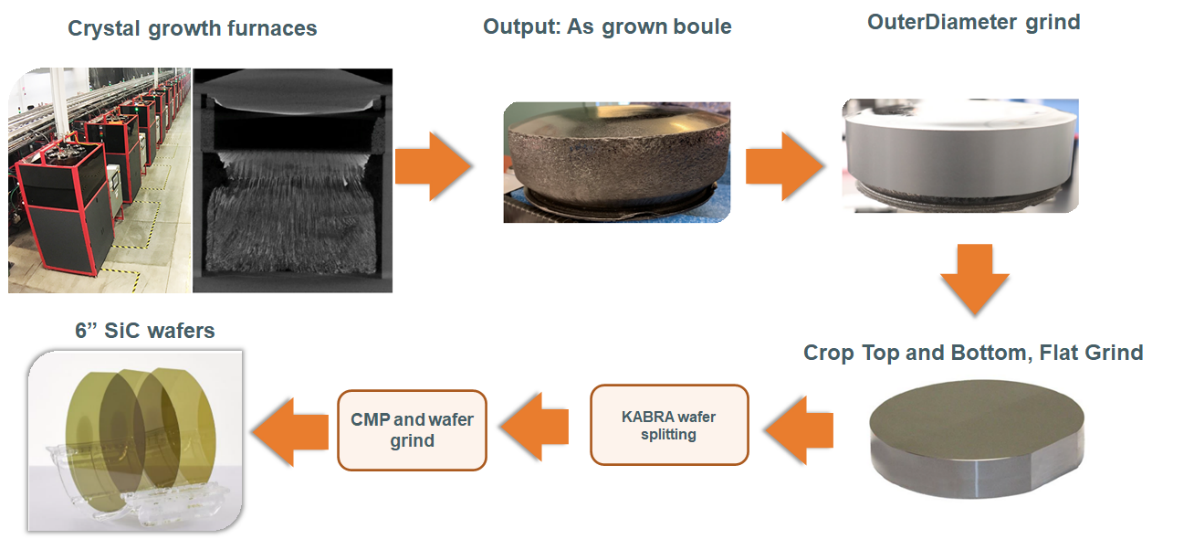

这里面涉及到了两个关键的步骤,晶体生长,晶锭切割和抛光。图二则是我们从碳化硅粉到衬底的生产流程简图

图二 碳化硅衬底生产流程图

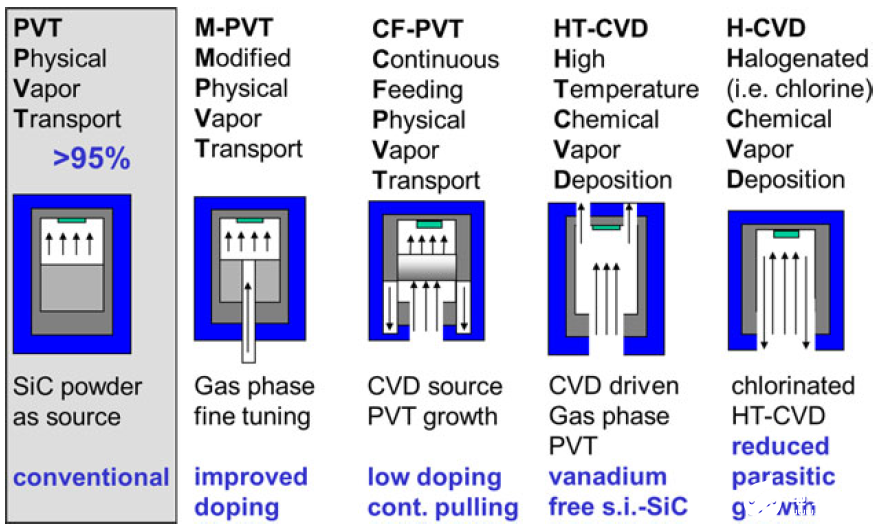

目前比较成熟的碳化硅晶体生长方法主要是PVT和CVD两种,它们都属于气象生长(vapor phase growth),而碳化硅型体主要是4H和6H两种。

图三碳化硅晶体生长方式

首先我们来看看晶体的生长都面临哪些挑战

要拥有高品质的籽晶(种子)

减少从籽晶到新生长的晶体缺陷的技术

晶体生长需要高温(>2000°C)

○ 在这些温度和生长时间下,很少有材料保持惰性,很容易发生反应。

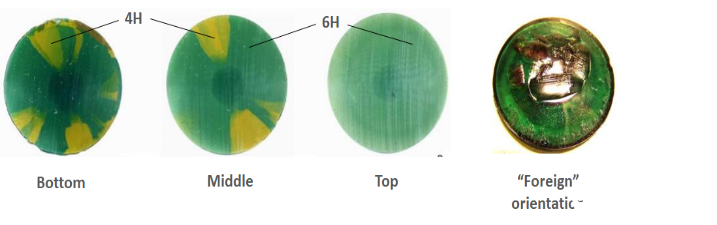

多态性–多达220种型体,目前可用的主要是用4H和6H

不一致的分解(气体: Si, Si2C, SiC),(固态:碳)

源头的纯净度 – 缺陷的晶核点

与Si相比,晶锭长宽比往往较低

整个行业面临的主要挑战是长出更长的无缺陷晶体

晶体直径扩大(目前最大是8“)

○无裂纹、高结晶质量(晶片边缘附近的晶界、缺陷等)

而GTAT本身是从生产制造长晶炉起家的,到现在差不多有20年左右的碳化硅长晶炉的设计制造经验,对于晶体生长的这些挑战,GTAT拥有者丰富的经验,我们有高品质的籽晶,很好的温度的控制等,有很好的缺陷控制技术以及很好的缺陷检测和标识能力。

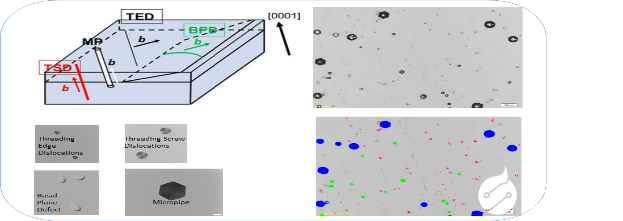

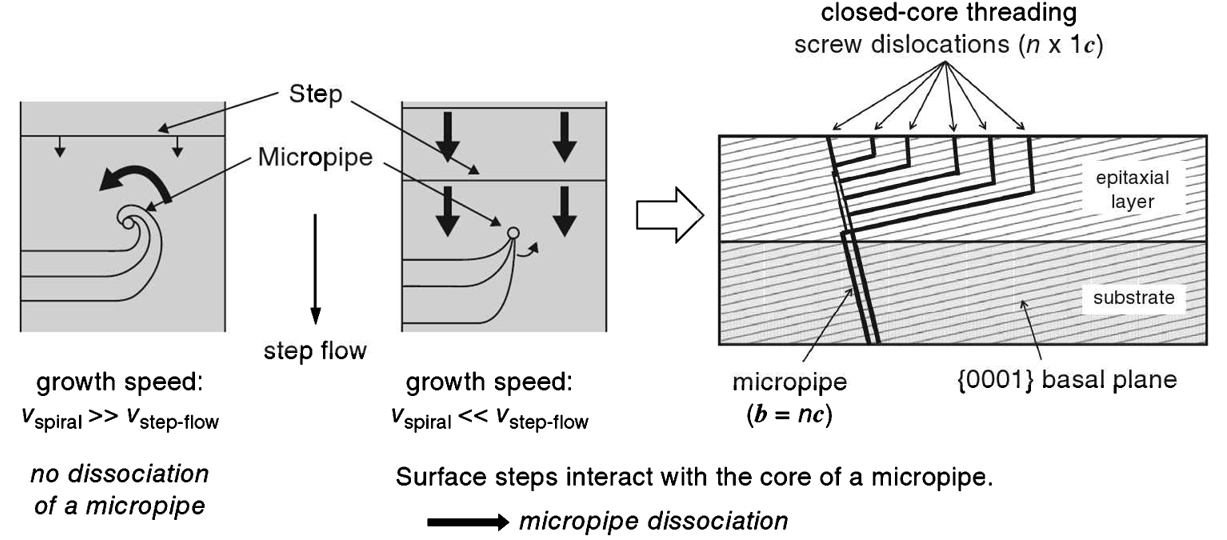

谈到碳化硅的缺陷,下面是碳化硅晶体的几种典型的缺陷

晶型不稳定性

开核位错(微管)

闭合核螺钉位错

低角度晶界

常规位错

基底平面位错(BPD)-基底平面边缘位错或部分BPD

螺纹边缘错位(TED)

叠加故障/转换

这些缺陷都是在衬底或者说晶锭阶段产生的,但是这些缺陷一旦产生了,就没法消除,它们会继续衍生到外延层,最终会影响到器件的质量。所以我们不仅需要在衬底阶段就要标识出来,在外延层也要把他们标识出来以排除在外。这个对外延层带来了挑战。

| 晶型不稳定 | 4H-SiC中的各种位错的特征 |

|

|

| 外延后的缺陷——位错的传播 | 外延层中的扩展表面缺陷 |

|

|

图四碳化硅衬底缺陷

高质量的晶体是整个碳化硅供应链的基石,而GTAT在这些方面积累了相当丰富的生产经验,它确保了安森美的碳化硅器件是在一个高质量的衬底上完成的。同时我们也可以非常快速的扩产,而这也是安森美富有竞争力的一个方面。

Epitaxy – EPI外延

碳化硅外延层是指在碳化硅器件制造工艺中,生长沉积在晶圆衬底上的那一部分。我们为什么需要外延?在某些情况下,需要碳化硅有非常纯的与衬底有相同晶体结构表面,还要保持对杂质类型和浓度的控制。这要通过在碳化硅衬底表面淀积一个外延层来达到。在功率器件中我们器件的每个单元等基本上都是在外延层加工完成的,它的质量对于器件来说重要性可见一斑。不同的器件对于外延的要求是不一样的。二极管对于外延的偏差和缺陷要求和MOSFET对它们的要求是两个不同层次的需求。MOSFET对于外延质量的要求很高。掺杂的偏差会影响MOSFET的Rdson的分布。有些缺陷会导致MOSFET轻则漏电流偏大,严重的会导致MOSFET失效。

外延目前来说比较成熟的加工技术是CVD,这也导致很多人误认为外延是比较容易加工的。其实这个是一个误解,外延并不是简单的把CVD的炉子买回来,就可以把它们做好,当然相对晶体衬底来说,它要相对简单一些但是并不代表它很容易做好,外延和晶体衬底面临的挑战是不一样的。也有很多人说现在市场上很多公司都有能力加工二极管的外延,他们只要稍微升级一下设备就可以很好的生长MOSFET的外延了,这个说法有待商榷。因为就像文章上面说的MOSFET和二极管对于外延的要求是不一样的,他们对于一致性和翘曲度等要求也不是一个数量级的。在外延这一个环节,安森美同样拥有丰富的经验,早在并购GTAT之前,安森美在碳化硅的外延和晶圆生产研发方面已经拥有超过10年的经验。因此我们会把这一优势继续保持,在扩大衬底生产的同时也扩大外延的生产。

相对晶锭衬底不同的是,外延的挑战主要集中在下面的几个指标上:

厚度以及一致性

掺杂和一致性

表面缺陷快速检测和标识追踪能力

底部缺陷快速检测和标识追踪能力

控制扩展缺陷

清洗

大尺寸的晶圆翘曲度的控制

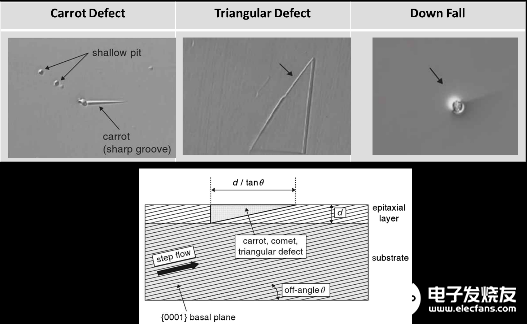

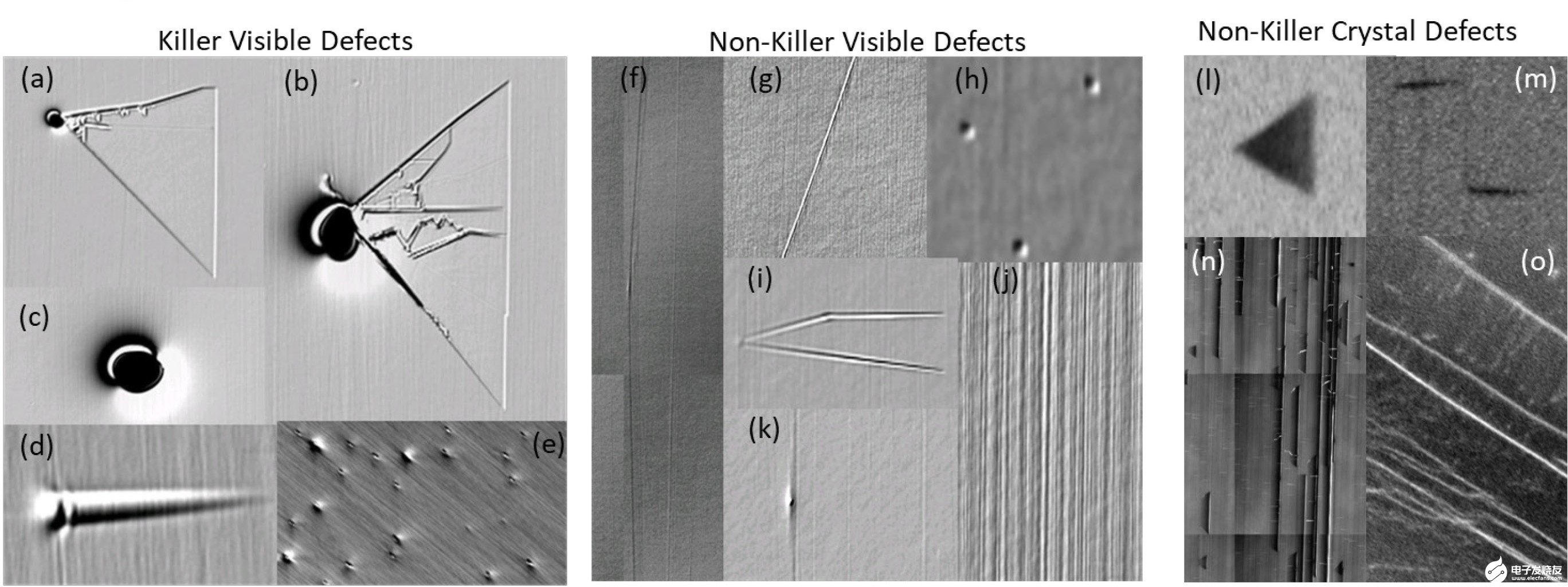

我们把检测到的缺陷做一下分类。

| 缺陷分类 | ||

| 致命的可见缺陷 | 非致命可见缺陷包括 | 非致命晶体缺陷包括 |

| (a)三角形缺陷、(b)颗粒三角形、(c)颗粒/下降、(d)胡萝卜和(e)强地形缺陷。 | (f)钝角三角形、(g)划痕、(h)凹坑、(i)V型缺陷、(j)粗糙度/台阶聚集和(k)小地形缺陷。 | (l)层错、(m)基面位错、(n)棒层错和(o)晶界。 |

|

||

图五 外延缺陷

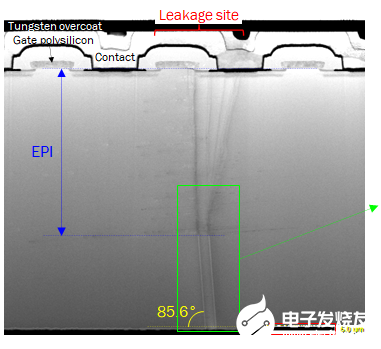

下图是一个完整的MOSFET active cell,这里就包含了衬底的缺陷,然后衍生到外延的缺陷。

图六 碳化硅MOSFET缺陷剖面图 - 衬底外延缺陷

总结一下,由于衬底的缺陷不能在外延层去把它消除,所以我们会采取一定的策略,让致命缺陷恶化,然后把它们筛选出来,这样的话在外延这一个流程中就要求衬底的缺陷具有可追溯性,所以对于衬底和外延都自己生产的公司就具有天然的优势。可以比较好的控制缺陷率。

由于衬底和外延和芯片的技术发展相关性不是特别大,所以我单独把这两个流程拿出来和大家分享,接下来的芯片技术发展比如MOSFET的平面结构或者沟槽结构都是直接在外延层里加工。因此后面的技术发展我们可以再分别拿出来讨论。安森美在衬底和外延的供应链上垂直整合了自己内部的资源,因此对于客户来说,他们的供给是可以预测的,这也是很多全球性的客户积极的和安森美签署了长期供应协议,因为我们的这一供应模式给予了他们长期保障。

-

安森美

+关注

关注

32文章

1713浏览量

92213 -

功率器件

+关注

关注

42文章

1805浏览量

90715

发布评论请先 登录

相关推荐

碳化硅的布局和领先优势

碳化硅的布局和领先优势

评论