导读

在半导体的发展进步中,有这样一些组织的存在,如美国的IBM、比利时的imec、法国的CEA-Leti等。在芯片的演进过程中,这些研究机构起到了不可磨灭的贡献。例如,IBM曾在2015年第一个提出要大规模生产7nm芯片,必须要采用EUV技术;2017年,IBM表示纳米片架构将是FinFET之外的下一个器件架构,目前3nm和2nm中都在采用这种结构。他们是半导体发展前进的基石。

未来的芯片演进还在继续,逻辑缩放技术仍是现代计算的基础。这些研究机构也是为了晶体管的微缩和半导体行业的发展“操碎了心”,他们在晶体管结构、新型互联、下一代EUV光刻、封装技术、新材料等多个领域进行积极探索,来寻找制造下一代节点芯片的方法。

01. 美国蓝色巨人IBM

IBM虽然早在2014年就将其制造业务出售给GlobalFoundries,退出了半导体代工业务。不过其与GlobalFoundries签订了10年的合作伙伴关系承诺,IBM还与英特尔、三星等保持着密切的合作关系,除此之外,IBM在奥尔巴尼也有自己的晶圆厂。凭借这些制造的支持,IBM在逻辑缩放中一直发挥着重要的作用。

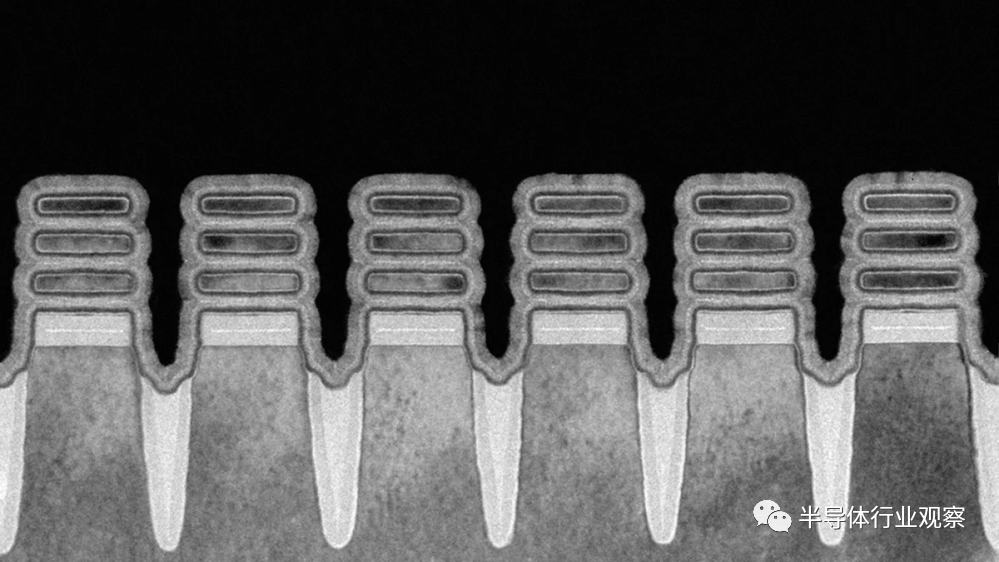

晶体管结构:2012年IBM首次提出“Nanosheet”这个新晶体管架构,在这一架构的支撑下,IBM研究院在2021年推出了全球首款2纳米节点芯片,与现代 7nm 处理器相比,IBM 的 2nm 开发将在相同功率下将性能提高 45%,或者在相同性能下将能耗提高 75%。IBM 表示,该技术可以“在指甲盖大小的芯片上安装 500 亿个晶体管”。去年年底,IBM还和日本的Rapidus宣布合作在日本的晶圆厂中进一步研发2nm。

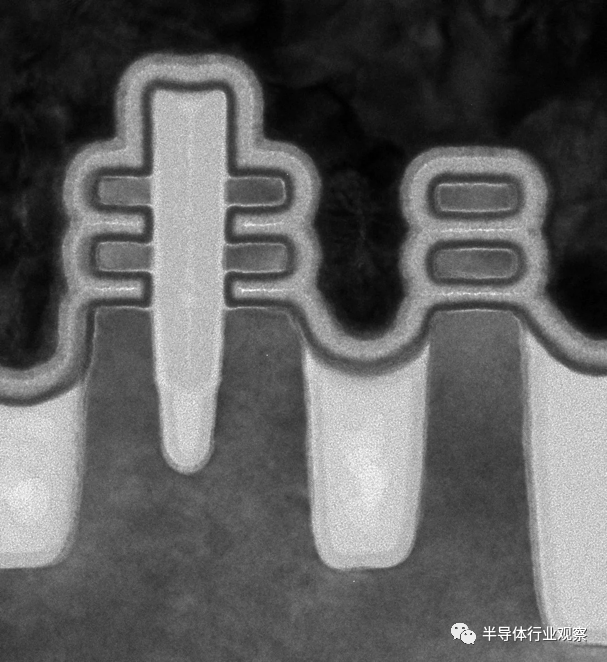

使用透射电子显微镜观察到的一排2 nm纳米片器件

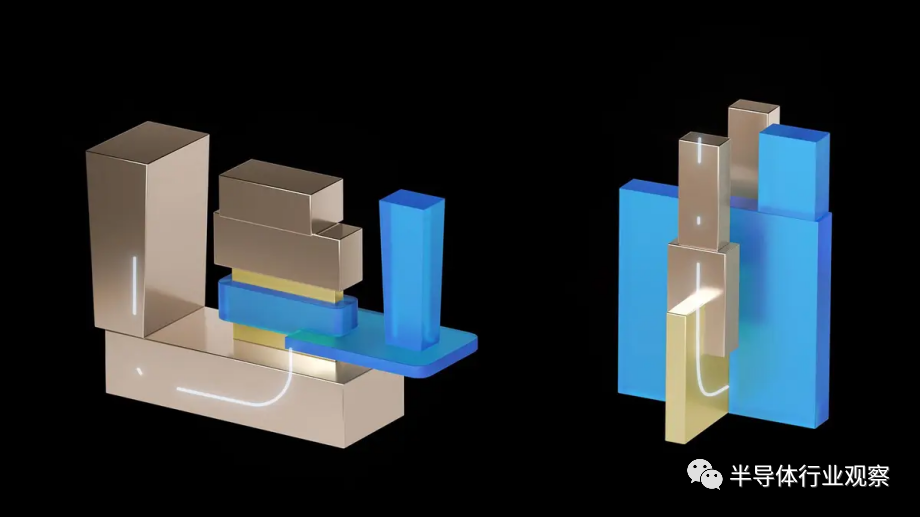

IBM 研究中心还在继续探索扩展到1 nm及以上。在2021年的IEDM会议上,IBM联合三星推出了一种设计半导体的新方法垂直传输纳米片场效应晶体管(VTFET)。如下图示意图所示,VTFET垂直于硅晶圆层叠晶体管,并将电流垂直引导至晶圆表面。这种新方法通过放宽对晶体管栅极长度、间隔物厚度和接触尺寸的物理限制来解决缩放障碍,从而可以优化性能和功耗等功能。在2022年的IEDM会议上,该小组的研究进一步表明,VTFET设计的规模可以远远超出其在2021年首次推出的最先进的2纳米节点纳米片设计的性能。据IBM的研究,与按比例缩小的FinFET替代方案相比,VTFET可提供两倍的性能或最多减少85%的能耗。IBM认为VTFET将在未来几年保持摩尔定律的活力。

VTFET(左)和横向FET(右)晶体管的 排列方式以及流经它们的电流

新型的互联材料:1997年,IBM率先从铝互连转向铜布线互连,铜互连至今仍是主流的互联标准。随着芯片来到2nm、1nm,IBM正在探究铜互连之外的新材料,金属钌是IBM的重要研究对象。

小芯片混合键合:小芯片是当下比较火的一种封装方式,而其从研究转向生产的最大困难之一是小芯片在封装过程中粘合在一起的方式,目前大多数的方法产生的粘合厚度在150至30微米之间,并且需要非常紧密的焊接才能有效。但IBM和ASMPT研究出了一种新的方法,他们将铜和氧化物熔合成只有几个原子厚的层,并且不使用焊料,最终使得小芯片之间的粘合只有0.8微米左右,比目前正在测试的其他方法要薄得多。

两层之间的微小粘合的微观图像

02. 比利时的Imec

自1984年以来,imec就一直在进行前沿半导体技术的研究。为了使CMOS晶体管能够继续微缩,imec正在多个领域进行广泛的研究。

1、晶体管架构的创新

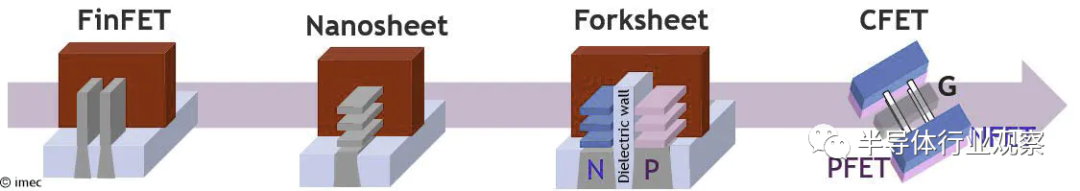

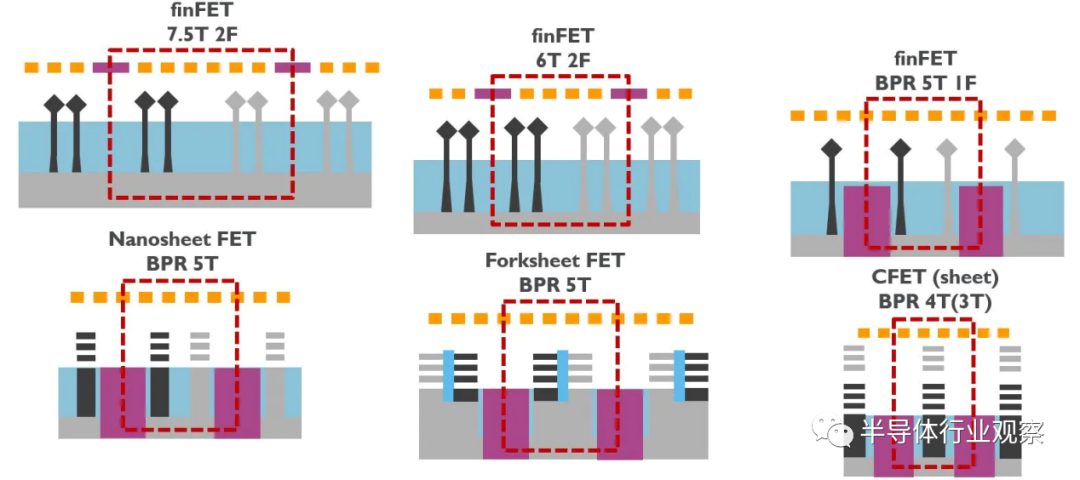

2012年,首款商用22纳米FinFET推出,至今其仍主流晶体管架构,但随着尺寸的不断缩小,缩小到5nm后FinFET逐渐失去动力,不良的短沟道效应需要引入新的晶体管架构。imec认为,晶体管架构的发展路径是:FinFET器件—》纳米片器件(nanosheet)—》叉片Forksheets—》CFET。

不同晶体管架构的示意图

具体来看,FinFET架构中最先进的节点在6轨 (6 Track) 标准单元中具有2个鳍片。而垂直堆叠的纳米片器件(nanosheet),将使标准单元的轨道高度缩小到五个轨道(5T)。随着轨道高度越来越小,单元高度的进一步降低将需要单元内 nFET 和 pFET 器件之间的间距更加紧密。然而,对于 FinFET 和纳米片器件而言,工艺限制限制了这些 n 和 p 器件的紧密结合程度。

于是,imec开创了一项独特的技术叉片(Forksheets)器件,叉片可以被imec认为是纳米片器件的自然延伸,它能允许轨道高度从5T扩展到4.3T,同时仍然提供性能增益。按照imec的说法,Forksheets可将Nanosheet扩展到2nm技术节点以上。

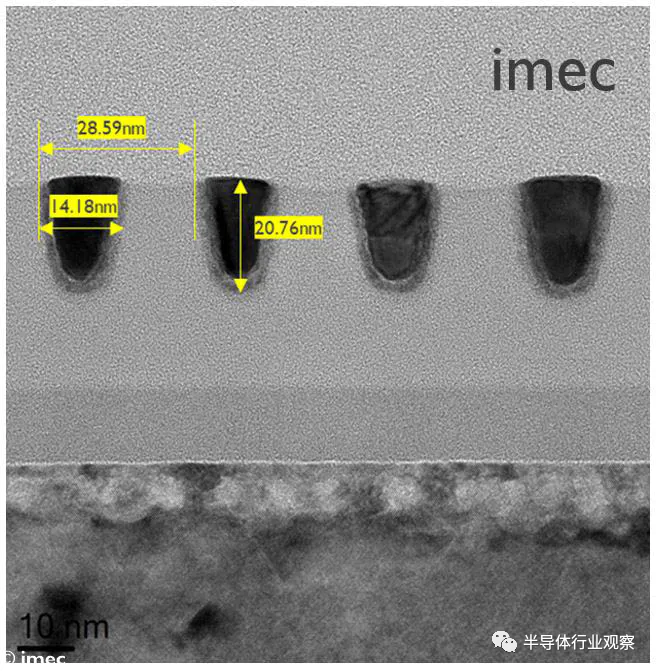

图源:imec

据了解,Forksheets器件采用300mm工艺,栅极长度降至了22nm。而且在n型和p型场效应晶体管中都有两个堆叠的硅通道,功能齐全。与垂直堆叠在同一晶圆上的纳米片器件相比,Forksheets器件的短通道效应控制水平(SSSAT = 66-68毫伏)相当。在Forksheets器件中,使用双功功能金属栅极采用了替代金属栅极流程,将n型和p型场效应晶体管的间距紧凑至17纳米(约为最先进的FinFET技术中间距的35%),这是新器件架构的关键优势之一。

下一代晶体管架构则被认为是CFET,CFET的原理是将nFET“折叠”在pFET顶部(鳍叠鳍或片叠片),从而充分利用3D器件缩放的可能性。基于纳米片的CFET可以提供额外的性能提升,并且是缩小到3T逻辑标准单元所必需的。imec及其合作伙伴专注于单片CFET集成,因为与现有的纳米片型工艺流程相比,这种集成方案的破坏性最小。

图源:imec

2、EUV光刻创新

长久以来,图案化技术的不断发展以及新型材料的引入一直是推进逻辑和存储技术扩展路线图的关键。EUV光刻系统的发展可以追溯到2000年代,到2019年,EUV光刻进入大批量制造,用于印刷7nm逻辑后端线最关键的金属层和通孔,金属间距在36-40nm范围内。未来几年,下一代高数值孔径 (high-NA) 的EUV***将被需要。

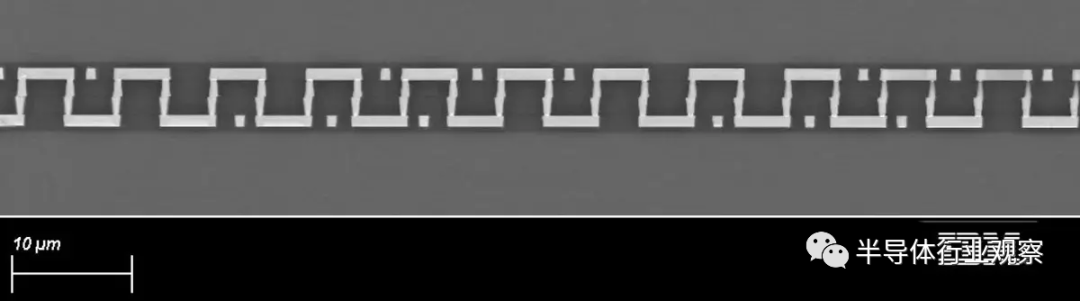

imec目前正在与ASML合作开设高数值孔径实验室,并为行业创建生态系统,共同应对工具开发过程中的工艺挑战,包括变形成像、新掩模技术、改进的光学邻近校正 (OPC) )技术、薄膜图案化材料开发、计量等。Imec和ASML在2021年2月就已经展示了使用Inpria的金属氧化物(MOx)抗蚀剂工艺的28nm间距线/空间的单曝光模式准备情况,这对应于5nm技术节点的关键后端线金属层。这一突破使得NXE:3400扫描仪非常接近其大批量生产的分辨率极限。

imec将0.33NA EUVL的单次曝光图案化能力推向极限

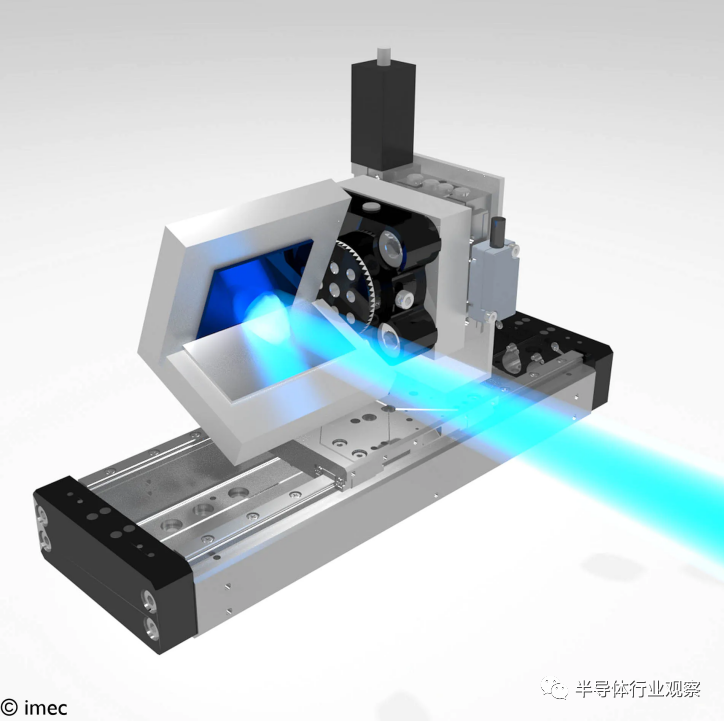

此外,imec还在支持材料供应商开发新型光刻胶材料,为此,imec投资建设了Attolab分析实验室,该实验室将用于探索光刻胶成像的基本动力学,并为ASML的第一个0.55高数值孔径EXE5000原型面世之前提供用于工艺开发的图案化300mm晶圆。

用于高数值孔径EUV干涉取样片实验的 Lloyd’s装置示意图(图源:imec)

3、3D封装

3D封装已被证明是提高系统性能的一种有吸引力的方法。imec正在开发一系列3D封装实现的因素:

混合键合技术:imec正在突破芯片到晶圆混合键合的物理可能性界限。例如具有创纪录低间距的微凸块互连,这种高密度连接充分发挥了硅通孔技术的潜力。它们允许芯片之间或芯片与硅中介层之间的 3D 互连密度比现有技术高出十六倍以上。使用混合铜键合也可以将芯片直接键合到硅上。imec正在利用其在晶圆间混合键合中学到的知识,开发间距小至3μm且具有高公差拾放精度的芯片间混合键合。

背面供电:对于高密度晶圆对晶圆堆叠,imec正在研究超低互连间距的混合键合,目前的目标是500nm间距互连。为了帮助实现这一目标,imec正在探索新的晶圆重构技术以及高密度再分布(RDL)技术,其导线尺寸在微米范围内,并且具有高密度封装通孔技术。

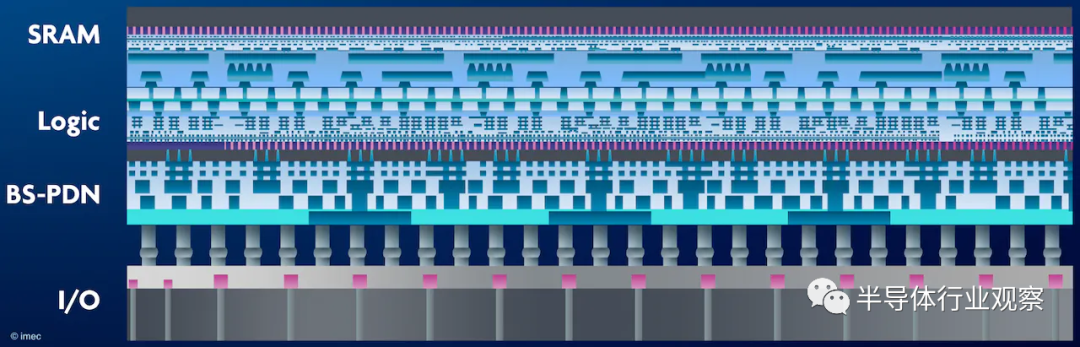

背面供电实现的3D-SOC示意图

4、互连新材料和新方式

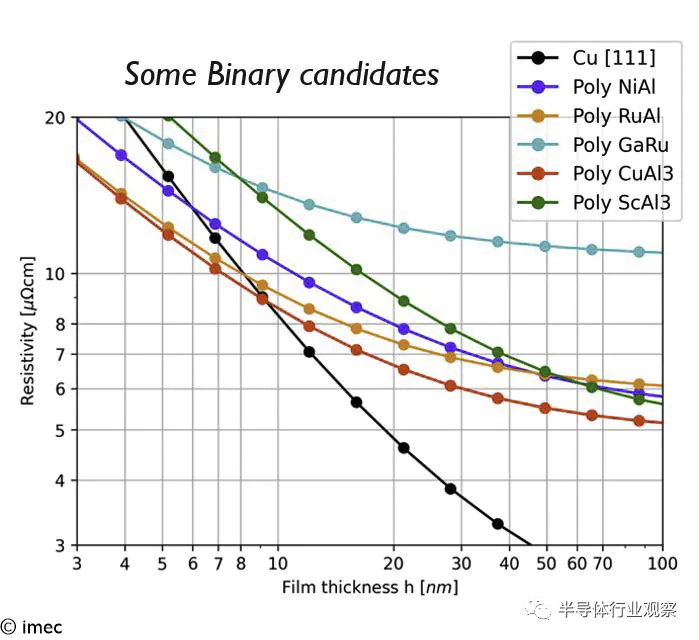

为了跟上器件尺寸不断缩小的步伐,最先进的逻辑和存储芯片中最关键的互连线的宽度很快就会接近10纳米。自20世纪90年代中期推出以来,铜 (Cu) 一直是逻辑后道 (BEOL) 应用中制造互连线和通孔的主流导体金属。随着金属线宽逐渐缩小,Cu互联逐渐失去动力和优势,所以imec正在找寻应用于BEOL的新材料。2023年5月,imec首次在 300mm硅晶圆上展示电阻率低于Cu和Ru的导体薄膜。除了金属材料之外,大约五年前,imec研究人员开始探索二元和三元化合物来替代铜作为未来互连金属化方案。

一些二元候选材料的电阻率情况

另外,随着计算能力和内存容量的指数级增长,对I/O带宽的需求也相应增加,这只能通过进一步改进光链路来满足。imec开发了实现这些未来光互连的技术。imec从带宽扩展、功耗 (10倍) 和每比特成本 (10-100倍) 这三个维度来优化光互连。

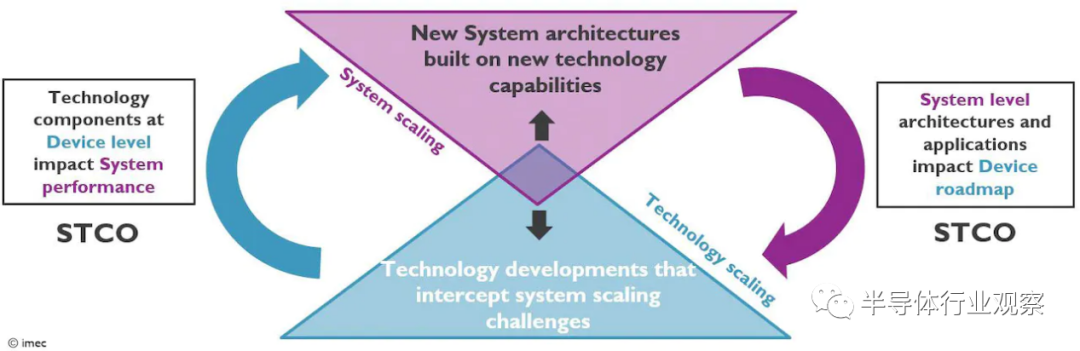

5、系统技术协同优化(STCO)

现在进入后摩尔时代,DTCO成为行业采用的新方式。但在imec看来,要获得更大的性能提升,不仅仅需要DTCO(设计技术协同优化),还需要使用STCO(系统技术协同优化)。最佳的系统实现将是极限CMOS 逻辑缩放、3D封装、新颖的存储元件甚至硅光子学等多种技术微妙优化的结果。

因此,imec正在用STCO补充DTCO,STCO计划的目标是以自上而下的方法将未来的系统需求和瓶颈转化为技术要求。该计划将确保 DTCO 研究与系统应用空间之间的联系。STCO将用来解决内存墙、配电或SoC子系统分区等系统问题。Imec的目标是确定 STCO所需的技术并使其成熟,以提高系统级性能。

STCO 框架的示意图

6、存储领域

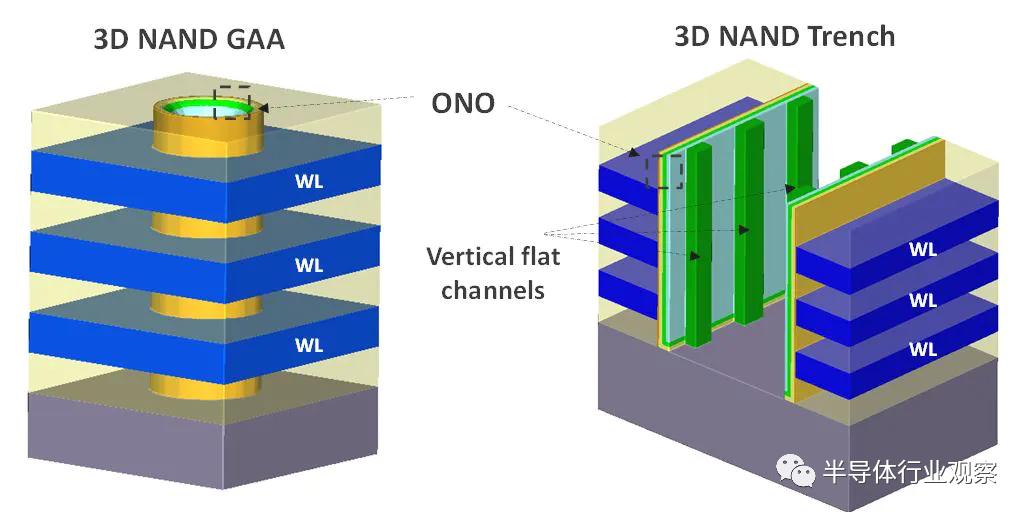

3D NAND:除了逻辑芯片的缩放,imec也在为存储领域的向前发展努力着。首先,在NAND传统存储领域,imec通过开发新的低电阻字线金属、研究存储器电介质堆叠的替代品、改善沟道电流以及确定控制由于堆叠层数不断增加而产生的应力的方法,为3D NAND的发展做出了贡献。

到2030年,当GAA NAND闪存规模达到饱和后,imec预计将引入一种新的架构来连接电荷陷阱单元:沟槽单元架构。通过这种架构,3D NAND摆脱了圆形GAA存储单元几何形状。相反,这些单元是在沟槽的侧壁上实现的——类似于侧面倾斜的平面配置——两个晶体管位于沟槽的相对壁上。这种下一代 NAND 闪存单元架构不仅将提供所需的位存储密度飞跃,而且还将提供所需的存储密度。它还有一个优势是可以降低成本。

3D NAND GAA和沟槽器件的3D示意图

新型存储:在存储领域,imec正在探索打破内存墙的方式,寻找改进MRAM和DRAM 技术的方法。新型存储技术3D铁电FET (FeFET)是imec在探索的领域。在3D NAND以外,imec正在评估一系列新存储概念的适用性,包括基于液体和DNA启发的记忆。

03. 法国的CEA-Leti

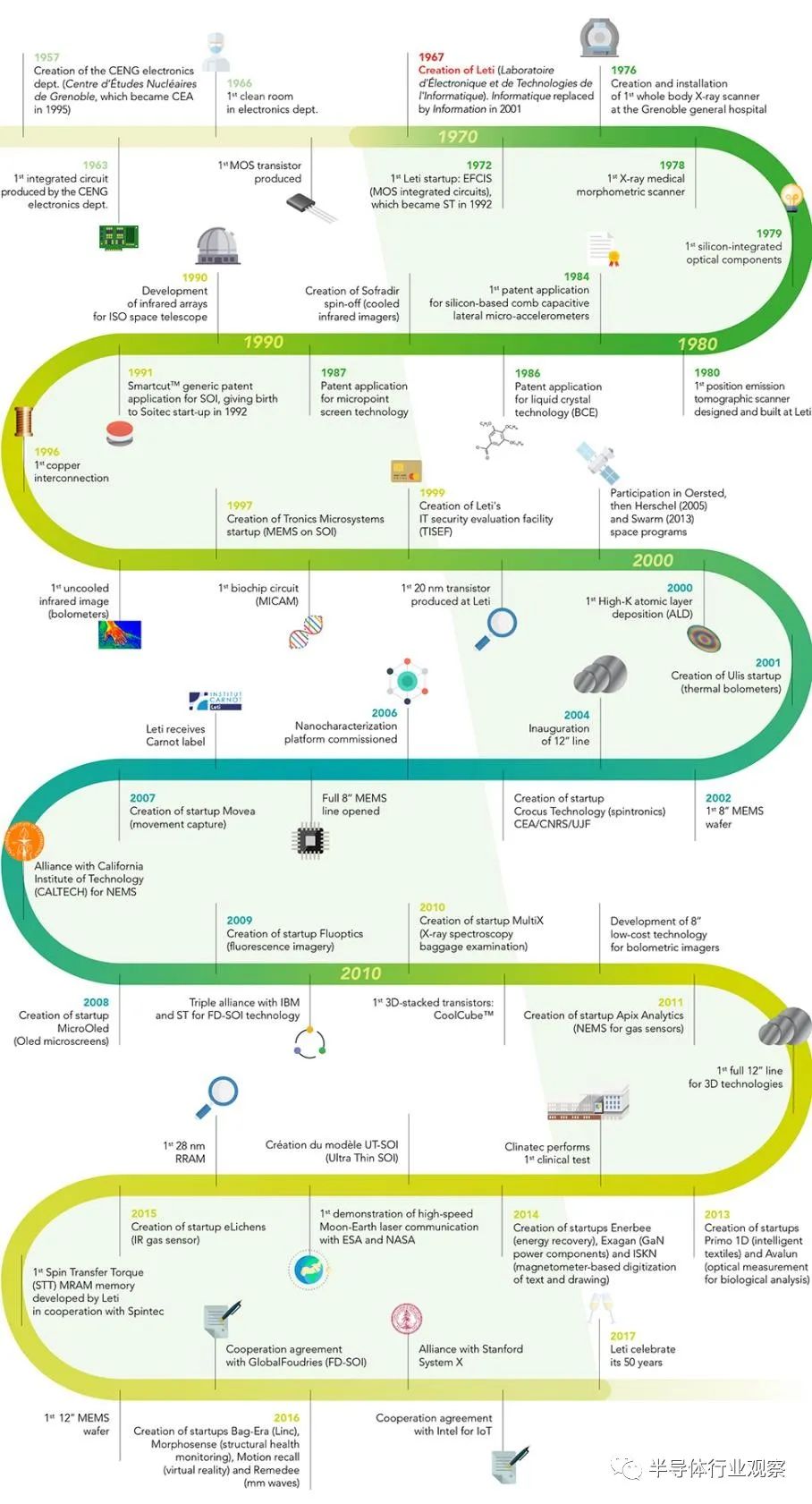

CEA-Leti成立于1967年,总部位于法国格勒诺布尔,该研究所的前身是成立于1957年的CENG(格勒诺布尔核研究中心)的电子系,目前大约有1900名研究人员。截止到 2022 年,CEA-Leti已在电子领域申请了291项专利。自成立以来,CEA-Leti已经孵化出了超过 75家的初创企业,其中75%仍在运营,比如SOI技术的领导者Soitec。下图显示了CEA-leti的重要里程碑事迹,如其是推动硅上绝缘体场效应管(FD-SOI)技术的重要推动者之一,该技术通过在晶体管的底部添加一层绝缘层,减少了晶体管之间的漏电流,提高了性能和能效。

CEA-Leti从成立至今的发展历史和重要里程碑

新材料:2023年6月19日,CEA-Leti和英特尔宣布两家将合作开发300毫米晶圆上的二维过渡金属二硫化物 (2D TMD)层转移技术,目标是将摩尔定律延续到 2030 年以后。这些2D材料具有良好的载流子传输和迁移率,适用于原子薄层,非常适合高性能和低功耗平台。此外,它们的器件主体厚度和适中的能带隙可增强静电控制,从而实现低断态电流。在这一合作中,英特尔主要为该项目提供制造服务,CEA-Leti提供键合和转移层专业知识以及大规模表征。

新型存储:CEA-Leti还在RRAM、PCM这样的新型存储领域发力。在RRAM领域,他们提出了一种“新颖的方法”,允许这些设备作为储能元件和内存运行,这取决于施加的偏差。内存能量是内存计算的一个补充特性,这是CEA-Leti路线图中的一个重点。它可以显著减少能源使用,因为基于RRAM的电池具有高度的可扩展性和动态分配性,而且它们可以放置在靠近处理器的内存块旁边。当处理器需要峰值功率(通常来自外部电源)时,将电源放置在处理器附近特别有帮助。

在PCM领域中CEA-Leti的研究使PCM直接堆叠在电路上成为可能。CEA-Leti的研究人员用与存储器串联的称为ovonic阈值开关 (OTS) 的小型设备取代了晶体管,有史以来第一次成功地将存储点集成到28纳米制造工艺末端沉积的后端线(BEOL)金属化层中。他们还设法将存储点放置在电路的顶层,防止在后期制造过程中损坏。

神经拟态/内存计算:CEA -Leti开发了一种受人类突触启发的模拟晶体管,它的优势主要体现在,其与突触的能量消耗几乎相同,比目前用于相同应用的其他组件(例如电阻式存储器)低100倍,再者,它采用与CMOS工艺兼容的200 mm晶圆上制造。一旦晶体管得到充分评估和确认,其低能耗将使其能够集成到神经形态电路中,应用于图像和语音识别。

在 IEDM 2020 上,CEA-Leti发表了两篇论文,概述了将3D架构与电阻随机存取存储器 (RRAM) 相结合进行内存计算的优势,以及它们在边缘AI和神经网络中的应用。CEA -Leti开发的GAA 技术适用于最先进的节点,并且可以支持 CEA-Leti 的内存计算方法。

芯片到晶圆 (D2W) 自组装:CEA-Leti 多年来一直致力于开发自组装方法,目标是大幅提高吞吐量和贴装精度。在2022年电子元件与技术会议 (ECTC) 上的一篇论文《用于高对准精度和高吞吐量 3D 集成的集体芯片到晶圆自组装》中展示了自组装过程的成功,该过程利用水的毛细管力来对齐目标晶圆上的器件,该工艺有望提高芯片到晶圆接合的未来每小时数千个芯片的对准精度和制造吞吐量。

04. 结语

IBM、imec和CEA-Leti等机构作为半导体行业的关键贡献者,通过其突出的研究和技术创新,推动了半导体技术的不断发展。他们现在的努力不仅改善了芯片的性能和功能,也为下一代节点芯片的制造提供了新的思路和方法。这些机构的杰出成就将继续对科技行业产生深远的影响,推动数字化时代的进一步发展和创新。

-

芯片

+关注

关注

459文章

51839浏览量

432449 -

晶体管

+关注

关注

77文章

9899浏览量

140021 -

半导体行业

+关注

关注

9文章

403浏览量

40906

原文标题:他们,为芯片操碎了心

文章出处:【微信号:算力基建,微信公众号:算力基建】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

未来的芯片演进还在继续,逻辑缩放技术仍是现代计算的基础

未来的芯片演进还在继续,逻辑缩放技术仍是现代计算的基础

评论