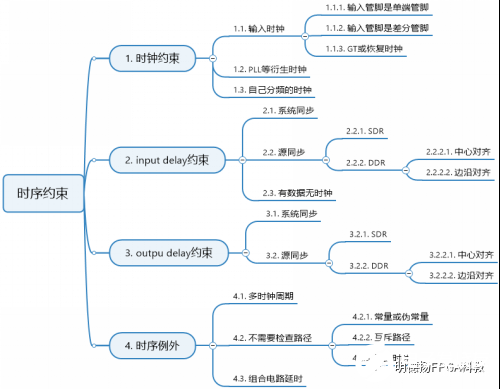

本小节对时序约束做最终的总结。如图1所示,前几节内容依次讲述了时序约束的四大步骤。第一是生成时钟约束;第二是输入端口约束input delay;第三是输出端口约束output delay;最后是时序例外。前几节内容把这些情况都归纳起来,对每种情况仔细划分,然后按照对应的情况进行时序约束即可。

图1 时序约束四大步骤

再强调一点,在工程项目开始阶段就要设置时钟约束和生成时钟约束。时钟约束又包括输入时钟、PLL等衍生时钟、自己分频得到的时钟。每种都有对应的要求和特点,根据需要查找对应的方式去完成约束。

在项目开发过程中,内部实际逻辑都写完了,并且全部满足时序要求,仿真没有问题了,不报告错误了,这时再对输入端口和输出端口设置相应的约束。比如跟外围器件的一个设置之类的。这时再去设置input delay 和 output delay。为什么要先保证内部逻辑设计是正确的再对端口进行约束呢?如果在内部时序不满足的情况下,对输入端口和输出端口进行约束了,这时如果出现错误,将无法确定是内部时序造成的错误,还是端口约束不对造成的错误。

input delay 和 output delay 一般有系统同步、源同步等几种,源同步又有SDR、DDR。虽然总的类型比较多,但是对应实际项目中的一种接口,必定是这其中的一种类型,此时只要按照对应情况去进行设置即可。开发人员确定待约束的输入信号的硬件接口到底是系统同步还是源同步?如果是源同步,是SDR还是DDR?如果是SDR,是中心对齐还是边缘对齐的?这样就可以逐步找到对应的情况进行约束。

而output delay 也是同样道理,根据实际的接口类型查找相应的约束方法即可。要注意两点,其一是 input delay 和 output delay 对应的公式是什么,代表什么含义。另外公式中的数据从何处获取,或者说怎么获取,只有获取有效的数据才能进行正确的约束。而且 input delay 约束和output delay 约束其实就是告知综合软件一些我们知道而综合软件不知道的参数,比如上游或下游芯片接口寄存器的建立时间、保持时间、PCB走线延迟等FPGA之外的数据。上游和下游芯片接口寄存器的建立时间、保持时间是可以通过数据手册以及示波器测量得到的,而PCB走线延迟也可以估算得到,最后将这些数据综合考虑成输入、输出接口的最大传输延迟、最小传输延迟告知综合软件,综合软件就可以根据这些参数对FPGA的时序进行调整,最后生成相应的时序报告。

当时钟约束、输入和输出端口约束都处理完了,没有问题后,最后做时序例外相关约束。目的是告知综合软件某些路径可能需要多个时钟周期才能得到正确输出,或者某些路径已经人为处理过了,时序是满足的,综合软件不需要对这些路径进行检查分析了。其中最重要的就是异步时钟的处理。

异步时钟是FPGA里面最多最常用也是最核心的一个部分内容,特别强调一定要做异步处理之后,才能将该路径force掉,时序例外掉。如果没做时序处理,就把它例外,排除掉,可能会出现严重的错误,开发人员还找不到原因,因为错误报告被屏蔽掉了。

上面就是时序约束的一个步骤,大家不需要记是怎么样格式去约束,只要按照的步骤去约束,查找对应的约束类型,然后按照对应要求约束即可,不要去记很多无用的东西,只要把约束类型归类好就可以了。

假如读者所在公司要求不一样,比如说顺序不一样,那就按照公司的要求去做。明德扬是按照前面介绍的步骤去做的,而且是成功的。当然不同的公司,有不同的做法、不同的要求,合理设置即可。

另外假如以后遇到一些情况,在这里面没有列明的。就需要按照这个表把它归纳到某种方式,补充完整,之后就可以使用了,这个表可以应付绝大部分的场合了。

审核编辑:汤梓红

-

DDR

+关注

关注

11文章

717浏览量

65750 -

时钟

+关注

关注

11文章

1756浏览量

132170 -

时序约束

+关注

关注

1文章

115浏览量

13493

发布评论请先 登录

相关推荐

VIVADO时序约束及STA基础

FPGA时序约束之衍生时钟约束和时钟分组约束

【潘文明至简设计法】系列连载教程 FPGA时序约束视频教程

时序约束的步骤分析

时序约束连载03~约束步骤总结

时序约束连载03~约束步骤总结

评论