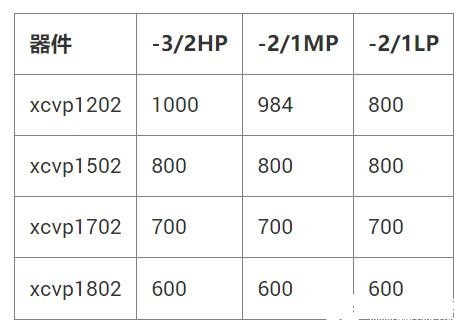

对于较长的时钟布线,可以降低时钟网络的 FMAX。下表列出了不同器件/速度等级组合下的最差情况 FMAX。

在 2022.2.2 版本中,DRC BFGCHK-1 会将设计中每个时钟网络的频率与以上最差情况 FMAX 表中的 FMAX 数值进行比对。

如果时钟网络的频率超出最差情况 FMAX,那么 DRC 会阻止比特流生成,因为按此频率操作时钟可能不安全。

[DRC BFGCHK-1] BUFG_has_device_restricted_FMAX:如果使用最大时钟扩展范围,时钟信号线 design_1_i/clk_wizard_0/inst/clock_primitive_inst/clk_out1 上的周期要求会超出此器件的 FMAX 规格 (600.00 MHz)。请参阅答复记录 AR34820,了解您是否可以为自己的时钟网络豁免此 DRC 检查。

* 注释:请参阅以下“Versal 时钟设置背景”部分,获取有关时钟拓扑结构扩展范围的更多详细信息。

解决方案:

当 DRC 检查 BFGCHK-1 报告违例时,并不一定暗示时钟信号线无法支持所需时钟频率,因为 DRC 仅基于最差情况 FMAX 检查最大时钟扩展范围。 为根据时钟网络的实际扩展范围来判定其支持的 FMAX,我们为每个时钟提供了一个 Tcl 脚本,用于计算最大时钟扩展范围和 FMAX。

如果针对每条时钟信号线计算所得 FMAX 低于时钟网络的实际时钟频率,那么可豁免 DRC,设计可以继续生成器件镜像。以下是如何豁免 DRC 的示例:

create_waiver -type DRC -id {BFGCHK-1} -user "" -desc "Ignore this DRC as all clocks are within FMAX specification."

检查确认所有时钟都在给定时钟扩展范围的 FMAX 规格范围内之后,仅限在器件镜像生成前将 DRC 严重性降级。

如果您重新编译设计,则可更改时钟信号线的最大扩展范围,并且需要在新布线的检查点上运行 validate_fmax Tcl 命令,查看是否可将 DRC 严重性降级。

Tcl 脚本详细信息

提供的 validate_fmax.tcl Tcl 脚本可用于计算当前设计中针对每个时钟网络遍历的时钟区域的最大数量,并从表中查找关联的 FMAX 值。该脚本计算遍历的时钟区域数量时会考量不同时钟布线资源。 例如,穿过 XPIO 时钟区域的时钟布线不影响 FMAX 并且不会添加到遍历的时钟区域数量中用于计算时钟网络的 FMAX。

使用 source 运行 Tcl 脚本时,会创建 validate_fmax Tcl 命令。运行 validate_fmax Tcl 命令时,如果没有 FMAX 违例,那么此命令会返回 1,如果设计中任意时钟信号线违反 FMAX 规格,则返回 0

source -quiet ./validate_fmax.tcl

validate_fmax

您也可以运行 validate_fmax 并搭配 -verbose 选项来提供设计中每条全局时钟信号线的详细信息。

% validate_fmax -verbose

Global clock net: clknetwork/inst/clock_primitive_inst/clk_out4:

PERIOD: 16.252

FMAX: 1070

Number Fabric CR traversed: 4

Global clock net: clknetwork/inst/clock_primitive_inst/clkout2_primitive_bufg:

PERIOD: 11.327

FMAX: 1070

Number Fabric CR traversed: 4

注释:该脚本应仅在已布线的设计/DCP 上使用。

Versal 时钟设置背景

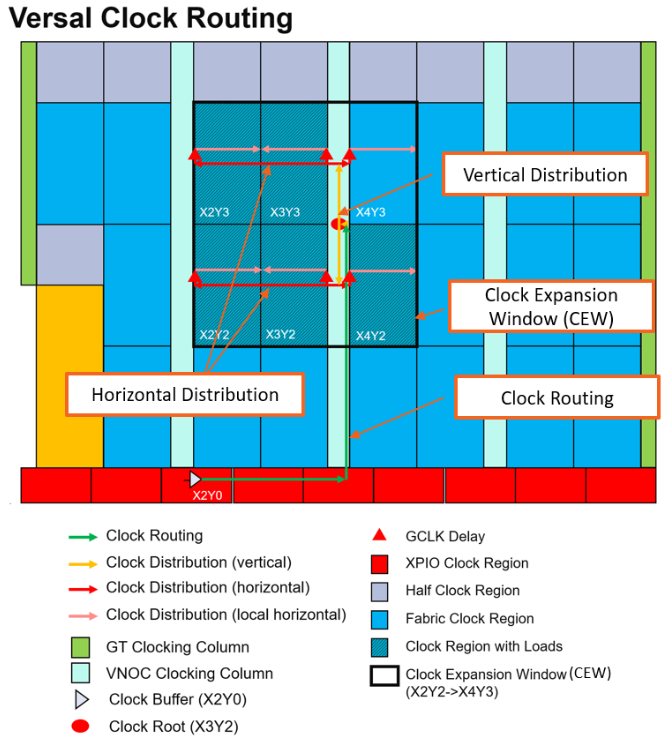

Versal 器件中的全局时钟网络的入口点是全局时钟缓冲器。时钟信号线通过水平和垂直布线资源,从全局时钟缓冲器布线到时钟根。 时钟使用垂直分布 H 树状和水平分布从时钟根分布到负载时钟区域。

下图显示了 SLR0 中跨时钟区域 X2Y2 到 X4Y3 的时钟的时钟布线示例。 X2Y0 中的全局时钟缓冲器用于驱动时钟穿过 XPIO 时钟区域到达 VNOC 时钟设置列,而后再到 X3Y2 中的时钟根的过程。 时钟从中分布到所有负载时钟区域。 负载时钟区域 X2Y2 和 X2Y3 都位于距离时钟根最远处,因此都存在最大数量的跃点。

如何为时钟网络改善 FMAX

可通过减少跃点数量或者选择最优时钟列来改善时钟网络的 FMAX。 穿过 VNOC 时钟列的时钟布线所得 FMAX 会好于穿过器件左右两侧 GT 时钟列的时钟布线。 穿过负载时钟区域中心的 VNOC 列布线的时钟到达最远端负载时钟区域过程中所产生的跃点数量较少,故而能得到更好的 FMAX。 您可使用 USER_CLOCK_ROOT 约束强制使用与负载时钟区域相关的更接近中心的时钟列。如需了解有关 USER_CLOCK_ROOT 的更多信息,请参阅UG1387。

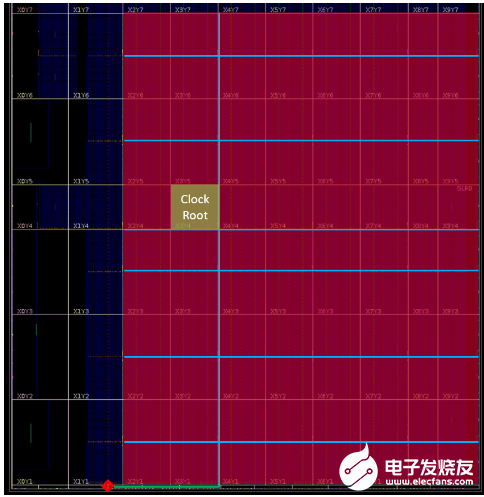

在以下示例中,XPIO 时钟区域 X3Y0 中的 BUFGCE 用于驱动时钟扩展窗口中的时钟负载,该窗口从 X2Y1 扩展至 X9Y6。 时钟根偏离中心,位于时钟区域 X3Y4 处。 当时钟根偏离中心时,相比于位于水平方向时钟扩展窗口上中心位置的时钟根,时钟区域的最大跃点数量会增加。

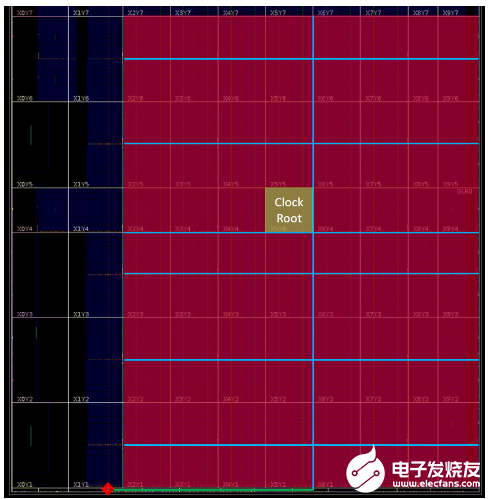

将时钟根移至 X5Y4 会选择更偏向中心的 VNOC 列用于时钟布线,从而减少跃点数量并提高 FMAX。 在时钟网络的 FMAX 计算中,不会计入从 BUFGCE 穿过 XPIO 时钟区域到 VNOC 的时钟布线。

审核编辑:汤梓红

-

时钟

+关注

关注

10文章

1733浏览量

131446 -

布线

+关注

关注

9文章

771浏览量

84322 -

DRC

+关注

关注

2文章

148浏览量

36158

发布评论请先 登录

相关推荐

贸泽电子开始备货Maxim Integrated的多种适用于医疗耗材的安全器件

适用于STM32芯片的开发教程

适用于家电应用的优化参考设计

适用于PDA的PLC编程系统开发

USB标准适用于哪些应用

适用于节能家电的创新功率转换器件

英飞凌推出适用于节能家电的创新功率转换器件

适用于Arduino的Adafruit NeoPixel Shield

适用于SSIT器件的Versal Fmax限制

适用于SSIT器件的Versal Fmax限制

评论