典型设计应该不会出现时序违例。多 bank 设计更容易受此问题影响。

对于多 bank 接口配置,如果单个 bank 同时具有 RX 和 TX,并且其中序列化因子不同,或者如果在“Advanced”选项卡上使用了 enable_all_ports,则可能发生此问题。

在 2021.1 版的 Advanced IO Wizard 中为 PLL 提供了经过更新的去歪斜电路,此更新可解决大部分时序违例。

如果仍发生违例,请考虑手动调整时钟的 PHASE 属性,直至解决违例为止。

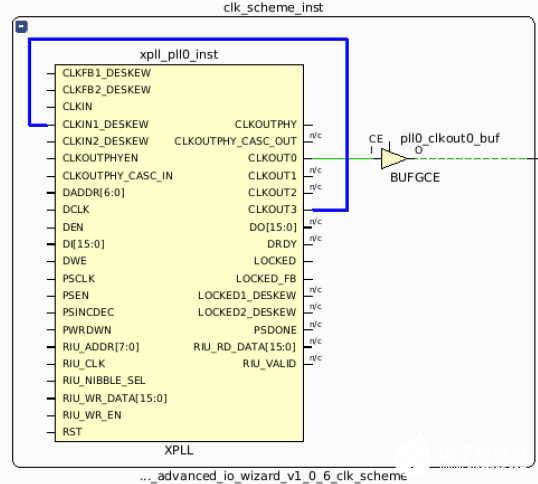

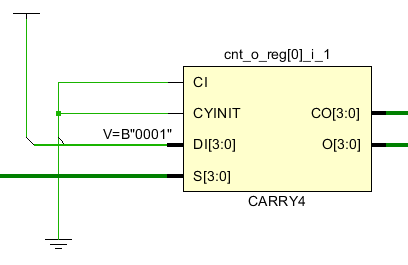

XPLL 的 CLKIN_DESKEW 连接到 XPLL 的 CLKOUT3(XPLL 将设置为使 CLKOUT3 频率 = CLKIN 频率)。

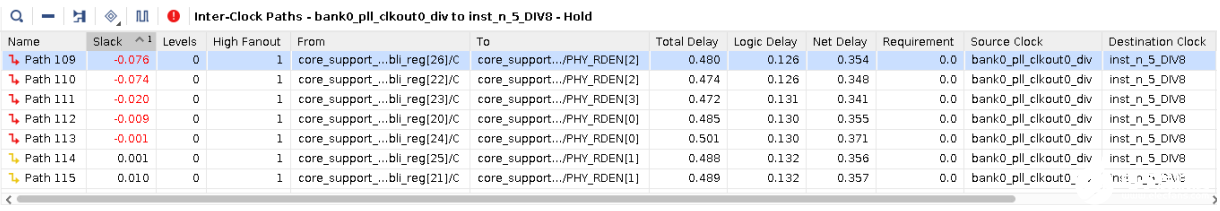

在以下示例中,到 PHY_RDEN 的路径上存在保持时间违例,最差情况下保持时间为 0.076 ns。

您可使用以下 Tcl 命令来计算 CLKOUT3 的相移,以解决此保持时间问题,然后对该路径进行定时:

set XPLL [get_cells >]

set THSviolation 0.076

set existingPhaseShift [get_property CLKOUT3_PHASE $XPLL]

set clkout3_divide [get_property CLKOUT3_DIVIDE $XPLL]

set c_stepsize [expr 45.0/$clkout3_divide]

set phaseAdjust [expr {$THSviolation / [get_property PERIOD [get_clocks -of [get_pins -of $XPLL -filter REF_PIN_NAME=~CLKOUT3]]] * 360}]

set updatedPhaseShift [expr {$existingPhaseShift + $phaseAdjust}]

set c_phase_rounded [format %.3f [expr $c_stepsize * round($updatedPhaseShift/$c_stepsize)]]

set c_phase_rounded_margin [format %.3f [expr $c_phase_rounded + $c_stepsize]]

set_property CLKOUT3_PHASE $c_phase_rounded_margin $XPLL

report_timing -from [get_pins {design_1_i/advanced_io_wizard_0/inst/design_1_advanced_io_wizard_0_0_phy_i/inst/phy_rden_int_bli_reg[*]/C}] -to [get_pins design_1_i/advanced_io_wizard_0/inst/design_1_advanced_io_wizard_0_0_phy_i/inst/BANK_WRAPPER_INST0/NIBBLE[1].UNISIM.I_XPHY/PHY_RDEN[*]]

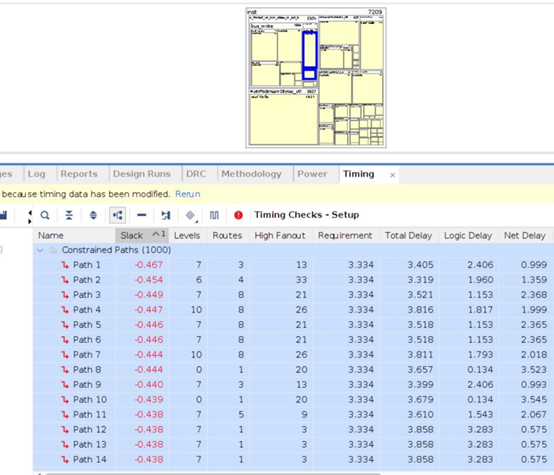

同样,您也可使用以下 Tcl 命令来计算 CLKOUT3 的新相移,以解决此建立时间违例,然后对该路径进行定时:

set XPLL [get_cells >]

set WNSviolation 0.076

set existingPhaseShift [get_property CLKOUT3_PHASE $XPLL]

set clkout3_divide [get_property CLKOUT3_DIVIDE $XPLL]

set c_stepsize [expr 45.0/$clkout3_divide]

set phaseAdjust [expr {$WNSviolation / [get_property PERIOD [get_clocks -of [get_pins -of $XPLL -filter REF_PIN_NAME=~CLKOUT3]]] * 360}]

set updatedPhaseShift [expr {$existingPhaseShift - $phaseAdjust}]

set c_phase_rounded [format %.3f [expr $c_stepsize * round($updatedPhaseShift/$c_stepsize)]]

set c_phase_rounded_margin [format %.3f [expr $c_phase_rounded - $c_stepsize]]

set_property CLKOUT3_PHASE $c_phase_rounded_margin $XPLL

report_timing -from [get_pins {design_1_i/advanced_io_wizard_0/inst/design_1_advanced_io_wizard_0_0_phy_i/inst/phy_rden_int_bli_reg[*]/C}] -to [get_pins design_1_i/advanced_io_wizard_0/inst/design_1_advanced_io_wizard_0_0_phy_i/inst/BANK_WRAPPER_INST0/NIBBLE[1].UNISIM.I_XPHY/PHY_RDEN[*]]

如果 Advanced IO Wizard 有多个实例(如有其它 IP 使用此 Wizard,例如 SGMII,那也计算在内),那么在某些情况下,此 Tcl 脚本可以解决 PHY_RDEN 上的保持时间问题,但会在 PHY_WREN 路径上引发建立时间问题。

2022.2 版及更低版本的 Advanced IO Wizard 默认在 PHY_WREN 路径上不使用 BLI 寄存器。如果使用该脚本解决保持时间问题导致 PHY_WREN 出现建立时间问题,请为 PHY_WREN 设置 BLI = TRUE,这样即可帮助解决此问题。

在 XDC 文件中应用下列约束,然后重新运行实现。

set_property BLI TRUE [get_cells -hierarchical phy_wren_bli_temp_*]

审核编辑:汤梓红

-

接口

+关注

关注

33文章

8585浏览量

151077 -

pll

+关注

关注

6文章

776浏览量

135144 -

时序

+关注

关注

5文章

387浏览量

37324 -

Versal

+关注

关注

1文章

158浏览量

7661

发布评论请先 登录

相关推荐

UltraFast设计方法时序收敛快捷参考指南

FPGA时序收敛学习报告

基于MCMM技术IC时序收敛的快速实现

FPGA设计的“三个代表”:Ultrafastdesign methodology

FPGA中IO口的时序分析详细说明

从已布线设计中提取模块用于评估时序收敛就绪状态

UltraFast设计方法时序收敛快捷参考指南(UG1292)

Versal Advanced IO Wizard-部分配置存在时序收敛问题

Versal Advanced IO Wizard-部分配置存在时序收敛问题

评论