如果您已经在使用全新速度文件运行时序,而且 OSERDES CLK 和 CLKDIV 或者 IDDR CLK 和 CLK_B 之间有歪斜违规,接下来帮助解决歪斜违规问题的步骤已在本答复记录中归档。

提供几个解决方案:

推荐的解决方案:将您的项目迁移至 Vivado 2016.4,将时钟拓扑更新至本答复记录所描述的推荐拓扑并运行正常综合及实现流程。

Vivado 2016.4 可在时序分析中自动报告 OSERDES 和 IDDR 的歪斜检查情况。

第二种解决方案:更新时钟拓扑后为您的项目继续使用较早的 Vivado 版本,包括运行综合及实现方案。 使用本答复记录附带的 Tcl 脚本 (reportIOSERDES.tcl) 报告有关 OSERDES 及 IDDR 的歪斜检查。 使用 Vivado 2016.4 在已布线的 DCP 上运行时序签收 (report_timing_summary),并修复剩余的歪斜违规问题(查看(68266))。

第三种解决方案:升级时钟拓扑后,继续使用带有相应速度文件补丁的较早 Vivado 版本(仅限于某些 Vivado 版本,按需提供),包括运行综合及实现方案。 使用本答复记录附带的 Tcl 脚本 (reportIOSERDES.tcl) 报告有关 OSERDES 及 IDDR 的歪斜检查。

OSERDES CLK 至 CLKDIV 歪斜

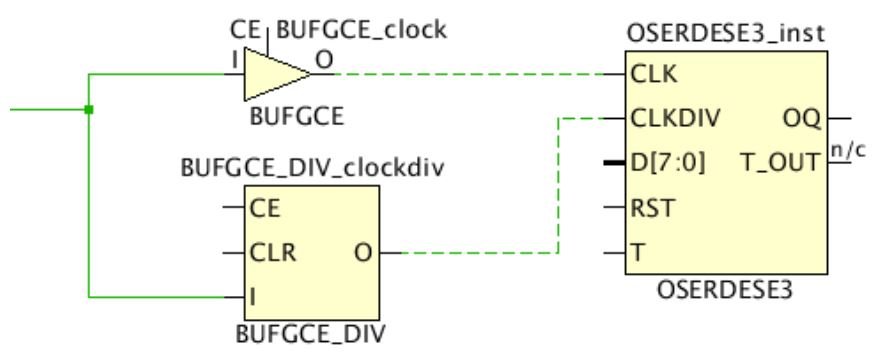

OSERDESE3 的最佳时钟拓扑如下图所示。

MMCME3 的 CLKOUT 应并行驱动两个 BUFGCE_DIV,这可使用一个 BUFGCE_DIV 的分频功能创建较慢的 CLKDIV。

注意,也不一定就需要驱动高速时钟 (CLK) 的全局缓冲器为 BUFGCE_DIV 单元。如果缺乏 BUFGCE_DIV,它也可以是 BUFGCE。

使用 MMCME3 的多组输出创建 CLK 和 CLKDIV 时,请查看确保符合歪斜要求。

图:推荐的时钟拓扑

请注意:因为 BUFGCE_DIV 正在使用被下分频的较高频率时钟。

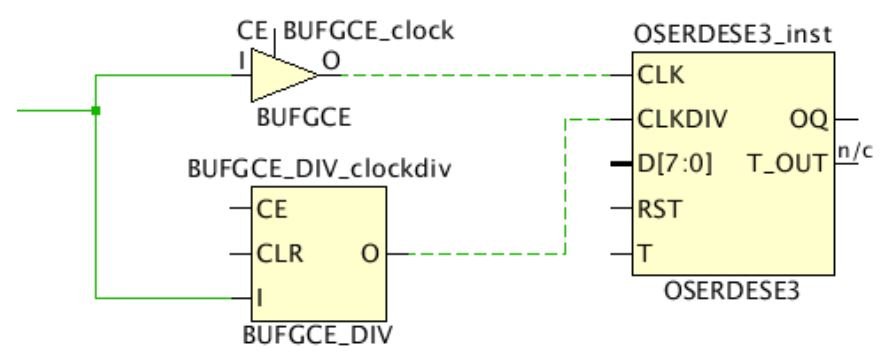

因此,架构逻辑必须使用图(支持 BUFGCE_DIV 的架构时钟)中所示的 BUFGCE_DIV 驱动。

图:支持 BUFGCE_DIV 的架构时钟

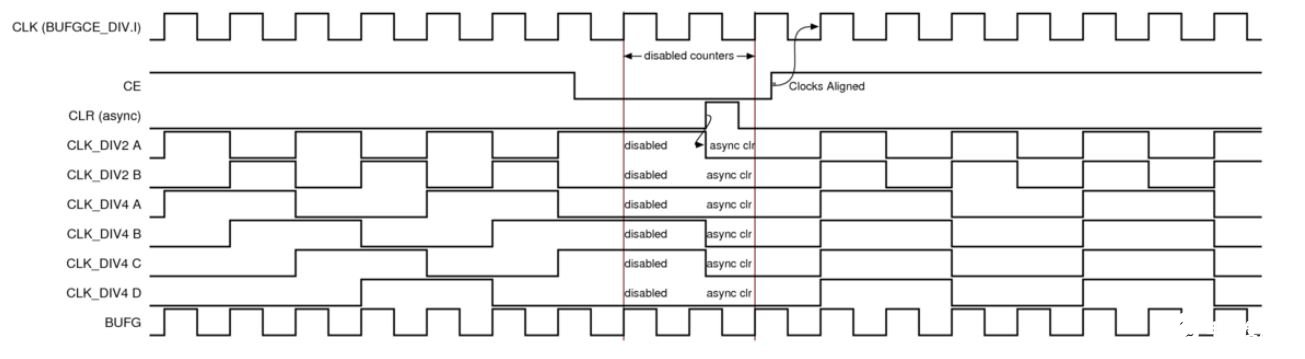

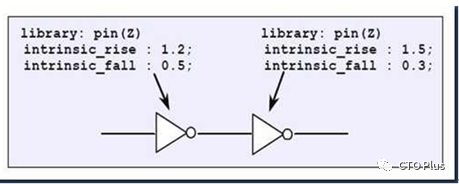

如图所示:BUFGCE_DIV 对齐,BUFGCE_DIVIDE = 2 或者 4 个计数器可以在不同的时间启动。

CLK_DIV2 A 和 CLK_DIV2 B 进行 2 分频时出现了两个对齐。同样,进行 4 分频时,CLK_DIV4 A/B/C/D 出现了 4 个可能的对齐。

计数器可通过使用 CLR 和 CE 输入与既定的时钟边缘对齐。

图:BUFGCE_DIV 对齐

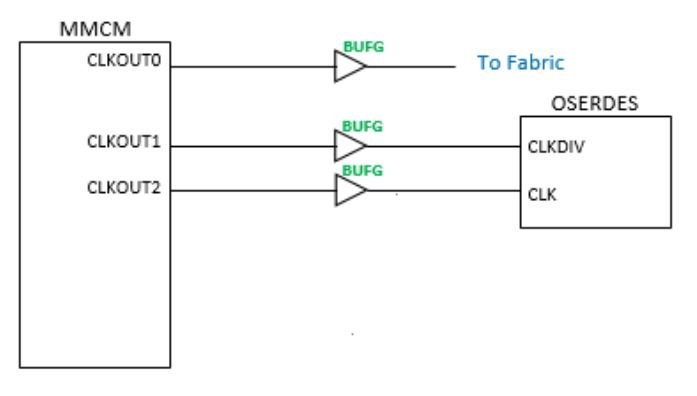

此外,如果您需要 MMCM 输出为相位对齐(就是 CLKOUTx_PHASE)而且无法应用 correctcontrols 控制图(BUFGCE_DIV 对齐)的时序,您可以使用 aseparate BUFG 时钟缓冲器进行架构连接。

在支持 MMCM 时钟输出的架构时钟使用 3 个 MMCM 输出的图中。CLKOUT0 可驱动架构逻辑(另外一个 MMCM CLKOUT1)来驱动 OSERDES CLKDIV 并驱动另外一个 MMCM CLKOUT2 来驱动 OSERDES CLK。

OSERDES 的 CLK 及 CLKDIV 端口由只连接至 ERDES 的 BUFG 驱动,将具有类似的加载/布线。此外,只要布线终点类似,CLKOUT1 和 CLKOUT2 也可用于其它组件原语(ISERDES、IDELAY、ODELAY、IDELAYCTRL)。

图:支持 MMCM 时钟输出的架构时钟

在 支持 MMCM 时钟输出的架构时钟图中, 时钟输出分频设置将是 DATA_WIDTH 的比率,这样:

CLKOUT0_DIVIDE_F = CLKOUT2_DIVIDE * DATA_WIDTH / 2

CLKOUT1_DIVIDE = CLKOUT2_DIVIDE * DATA_WIDTH / 2

输出来自 MMCM,因此实现既定相移时,MMCM 只会锁死,在这种情况下可以由 CLKOUT__PHASE 定义。

CLOCK_DELAY_GROUP

如果设计仍然无法满足要求,下一步就得尝试减少 CLK 与 CLKDIV 引脚之间的歪斜,将一个 CLOCK_DELAY_GROUP 分配给网络。

这可让 Vivado 实现工具平衡两个时钟网络。下面是 CLOCK_DELAY_GROUP 的一个示例:

set_property CLOCK_DELAY_GROUP SERDES_X2Y2 [get_nets of [get_pins BUFGCE_DIV_clk_inst/O]]

set_property CLOCK_DELAY_GROUP SERDES_X2Y2 [get_nets of [get_pins BUFGCE_DIV_clkdiv_inst/O]]

USER_CLOCK_ROOT

除了 CLOCK_DELAY_GROUP 属性外,您还可使用 USER_CLOCK_ROOT 属性强制对时钟缓冲器驱动的时钟进行时钟根定位。查看以下 USER_CLOCK_ROOT 示例:

set_property USER_CLOCK_ROOT X2Y3 [get_nets of [get_pins BUFGCE_DIV_clk_inst/O]]

set_property USER_CLOCK_ROOT X2Y3 [get_nets of [get_pins BUFGCE_DIV_clkdiv_inst/O]]

ISERDES CLK 至 CLKDIV 歪斜:

对 ISERDES CLK 和 CLKDIV 没有歪斜要求,但就 OSERDES 而言,所推荐的时钟拓扑将是相同的。

使用一个并列驱动两个 BUFGCE_DIV 的 MMCM CLKOUT,这可使用一个 BUFGCE_DIV 的分频功能创建更慢的 CLKDIV。

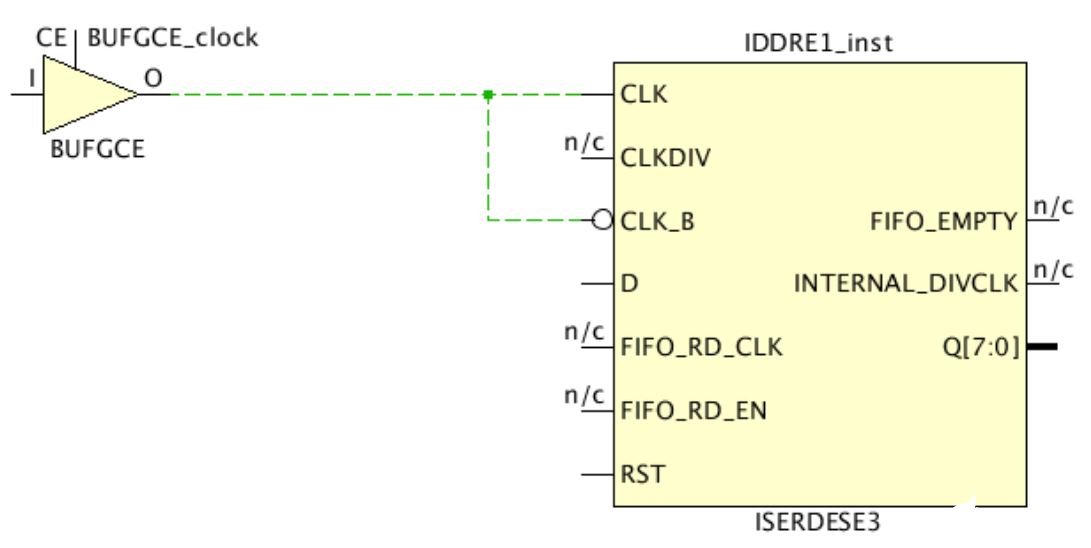

IDDRE1 C 至 CB 以及 ISERDES CLK 至 CLK_B 歪斜

IDDR(和 ISERDES)CLK 和 CLK_B 的最佳时钟拓扑就是使用相同的网络驱动两个引脚并使用局部求逆创建反相时钟。查看下图示例。

查看(68331),了解有关 Vivado 时序歪斜检查的详细信息,解决有关专属时钟组约束的歪斜检查问题。

审核编辑:汤梓红

-

缓冲器

+关注

关注

6文章

2000浏览量

45775 -

计数器

+关注

关注

32文章

2276浏览量

95263 -

时钟

+关注

关注

11文章

1750浏览量

131989 -

Vivado

+关注

关注

19文章

816浏览量

67054

发布评论请先 登录

相关推荐

基于LM12CLK的100W音频放大器电路图

FPGA设计之Verilog中clk为什么要用posedge而不用negedge?

如何应用CLK和RSTn?

clk的延时函数最小延时是多少?

AD9515的CLK与CLKB这两个引脚接差分时钟时哪个接CLK+,哪个接CLK-?

时钟抖动(CLK)和相位噪声之间的转换

CLK233型金属化聚酯薄膜电容器

使用51单片机实现ADC0808A-D虚拟CLK的仿真文件免费下载

使用51单片机实现ADC0808查询方式AD ALE输出CLK的仿真文件

STM8L151C8单片机学习例程(2)——CLK切换

CLK-104a/b 板使用 Renesas RF-PLL 和 RF-Synthesizer 解决方案手册

CLK-104a/b 板使用 Renesas RF-PLL 和 RF-Synthesizer 解决方案手册

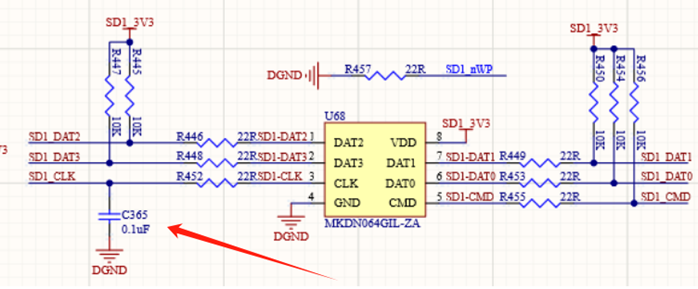

SD NAND的CLK引脚的注意事项和走线规范

如何减少OSERDES的CLK-CLKDIV与IDDR的CLK及CLK-CLK_B之间的歪斜

如何减少OSERDES的CLK-CLKDIV与IDDR的CLK及CLK-CLK_B之间的歪斜

评论