半导体的先进封装为克服阻碍高性能计算应用程序的内存访问障碍提供了机会。在数据中心和边缘运行的技术,如 AI 和视觉,具有与之相关的巨大内存和计算要求,内存的延迟和密度都是可以在封装级别解决的挑战。

为了克服这些挑战,半导体封装设计人员采用了异构集成路线,以在更靠近处理器的位置包含更多内存。而高带宽内存就为现代处理器和嵌入式系统当前面临的内存障碍问题提供了解决方案。这些存储器为系统设计人员提供了两个优势:一是减少组件占用空间和外部存储器要求;二是更快的内存访问时间和速率。

由于这些优势,预计会看到更多更先进的处理器在封装和模块中包含更多的高带宽内存。

查看标准组件数据表(例如,微控制器和 MPU)和计算机/服务器 CPU,您会发现大量具有片上/封装内存的组件。组件封装中使用了许多不同的存储器,其中闪存最为常见。经常看到中等大小的片上或封装内闪存块用于存储小型二进制文件或嵌入式应用程序的配置设置。较旧的封装中可能还包含少量同步随机存取存储器 (SRAM) 或动态随机存取存储器 (DRAM);许多流行的微控制器都将片上 SRAM 作为标准功能。

因此,为了增加高性能计算系统的内存容量,半导体制造商在其 CPU 封装中包括 3D 堆叠 DRAM 小芯片以及处理器核心硅片。就在去年(2022 年),AMD在面向数据中心基础设施的产品中推出了第一批带有堆叠DRAM 和 SRAM芯片的服务器 CPU。随着越来越多的公司完善该技术,预计会有更多产品包含这些 DRAM 堆栈,它们通过高带宽内存 (HBM) 接口与内核通信。

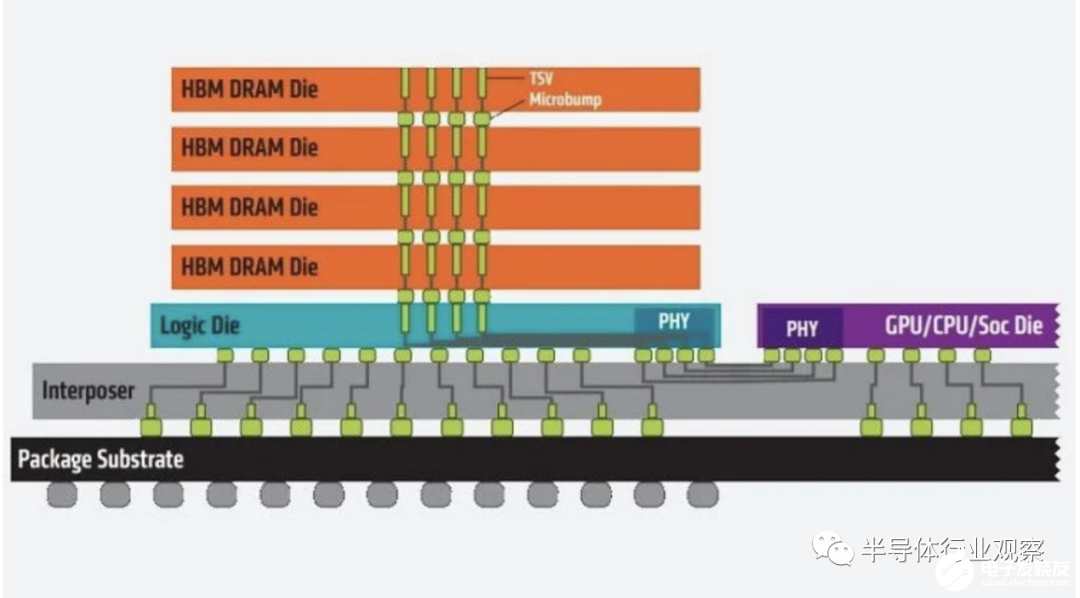

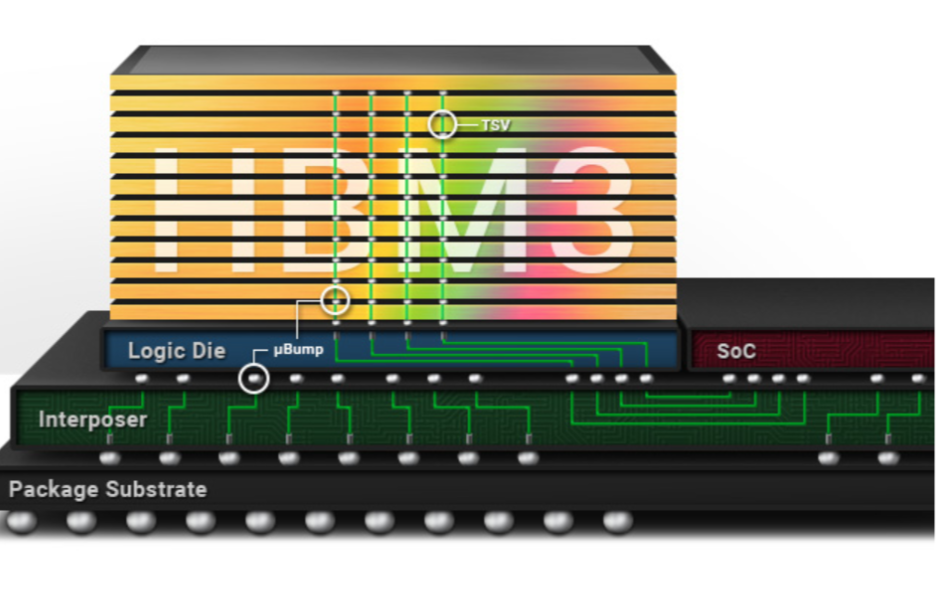

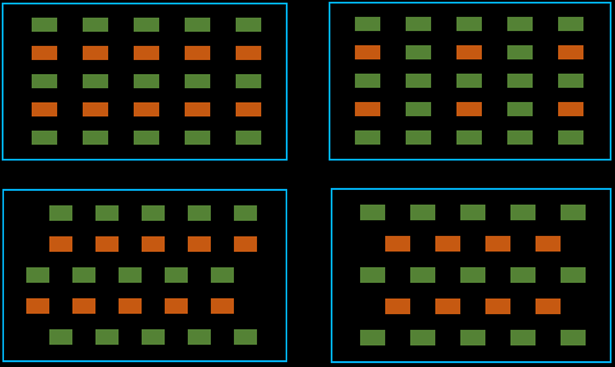

下图显示了典型的异构集成封装中的典型堆叠 DRAM 结构。堆栈 DRAM 位于基板/中介层堆栈上,线路通过这些线路连接到 CPU,以提供所需的内存接口。这些 DRAM 芯片与垂直硅通孔 (TSV) 连接,以提供返回到中介层并最终返回到内核所需的连接。

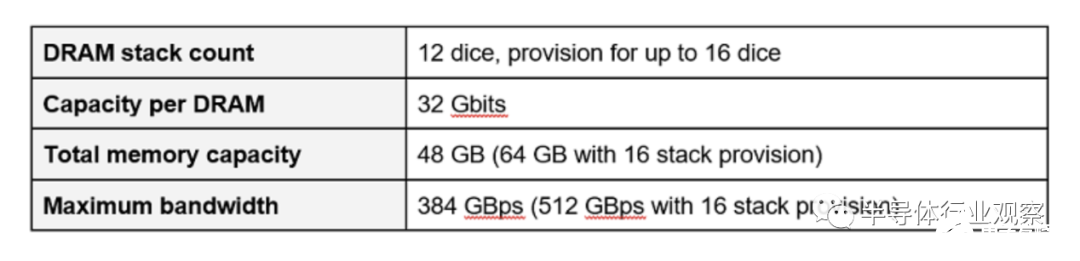

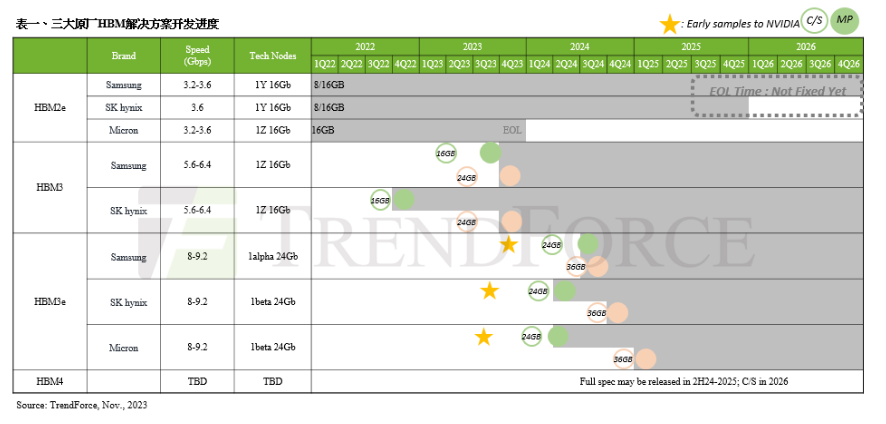

目前,由 JEDEC 发布的 HBM3 标准是 HBM 结构特性和性能的管理标准。HBM3 标准中的一些规定总结如下。

用于构建 DRAM 堆栈的技术最初是为图形处理器开发的,但它已经扩展到内存以实现上表所示的超高带宽。

与其他 JEDEC RAM 类型的比较,总的来说,JEDEC 定义了三种其他类型的 RAM,它们不同于 HBM 并且出现在处理器封装之外:

双倍数据速率 (DDR) — 用于计算机、笔记本电脑的标准 RAM

图形 DDR (GDDR) — 用于 GPU 中的板载内存

低功耗 DDR (LPDDR) — 主要用于移动设备(手机、平板电脑)

最近的趋势继续将这些新一代 RAM 推向更快的时钟速度,以便可以不断提高数据传输速率。这些存储器的前几代面临的挑战是,这是获得高数据传输速率的唯一途径,因为总线宽度非常窄。HBM 不是这种情况;HBM 中的总线宽度非常宽,因此内存接口可以以较低的速率运行,但仍能在宽总线上提供极快的数据传输。这是将 HBM与其他 DDR 区分开来的主要操作因素之一。

对于嵌入式系统设计师、嵌入式计算模块设计师、封装设计师和相关领域的许多其他芯片设计师来说,则可以从采用 HBM 的处理器中获益匪浅。最大的好处是通过消除主板上的外部存储芯片来减小系统尺寸。目前 3D 堆叠 DRAM 的成本相当高,但随着这些组件市场的发展和工艺的进步,预计价格将比标准 RAM 选项更具竞争力。

将内存模块放置在封装中的另一个好处是减少了高计算处理操作所需的时间。这是抑制视觉等领域大型数据集实时处理的主要因素。每次必须从外部存储器获取数据时,处理时间都会增加。将处理和内存放在同一个包中消除了这个障碍并实现了更快的计算。

在数据中心之外需要这些类型的组件的一些现代系统包括机器人技术、高级驾驶辅助系统、成像雷达、传感器与视觉融合、高性能计算。

在这五个应用领域列表中,针对前四个领域的系统正在为实时系统构建,这需要 HBM 可以提供的极低处理延迟。

审核编辑:汤梓红

-

DRAM

+关注

关注

40文章

2315浏览量

183510 -

存储器

+关注

关注

38文章

7492浏览量

163856 -

嵌入式系统

+关注

关注

41文章

3593浏览量

129484 -

HBM

+关注

关注

0文章

380浏览量

14761

发布评论请先 登录

相关推荐

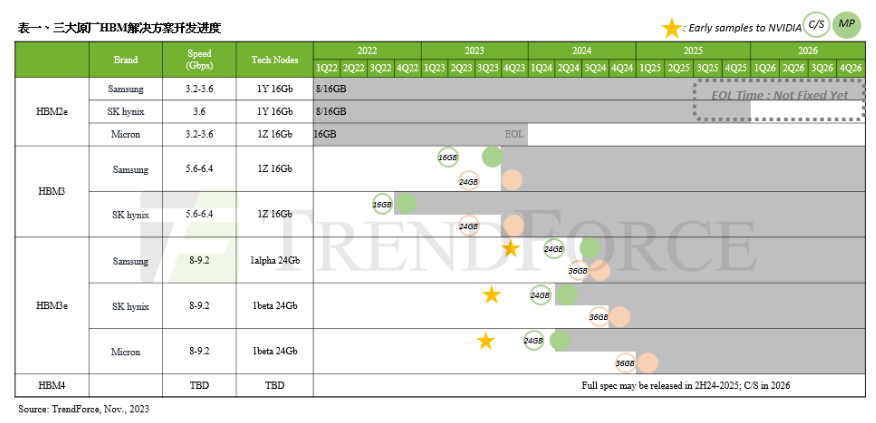

还没用上HBM2E?HBM3要来了

追求性能提升 使用8GB HBM2显存

HBM称重传感器的运用知识

HBM传感器的安装

半导体测试HBM了解一下~

HBM产品在电机测试中的使用情况

使用带HBM芯片有哪些要注意的地方

ChatGPT带旺HBM存储

预计英伟达将于Q1完成HBM3e验证 2026年HBM4将推出

英伟达将于Q1完成HBM3e验证 2026年HBM4将推出

HBM、HBM2、HBM3和HBM3e技术对比

为什么需要HBM?

为什么需要HBM?

评论