76889 - Versal HDIO/MIO:以 3.3V 或 2.5V 上电时,如果使用三态,则在数据与三态之间可能存在争用条件是一篇面向 Versal ACAP 的设计咨询,其中详述了三态控制发生更改时的 MIO 要求和 HDIO 要求。

本文则着重探讨 JTAG TDO 用例。

如果 VCCO_503 为 3.3V 或 2.5V,那么三态数据争用条件可能会影响 JTAG TDO_503。

由此导致 TDO 输出可能无法驱动可编程逻辑 (PL) 的 LSB 位的“1”值。此问题不影响处理子系统 (PS) Arm DAP 和 PL BYPASS 数据输出功能特性。

解决方案

您可使用以下选项作为此问题的变通方法:

1) 将 VCCO_503 设为 1.8V。

注释:如果您使用的是 SSIT 器件,请联系赛灵思技术支持。

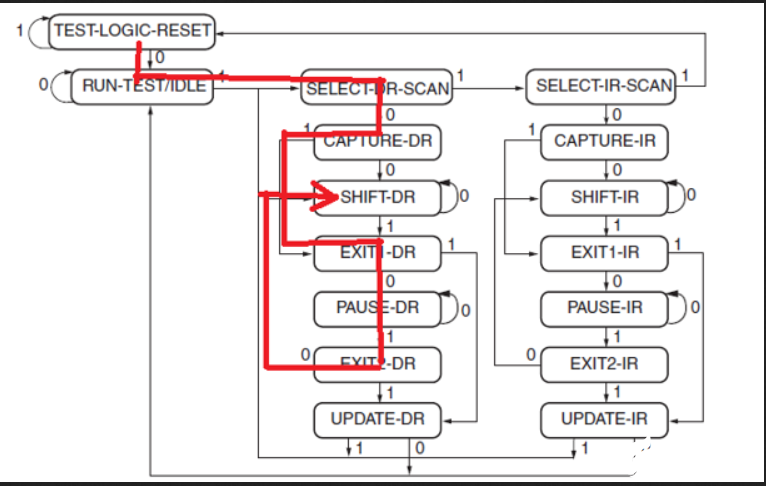

2) 如果 VCCO_503 必须设为 2.5V 或 3.3V,那么可改用备用 TAP 状态路径来进入“Shift IR”(移位指令寄存器)或“Shift DR”(移位数据寄存器)状态,以避免发生此问题,如下图所示。

在 Vivado 2021.2 及后续软件版本中,如果在 JTAG 链中包含 Versal 器件,那么该工具会默认自动检测并使用备用 TAP 状态路径。

在 2021.2 版本及后续软件版本中,用户也可以使用以下命令手动启动 hw_server:

hw_server -e "set jtag-pause-before-shift 2"

在 XSDB 2021.2 及后续软件版本中,使用以下命令“连接”后,必须应用 configparam 命令:

xsdb% configparam jtag-pause-before-shift 2

此备用路径仅显示进入移位 DR 状态。该备用路径应同样用于移位 IR 状态。

以上 configparam 会将此变通方法应用于 Shift-DR 操作和 Shift-IR 操作。

3) 如果 VCCO_503 必须设为 2.5V 或 3.3V,请向您的 JTAG 工具供应商申请采用此备用 TAP 状态路径作为 JTAG 变通方法。

审核编辑:汤梓红

-

寄存器

+关注

关注

31文章

5342浏览量

120271 -

JTAG

+关注

关注

6文章

400浏览量

71676 -

指令

+关注

关注

1文章

607浏览量

35698 -

Versal

+关注

关注

1文章

158浏览量

7660

发布评论请先 登录

相关推荐

简单认识JTAG接口

TDO没有信号切换

哪里可以找到将CC2640 5*5 JTAG TDO 与TDI复用为IO口的资料?

tms320c6416的TCK、TDO、 TDI、TRST、TMS、EMU等能否直接接到JTAG上?

XC2C384是否具有TDO引脚的内部上拉?

在JTAG配置阶段TDO没有给出任何结果是为什么?

S32K-连接失败- JLink日志:无法测量总IR len,TDO恒定高的问题如何解决?

JTAG的原理

jtag工作原理详解

基于S698PM芯片的JTAG控制G接口的设计及应用

Versal:JTAG TDO

Versal:JTAG TDO

评论