1. 技术背景

EtherCAT 是开放的实时以太网通讯协议,由德国倍福自动化有限公司研发。EtherCAT 具有高性能、低成本、容易使用等特点,目前在技业领域有着广泛的应用。

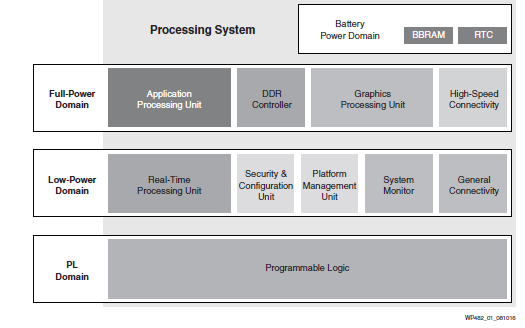

ZCU102 评估套件可帮助设计人员快速启动面向汽车、工业、视频以及通信应用的设计。该套件具有基于 Xilinx 16nm FinFET+ 可编程逻辑架构的 Zynq® UltraScale+™ MPSoC 器件,提供一款四核 ARM® Cortex®-A53、双核 Cortex-R5F 实时处理器以及一款 Mali™-400 MP2 图像处理单元。ZCU102 支持所有可实现各种应用开发的主要外设及接口。

KPA EtherCAT 主站是一套质量稳定、知名度和性价比较高的 EtherCAT 协议栈,有较大参考价值。本文将介绍KPA EtherCAT 主站在ZCU102平台的移植与测试。

2 EtherCAT简介

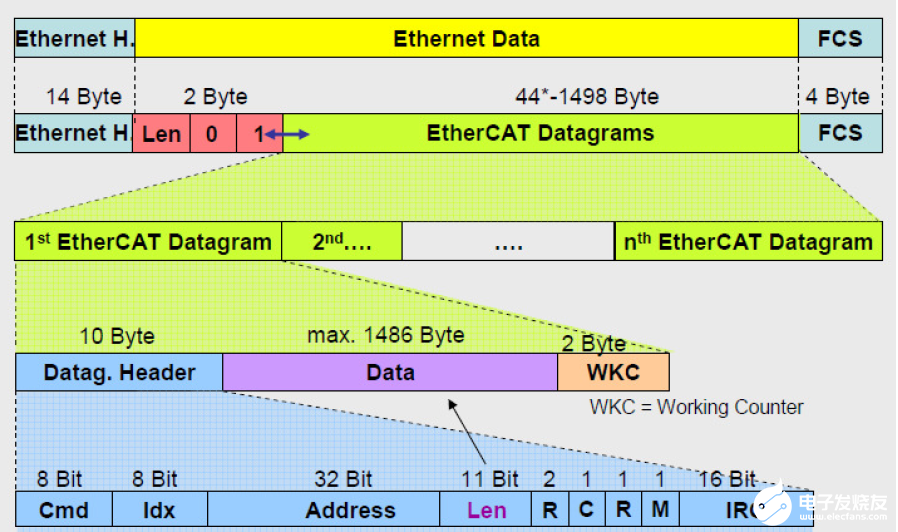

EtherCAT(以太网控制自动化技技)是一种用于确定性以太网的高性能工业通信协议,它扩展了 IEEE 802.3 以太网标准,使得数据传输中具有可预测性定时及高精度同步等特点。这个开放性标 准作为 IEC 61158 的组成部分,常用于机械设计及运动控制等应用中。EtherCAT 采用标准的 IEEE802-3 以太网帧,帧结构如图 1。EtherCAT 协议直接用标准以太网的帧格式传输数据,并不修改其基本结构。

EtherCAT 实现了 CANopen 协议,在 CANopen 中周期性的数据通过 PDO(过程数据对象)来传输,PDO 优先级较高,可用于实时传输。非周期性的数据比如配置参数和对象字典等则通过 SDO(服务数据对象)来传输。

每个 PDO 都包含单个或多个从设备的地址,这种数据加地址的结构(附带用于校验的传输计数位)组成了 EtherCAT 的报文。每个 Ethernet 帧可能包含数个报文,而一个周期中可能需要多帧来传送所需的所有报文。

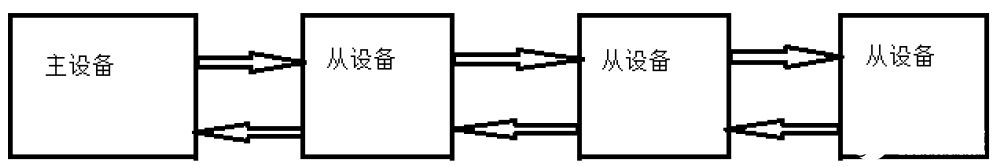

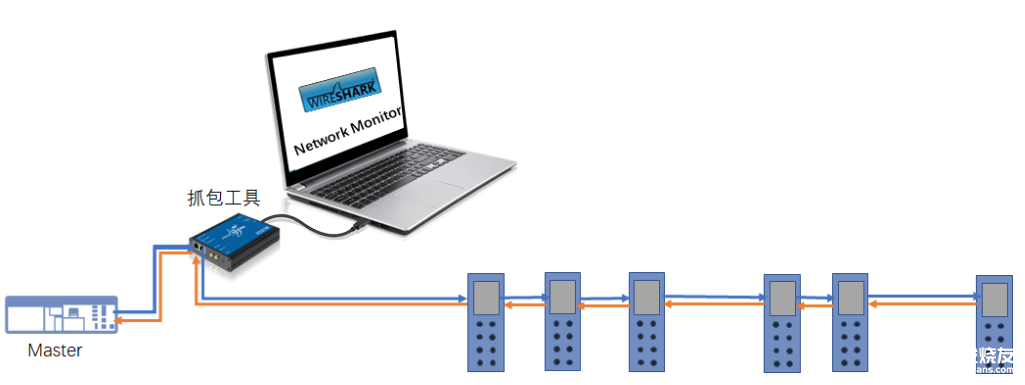

传统的以太网通信解决方案从站先接受以太网数据包,然后解释和复制过程数据,最后转发数据。而EtherCAT 以太网帧在特殊的硬件模块的帮助下可以实现在传输的同时被处理。每个从节点都有 FMMU(现场总线存储管理单元),FMMU 会对经过的数据包进行地址分析,发现是本节点的 数据就会读取,同时报文转发给下一个设备。同样在报文通过的时候也可以插入需要传输的数据。读取/插入/转发数据的整个过程,报文只有几纳秒的延迟。如图 2 所示,设想以太网的帧就像行驶中的火车,EtherCAT 报文是每节火车车厢,PDO 数据的比特就是车厢内的乘客,这些数据可以被提取并插入到合适的从设备中。整辆火车不停止地穿越所有从设备,在末端从设备处又掉头,重新反向穿越所有从设备。(注:EtherCAT不仅支持主从通讯,也支持从从通讯即S2S)

2.1 KPA EtherCAT主站软件介绍

KPA EtherCAT主站软件根据功能不同,提供了Basic,Standard,Premium以及Extension四个版本主站协议栈,因此除了支持ETG1500定义了Class A和Class B两种主站类型外,KPA还支持一些拓展功能比如:Data- and Frame-Logger(记录数据和报文)、Access Rights(设置不同的访问权限)Multi Master(多主站,冗余)、Cable Redundancy (线缆冗余)、Hot-Connect(热插拔)、其他。

提供了基于多种不同硬件平台和OS的现成开发包,支持SoC(ARM+FPGA)/ARM/X86 /PowerPC等主流硬件平台,支持Linux(Xenomai/RT-preempt)/ Windows(INtime/RTX)/ QNX/ Ucos/ Vxworks等。几乎满足目前所有用户主站开发要求的一款主站方案。

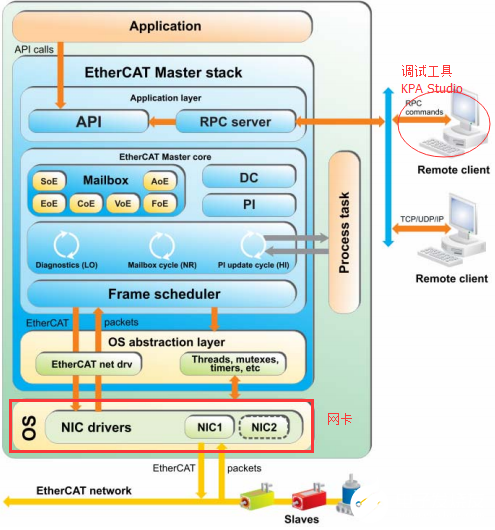

KPA主站协议栈采用模块化的架构,可以实现每个特殊的项目应用。它使得主站可以自由扩展以适应不同大小的应用程序、可以移植不同的操作系统和各种各样的硬件平台。每个模块可以单独定制化或者二次开发,而且不会破坏其他模块的完整性。主站结构如图

KPA主要功能模块为:

(1)应用层:应用层负责与各种不同的编程/配置环境交互,负责与不同的应用或设备交互。确保在应用或过程任务端顺利访问主站功能函数;与主站通过Remote Procedure Calls服务交互,提供了TCP/IP以及UDP连接,比如:通过UDP与从站设备进行mailbox相关的通讯

(2)Mailbox Module:EtherCAT主站核心mailbox模块利用不同的协议处理服务数据对象(SDP),数据传输以及数据交换。支持CoE,FoE,EoE,SoE,VoE,AoE等邮箱服务。

(3)Process Image Module过程映像模块:Process Image简称PI,它的地址是由EtherCAT network information (ENI) 文件提出的,ENI文件可由配置工具KPA Studio自动生成。从控制/过程任务访问过程映像是由主站接口执行的。

(4)Distribution Clock分布时钟模块:使得所有的EtherCAT设备(包括主站和从站)总是能够共享相同的EtherCAT系统时间。这是通过补偿编译和漂移时间来实现的。

(5)Frame Schedule Module帧调度模块:不同PDO采用不同的扫描周期。在配置工具KPA Studio里,用户可以单独定义每个从站的扫描速率。帧调度表模块管理EtherCAT帧速率,转发它们到EtherCAT网络驱动。

(6)OSAL操作系统抽象层模块:包含与操作系统相关的功能函数的包装,比如处理线程、计时器、互斥量等;包括网络适配驱动器模块:从底层的网络实现提取主站堆栈的core核心

2.2 KPA EtherCAT主站硬件介绍

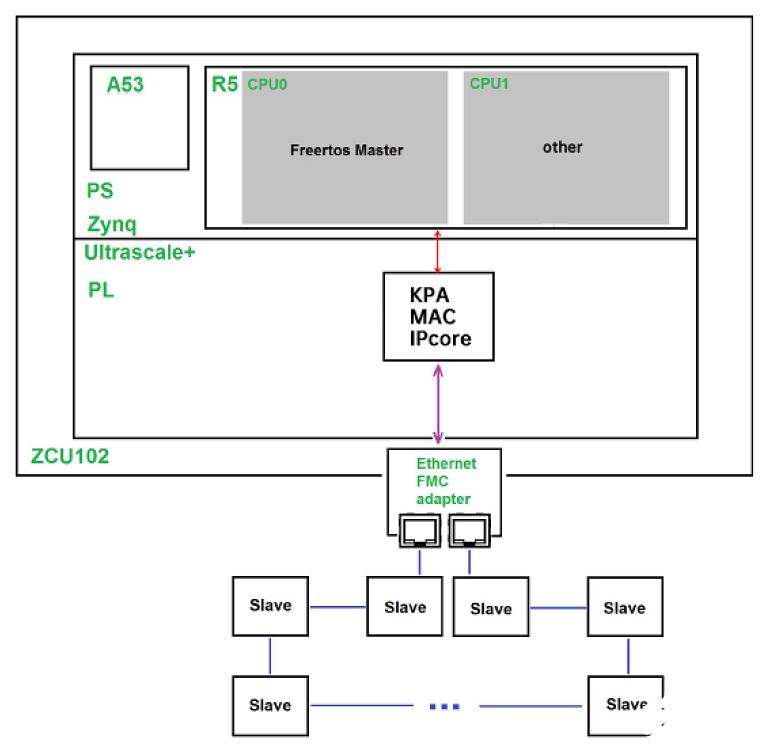

主站硬件主要由三部分组成见下图:ZCU102主站开发板以及外扩的FMC网卡。KPA MAC IPcore在PL端构建了FPGA网卡,FreeRTOS master既可以运行在R5 CPU中也可以运行在A53 CPU中,另外需要一台PC通过串口终端来实现操作系统指令输入,PC端上的EtherCAT网络诊断配置工具KPA EtherCAT Studio通过RPC服务连接ZCU102主站板,可以实现对主站和从站的配置,扫描生成网络配置文件。

2.3 KPA EtherCAT主站移植

2.3.1 硬件开发板

Xilinx HW-Z1-ZCU102 revision1.1

2.3.2 EtherCAT主站软件开发包

MDK_xilinx-2018.3_freertos_a53_trial_v2.4.48714.0-release.zip

HW_SAMPLE_xilinx-2018.3_freertos_a53_trial_v2.4.48714.0-release.zip

2.3.3 软件编译

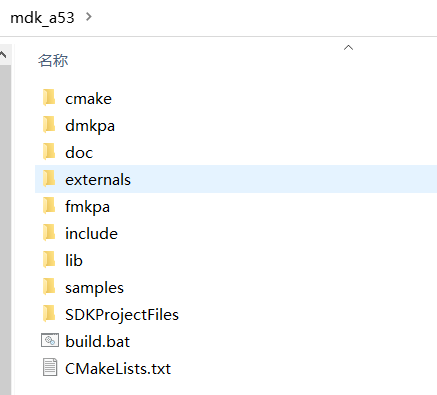

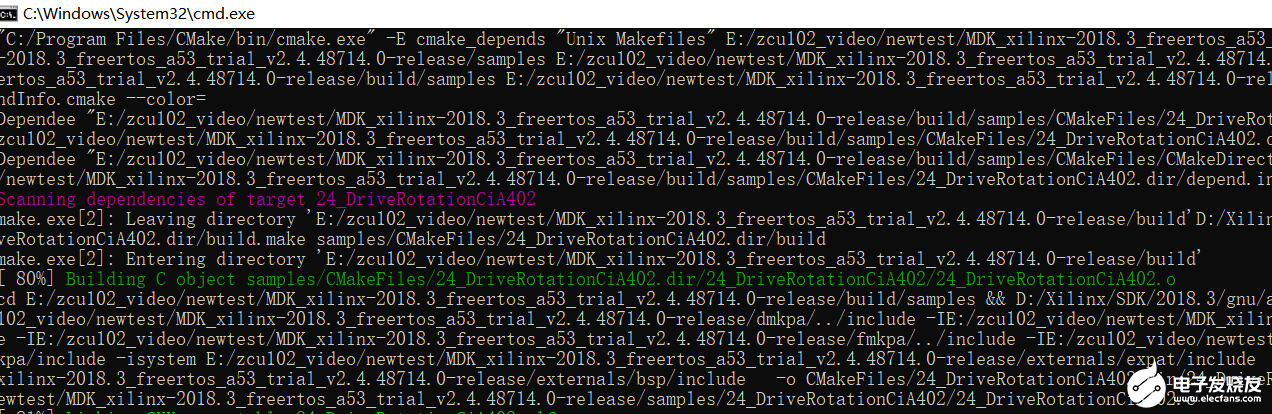

将MDK_xilinx-2018.3_freertos_a53_trial_v2.4.48714.0-release.zip解压到mdk_a53文件夹下

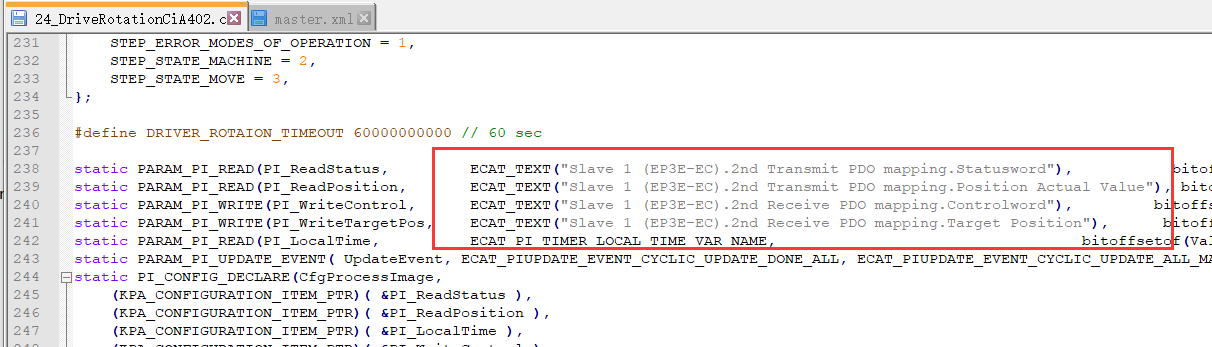

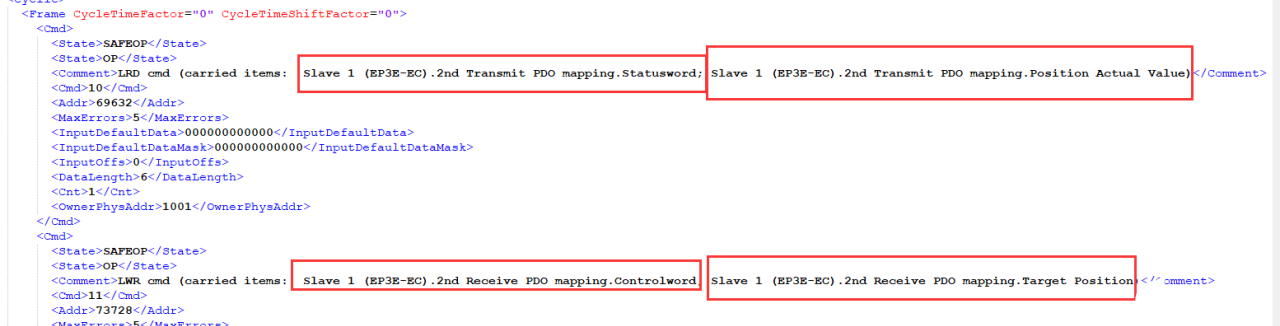

进入mdk_a53samples路径下修改对应样例程序,此处每个不同的样例程序包含不同的API,具有不同的功能,此处以24_DriveRotationCiA402为例,这是一个简单运行单轴伺服的样例程序,为了适配迈信伺服驱动器,需保持C文件中的描述和ENI文件描述一致,修改后保存

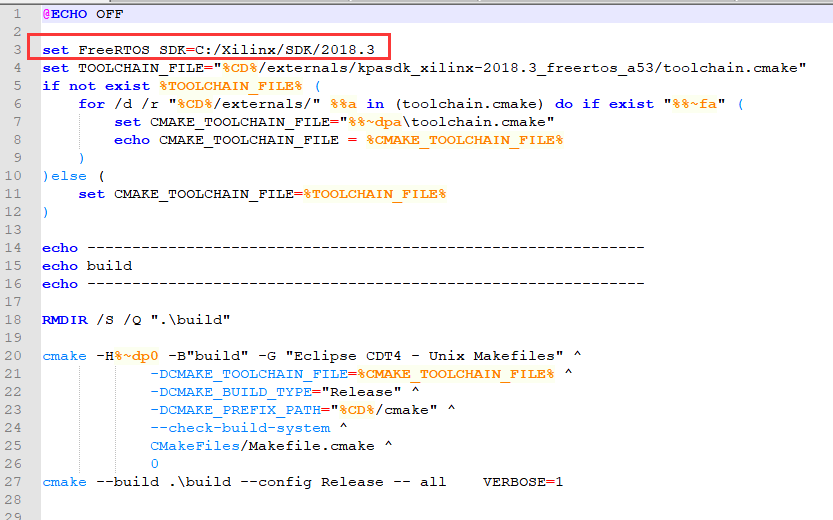

进入mdk_a53下,打开build.bat,修改编译器路径,路径是xilinx SDK安装路径

运行cmd,进入该路径下,运行build.bat,编译所有样例代码,包括编译24样例,在buildsamples路径下生成24_DriveRotationCiA402.elf文件

2.3.4 创建运行程序

2.3.4 创建运行程序

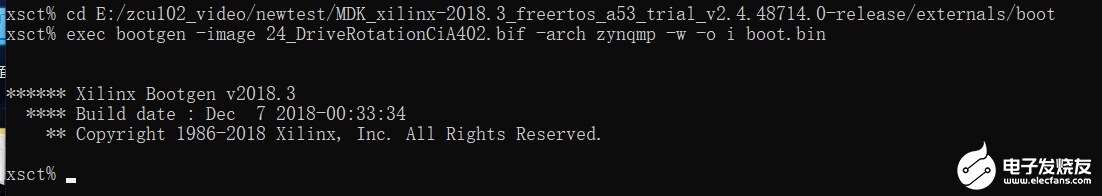

进入mdk_a53externalsboot路径,根据readme文件以及24_DriveRotationCiA402.bif文件;

拷贝zcu102_freeRTOS内vivado工程生成的design_1_wrapper.bit()文件到该路径下,覆盖原来bit文件;

拷贝zcu102_freertosproject_1project_1.sdkfsblRelease下的fsbl.elf到该路径下,覆盖原来fsbl.elf文件;

拷贝buildsamples路径下生成的24_DriveRotationCiA402.elf到该路径下;

拷贝生成的ENI文件(master.xml)文件到该路径下

打开Xilinx XSCT tool进入到externalsboot路径下,生成boot.bin

将boot.bin文件拷贝到SD卡中,设置开发板SD卡启动,上电运行

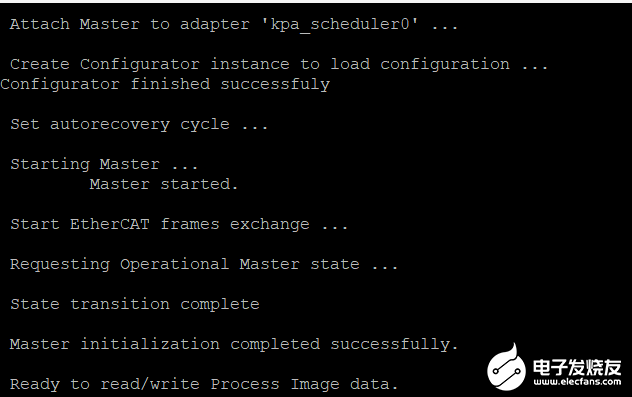

2.4 主站性能数据

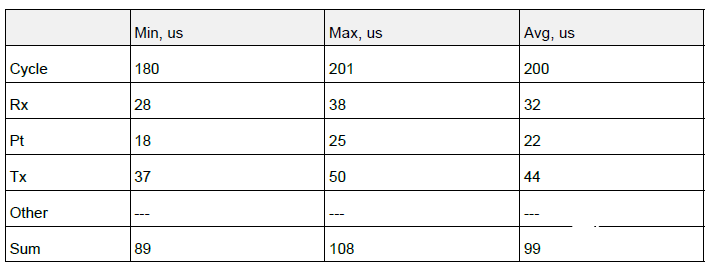

网络配置:Beckhoff EK1100+EL1004+EL2004+EL6692 (60 bytes frame)。

运行在R5 CP(x32)上测试数据:

运行在A53 CPU(x64)上测试数据:

3. 第三方抓包工具性能分析方法

一般情况下EtherCAT主站性能测试会关注主站通讯周期,circle time是否稳定,抖动多少,因此可以设置在不同的circle time,比如2ms,1ms,500us,250us,125us等条件下测试抖动,可以采用第三方的抓包工具+wireshark进行报文分析,不同主站周期,需要修改代码以及ENI文件的circle time,此处以1ms主站周期,邮箱任务周期是5ms(主站周期的5倍)

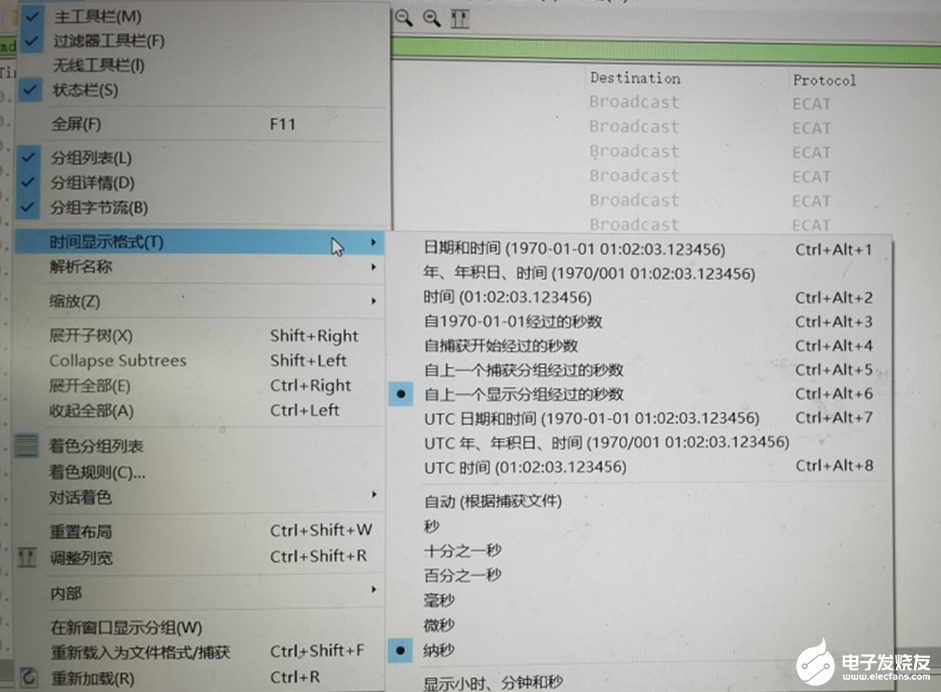

对Wireshark数据包进行针对性分析,设置时间显示格式如下

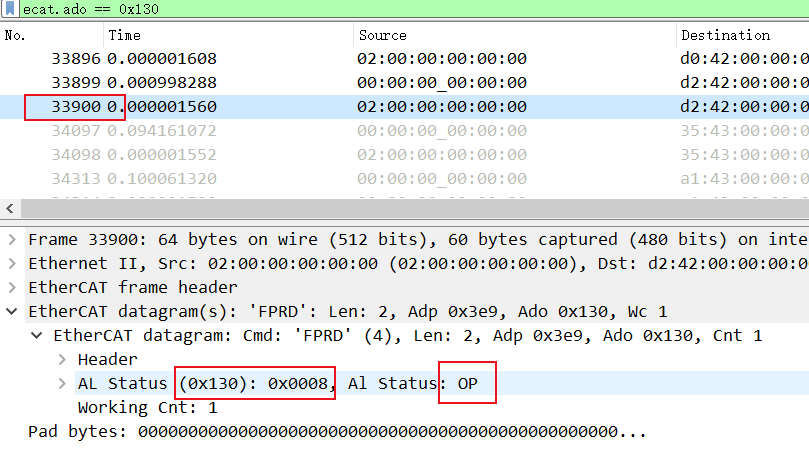

使用ecat.ado == 0x130命令,过滤出从站在第几条报文处进入op状态的,这里是33900,意味着33900前的报文不能用于分析circle time,因为pdo数据/周期性数据只在从站进入op后才被发送

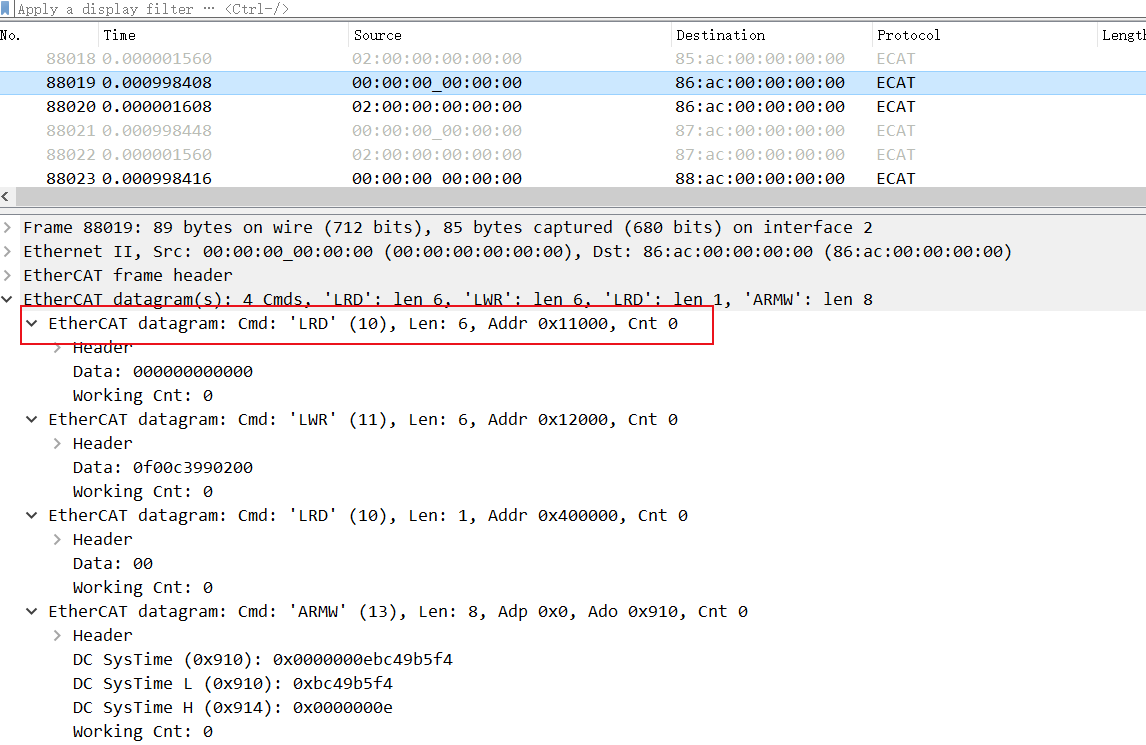

分析周期性报文,注意到每个周期性报文包含三个子报文(逻辑寻址)以及一个DC相关的ARMW命令

过滤出周期性报文,使用该指令ecat.sub1.cmd == LRD && ecat.sub1.cnt == 0,过滤出子报文1为LRD且计算器值为0(表示从主站发出,未经过从站)的周期性报文,选择三角进行报文排序,可以是从小到大,或者从大到小。

最小周期是999.496us

审核编辑:汤梓红

-

以太网

+关注

关注

40文章

5376浏览量

171113 -

Zynq

+关注

关注

9文章

608浏览量

47128 -

ethercat

+关注

关注

18文章

653浏览量

38604 -

MPSoC

+关注

关注

0文章

198浏览量

24252

发布评论请先 登录

相关推荐

如何利用ZYNQ MPSoC玩DOOM?

请问Zynq Ultrascale + MPSOC本身是否存在问题?

如何调试Zynq UltraScale+ MPSoC VCU DDR控制器

开源!ZYNQ IgH EtherCAT主站方案分享

Zynq UltraScale+ MPSoC系列有多少SerDes接口?

Ti推出面向Zynq UltraScale+ MPSoC的电源参考设计

Zynq UltraScale+ MPSoC的发售消息

如何使用Zynq UltraScale和MPSOC管理电源和性能资料说明

如何调试 Zynq UltraScale+ MPSoC VCU DDR 控制器?

米尔电子zynq ultrascale+ mpsoc底板外设资源清单分享

Zynq UltraScale ZU19EG MPSOC评估板

Zynq UltraScale+ MPSoC的隔离设计示例

Zynq UltraScale+MPSoC嵌入式设计教程

基于Zynq UltraScale+MPSoC高性能EtherCAT主站方案

基于Zynq UltraScale+MPSoC高性能EtherCAT主站方案

评论