目前绝大多数的Versal IP所提供的例子工程,都使用了IPI的流程。

这篇blog会给大家介绍如何修改IP例子工程(Block Design)里的IP和GT模块的源代码与属性。这里用的是以太网IP,如MRMAC和DCMAC作为示例。当然这些修改的方法,也适用于其它调用了GT的各种IP。

这篇blog主要包含以下4个方面内容:

1. 使用APB3接口修改GT的参数属性

2. 如何从Block Design的模块内部,获取GT端口信号的控制

3. 通过CIPS读、写以太网IP的寄存器

4. 如何修改IP的内部源代码

首先,产生一个DCMAC或者MRMAC IP的例子工程。

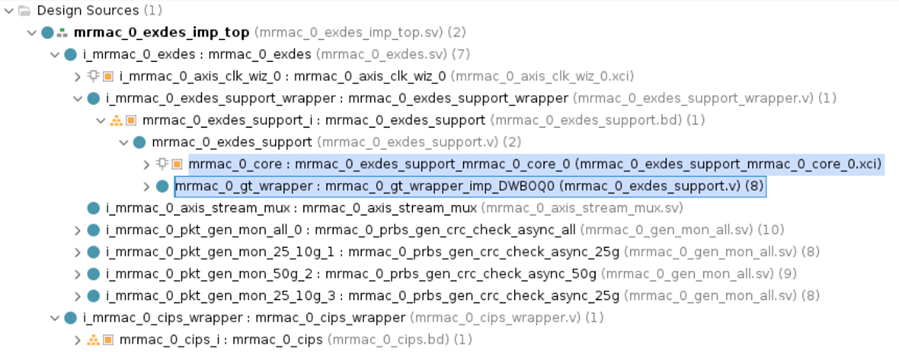

如下图可以看到,IP的例子工程里面有个Block Design(BD)工程,里头包含了MAC core(.xci)和GT wrapper模块。另外,工程里还有个CIPS模块,用来读写寄存器。

1. 使用APB3接口修改GT的参数属性

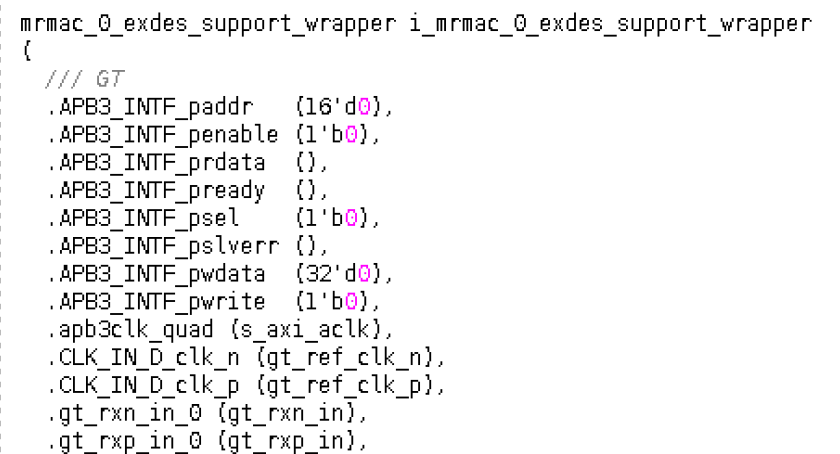

在产生的MRMAC例子工程中,GT的APB3接口是直接拉出来的,但是在代码逻辑里面并没有被使用,如下图,在”*_exdes.sv”文件里可以找到。

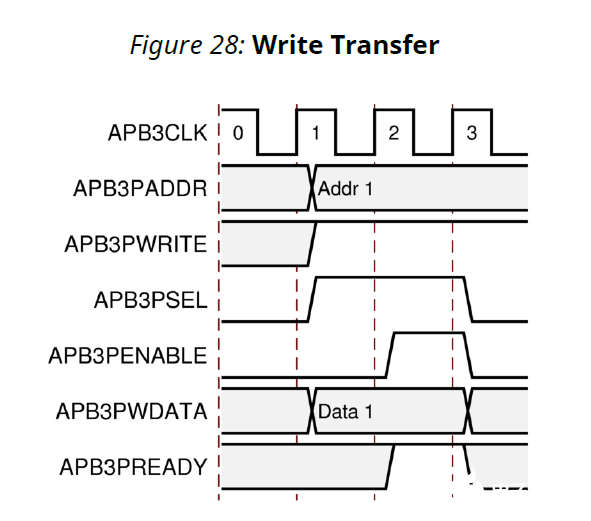

请参考GT用户手册(如GTM的文档AM017)中的章节“Fabric Configuration Interface”,来操作APB3接口。这个新的APB3接口,跟GT以前用的DRP接口非常类似,可以通过该接口,动态读写GT的参数属性。

在另一篇blog“Differences When Designing with UltraScale+ GTY and Versal GTY/GTYP“当中,提供了一个如何使用VIO去控制APB3的例子,可供参考使用。它还提供了另一个例子,使用AXI总线替换APB3接口来操作。

2. 如何从Block Design的模块内部,获取GT端口信号的控制

一个IP core调用了GT模块,但并不一定会用上所有的GT端口管脚。这些端口信号很有可能被留在了Block Design的模块内部,而没有拉到顶层来。但是在有的时候,客户为了自己的设计会想要去控制某些被留在BD内部的GT输入输出端口信号,例如为了做一些debug工作等。

这篇AR“75857 - Versal GTY Pass Through Mode - How do I tie off all of the interface pins/Changes from previous versions of the IP“介绍了如何去获取以及控制内部的GT模块的端口信号。

下面是一个例子,详细描述了如何可以手动把你想要用的GT端口从BD设计内部拉到IP顶层来,供你的逻辑驱动。

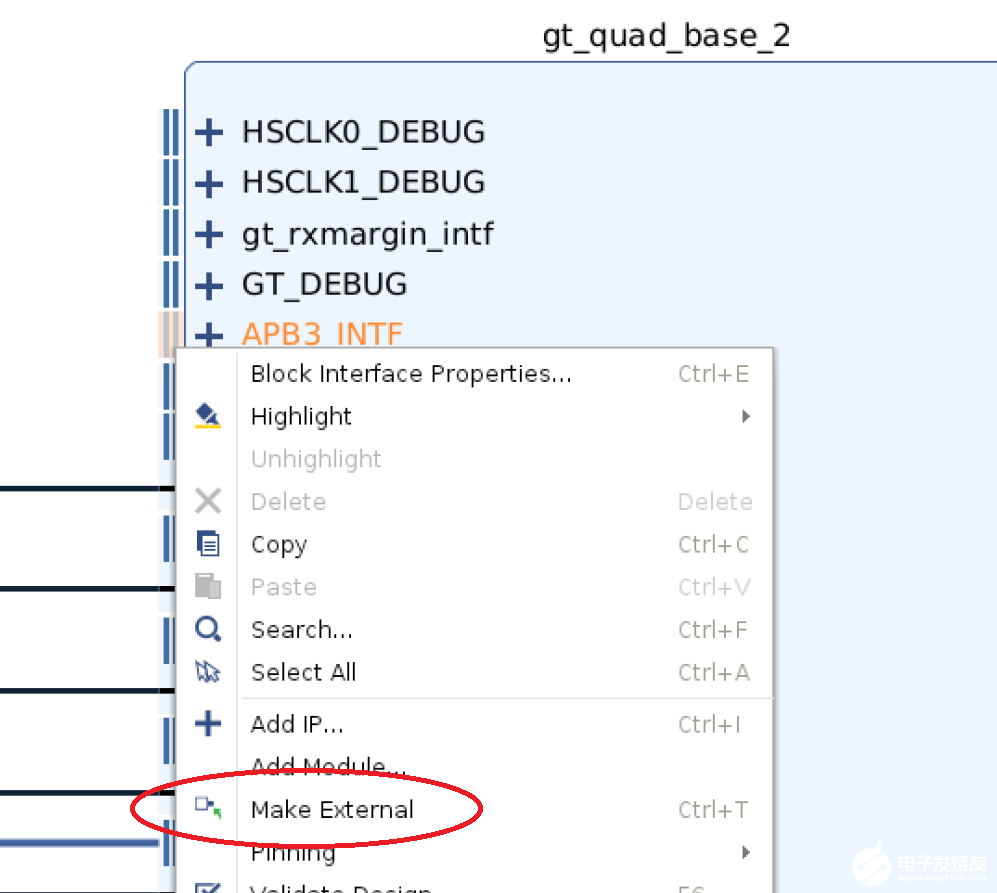

比方说,在一个DCMAC IP的例子工程当中,不同于上面的MRMAC example,这个DCMAC example也没有使用到GT的APB3接口信号,这些端口不仅没有连接,还被保留在了Block Design内部,没有被拉出来。首先,可以点开Block Design,找到gt_quad_base模块和它的APB3接口信号,如下图。右键点击这个端口,选择“Make External“。然后Vivado 工具会自动把这些点选到的信号,拉到顶层模块。

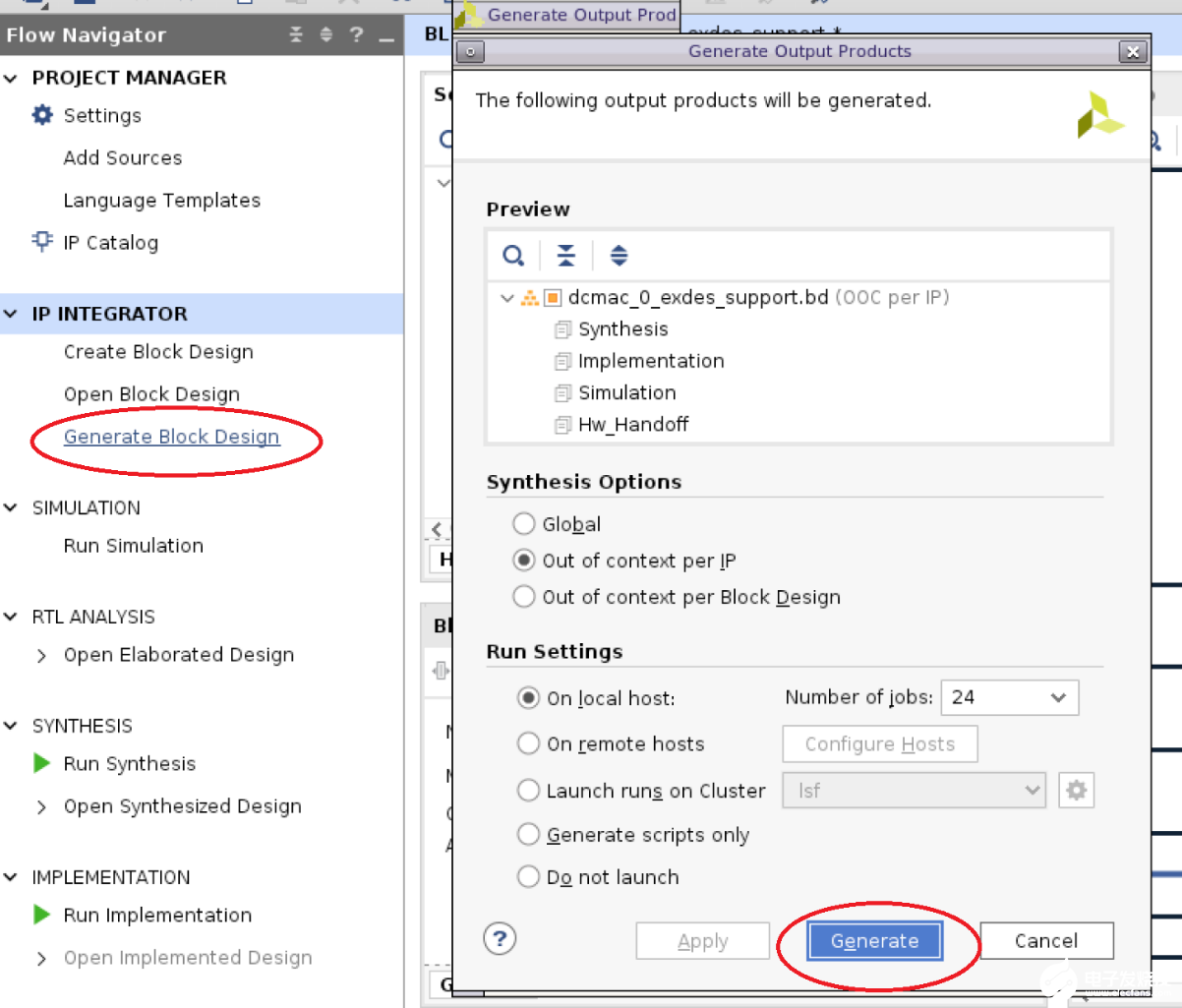

接下来,请点击“Generate Block Design“,完成后,你就能够在example顶层设计里直接用逻辑去控制这些拉出来的GT端口信号了。

3. 通过CIPS读、写以太网IP的寄存器

在DCMAC或者MRMAC IP的例子工程里面,都调用CIPS模块,该模块可以用来读写以太网IP的寄存器。

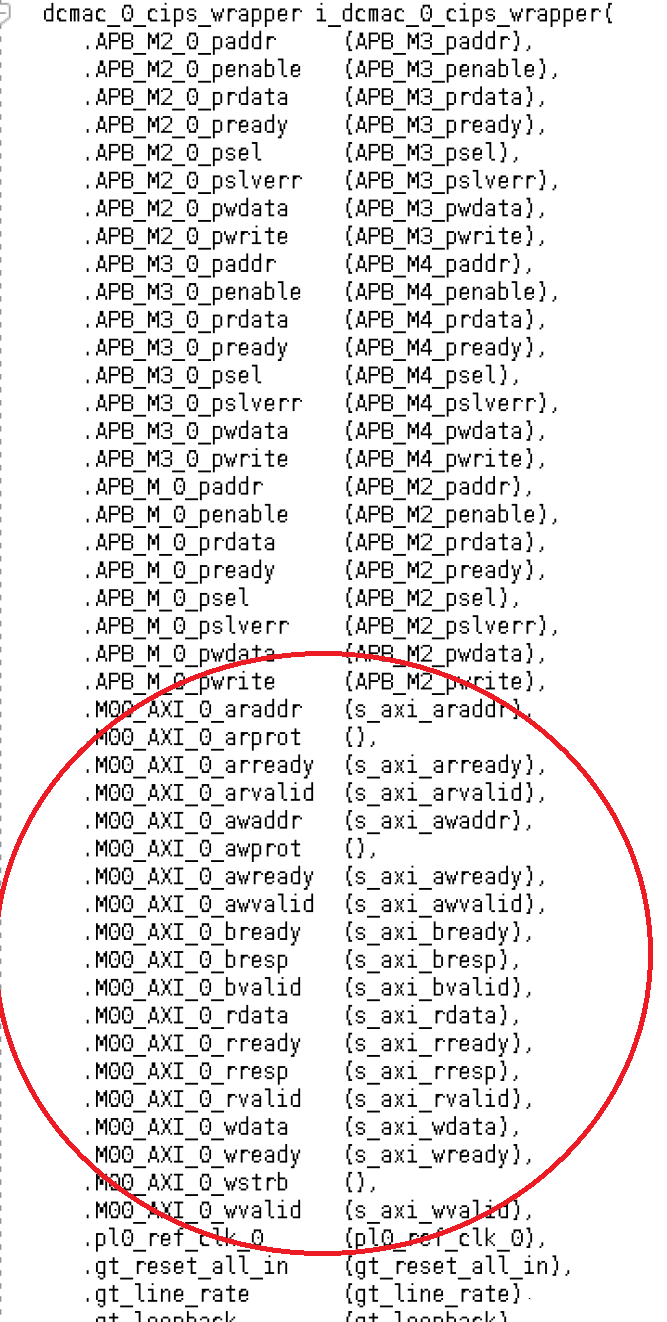

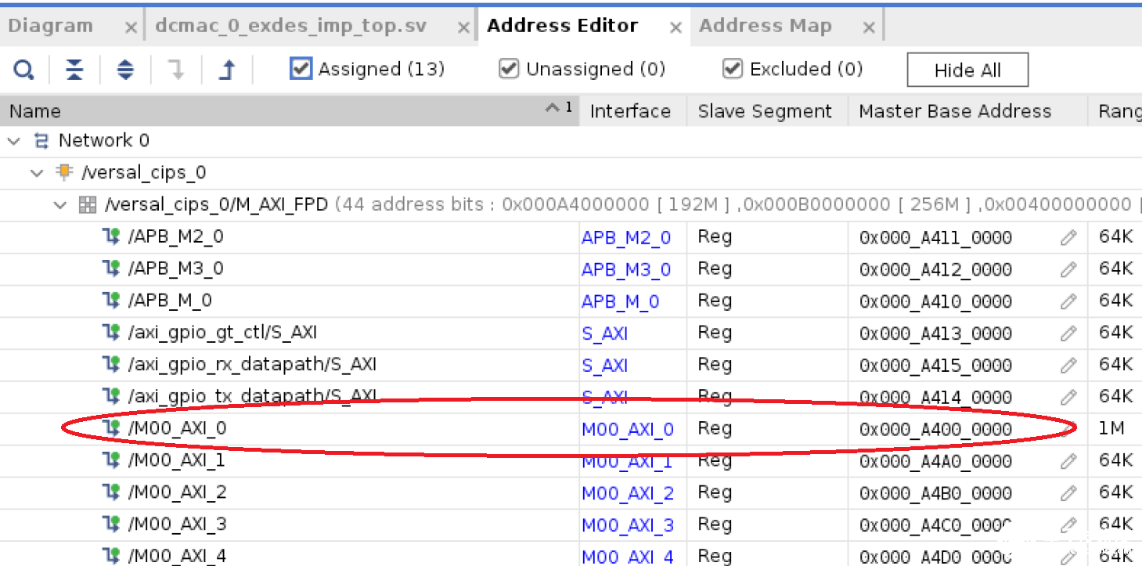

首先,你可以打开example top文件的源代码,找到CIPS模块的信号连接,再点开Vivado工程里面的“Address Editor“,确认每个模块对应的地址分配情况,如下面两张图。

请在AMD的网站上,下载这些以太网IP的寄存器地址映射信息。

(比如MRMAC的pg314-mrmac_registers_v1_5.zip)

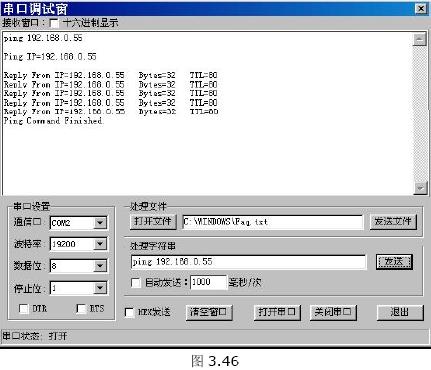

在以太网IP的文档中(如MRMAC的PG314)描述了如何使用XSDB平台,通过CIPS读写IP的寄存器。请在Tera Term工具中打开XSDB Console,使用mrd/mwr指令,实现读写寄存器。

这里是一组用以完成MRMAC初始化的寄存器读写指令的例子。

mwr-force27520532520x00000FFF mwr-force27520532560x40000A24 mwr-force27520532640x00000033 mwr-force27520532600x00000C03 mwr-force27520534560x00000000 mwr-force27520575520x00000000 mwr-force27520616480x00000000 mwr-force27520657440x00000000 mwr-force27520532520x00000000 mwr-force27520532920x00000001 mwr-force27525120000x00000F02 mwr-force27525120000x00000002 mrd-force2752577544 mwr-force27520551080xFFFFFFFF mwr-force27520592040xFFFFFFFF mwr-force27520633000xFFFFFFFF mwr-force27520673960xFFFFFFFF mrd-force2752055108 mrd-force2752059204 mrd-force2752063300 mrd-force2752067396

4. 如何修改IP的内部源代码

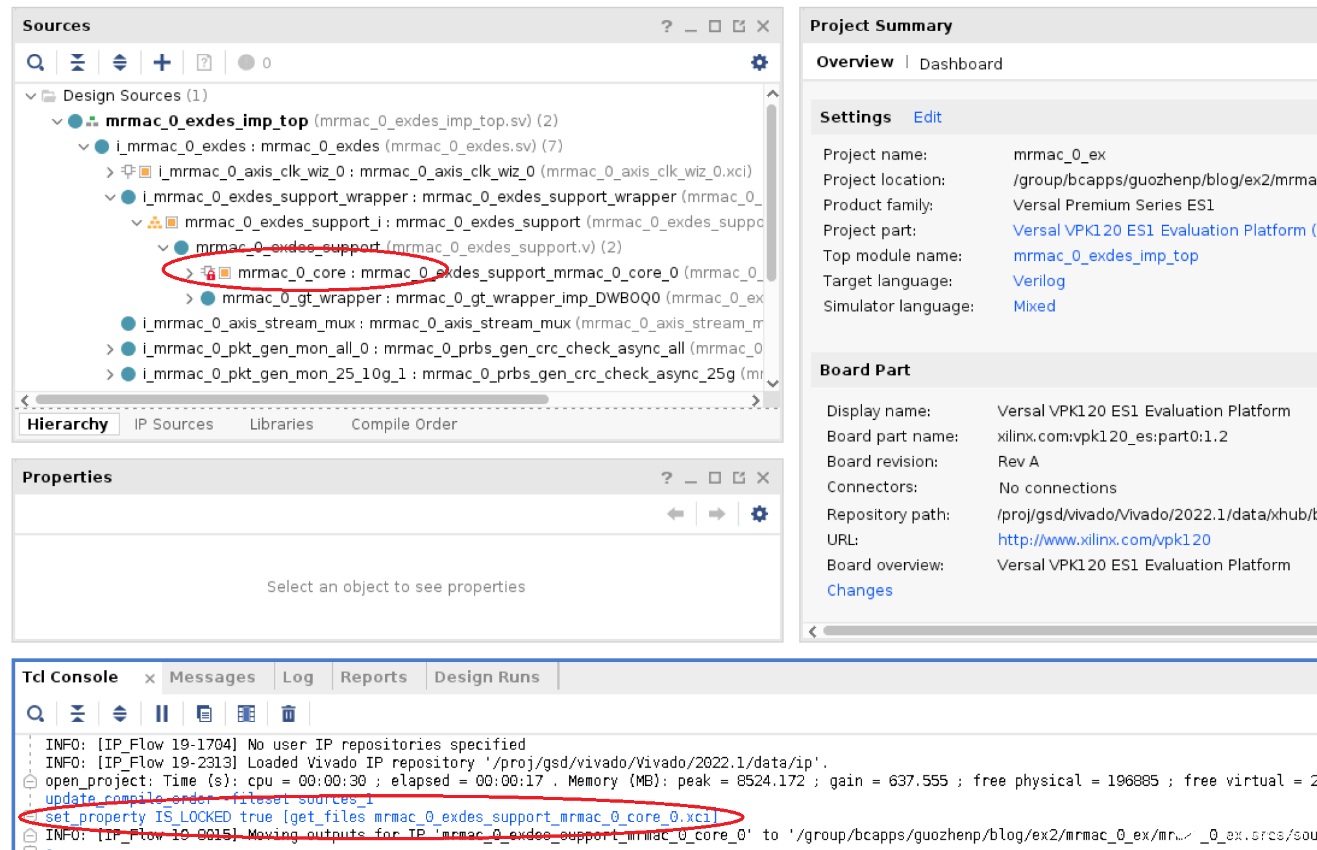

有的时候,用户还会想要直接修改IP内部那些没有被加密的HDL源代码。点开Vivado工程里的.xci IP,可以看到内部有很多代码模块。有些模块仍然是有HDL源代码的,但是因为这些代码文件在IP的.xci下面,因此不能直接修改,如果直接改完,工具在跑流程的过程中,很可能重新自动产生这个文件把你的手动修改给覆盖掉。

你可以参考这个AR里面介绍的,Vivado的手动修改IP代码的流程操作“57546 - Vivado IP Flows - How to modify/edit IP core source files in Vivado?“;在本文的IPI流程当中,我们可以采用类似的方式,来实现手动修改IP内部代码。

首先用下面这个命令,将需要修改的IP Lock住。

set_propertyIS_LOCKEDtrue[get_filesXXX.xci]

然后在Vivado以外找一个第三方的文本编辑器工具,打开要改的这个HDL源代码文件,修改后保存,重新综合IP,这样Vivado就不会重新生成这个文件覆盖你的修改了。你的手动修改将能够起效。

审核编辑:汤梓红

-

模块

+关注

关注

7文章

2696浏览量

47430 -

以太网

+关注

关注

40文章

5419浏览量

171585 -

寄存器

+关注

关注

31文章

5336浏览量

120224 -

Versal

+关注

关注

1文章

158浏览量

7656

发布评论请先 登录

相关推荐

基于TCP IP协议栈的嵌入式以太网终端设计

自动化行业中的全厂自动化中的以太网/IP

以太网和工业以太网的不同

【FPGA DEMO】Lab 10:千兆以太网

Android系统启动以太网卡及支持双网卡共存的操作流程

基于以太网接口的TCP/IP 实验

Ethernet/IP工业以太网的研究

如何在IPI流程中修改(以太网)IP工程(及其所包含的GT模块)的代码与属性

如何在IPI流程中修改(以太网)IP工程(及其所包含的GT模块)的代码与属性

评论