一. 设计目标

1.编辑镜像加法器电路原理图。

2.对镜像加法器进行仿真并观察波形。

3.绘制镜像加法器版图,并进行 DRC 验证。

4.对版图电路进行仿真并观察波形。

5.对电路网表进行 LVS 检验观察原理图与版图的匹配程度。

二、镜像加法器的电路结构

镜像加法器是一个经过改进的加法器电路,首先,它取消了进位反相门;其次,门的 PUN 和 PDN 网络不再是对偶的, 而是巧妙地实现了进位传播 /产生/取消功能 ——当 D(D= ~(A+B) )或者 G(G=AB)为高时, ̄C0 分别被置为 VDD 或 GND。当满足进位传播条件时(即 P=A⊕B 为 1),输入位以反相的形式传播到 ̄C0,这一结构的全加器单元仅需要 24 个晶体管,使面积和延时都有相当程度的减少。

其真值表如下表:(看C非和S非都为0时对应的A、B、Ci,因为在镜像设计中不采用反相器)

其真值表如下表:(看C非和S非都为0时对应的A、B、Ci,因为在镜像设计中不采用反相器)

由全加器的真值表可以得到,当A、B、Ci中只有一个输入是1或者三个输入都是1时,全加和输出为1。且在A、B、C只有一个是1时,进位输出是0.

由全加器的真值表可以得到,当A、B、Ci中任意2个输入为1或三个输入全为1时,进位输出是1.

-

反相器

+关注

关注

6文章

311浏览量

43487 -

晶体管

+关注

关注

77文章

9744浏览量

138816 -

加法器

+关注

关注

6文章

183浏览量

30217 -

DRC

+关注

关注

2文章

150浏览量

36330 -

LVS

+关注

关注

1文章

36浏览量

9967

发布评论请先 登录

相关推荐

十进制加法器,十进制加法器工作原理是什么?

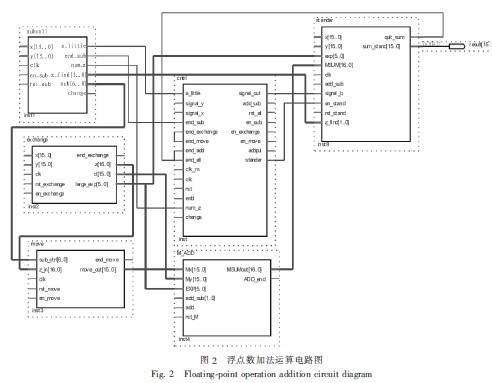

FPU加法器的设计与实现

同相加法器电路原理与同相加法器计算

加法器工作原理_加法器逻辑电路图

镜像加法器的电路结构及仿真设计

镜像加法器的电路结构及仿真设计

评论