器件中的高功耗虽然是可以容忍的,但是在设计过程中,我们往往都在追求低功耗实现。上篇文章中,小编对MCU的低功耗设计有所解读。为增进大家对功耗的了解程度,本文将对寄存器传输级低功耗设计方法予以介绍。

除了芯片的速度和面积等,人们对低功耗的期望也越来越高,因而在IC设计中加入低功耗设计非常必要。寄存器传输级的低功耗设计对降低整个芯片的功耗作用非常显著,本文讨论的三种寄存器传输级低功耗设计方法,经验证对动态功耗的降低很有效。

自集成电路问世以来,设计者在单个芯片上集成的晶体管的数量呈现出令人惊讶的增长速度。近30年,集成电路的发展一直遵循着“摩尔定律”:集成在芯片上的晶体管的数量每18个月就翻一番,芯片成本也相应下降。

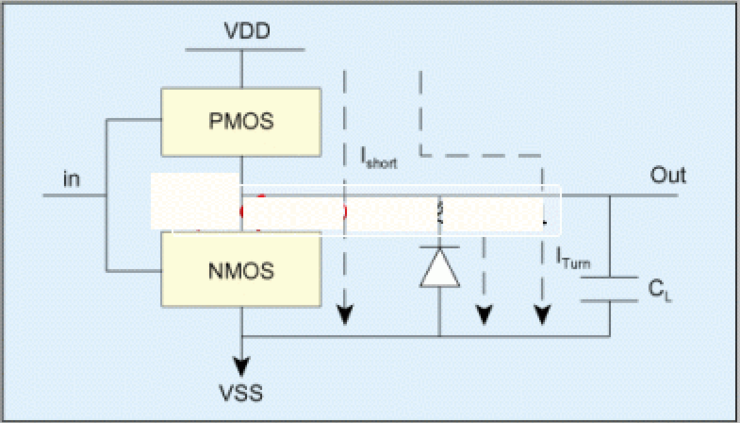

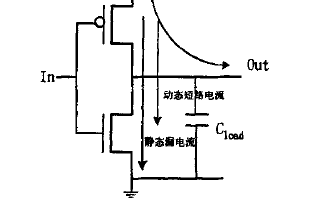

图1:CMOS电路功耗的主要来源是动态功耗,由开关电流和短路电流造成。

在半导体工艺水平不断进步的同时,以电池供电的手持设备和膝上电脑也迅速普及,系统的功耗有时已经成为系统设计首要考虑的因素,因此,低功耗设计成为发展移动系统必然要解决的问题。

集成电路的低功耗设计分为系统级、寄存器传输级、门级、电路级四个层次,而在这其中,寄存器传输级的低功耗设计对优化整个系统功耗的贡献达到20%-50%,这是非常巨大的比例。因而,在寄存器传输级进行低功耗设计是非常值得,也是很有必要的。

集成电路中功耗的来源

目前,CMOS工艺在集成电路特别是数字IC中应用得很普遍。由于CMOS电路在输入稳定的时候总有一个管子截止,所以它的静态功耗在理想情况下应该是零,但这并不代表静态功耗真的为零,实际上CMOS电路的静态功耗就是指电路中的漏电流(这里不考虑亚阈值电流)。

CMOS电路功耗的主要来源是动态功耗,它由两部分组成:开关电流和短路电流。

所以,整个CMOS电路的功耗为:其中,PTurn是开关电流ITurn产生的动态功耗;Pshort是动态情况下P管和N管同时导通时的短路电流Ishort产生的动态功耗;而Pleakage 是由扩散区和衬底之间的反向偏置漏电流Ileakage产生的静态功耗。如图1所示。

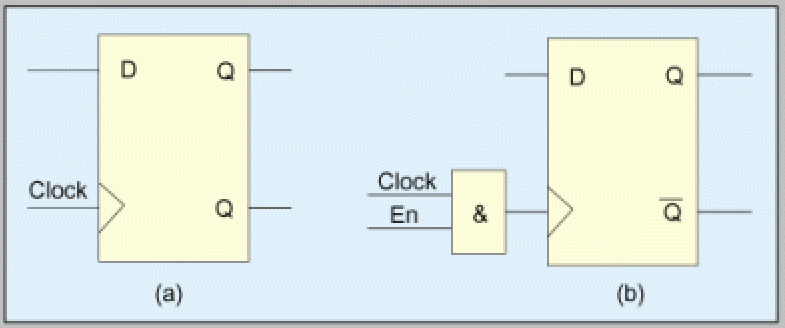

图2a:传统的设计。图2b:增加了门控时钟的设计。

在这三项中PTurn大约占电路功耗的80% ,因而这里就只考虑开关电流ITurn所产生的动态功耗PTurn。ITurn是这样产生的:在CMOS电路,当输入为“0”时,PMOS导通,电源通过PMOS向负载电容充电;而当电路输入为“1” 时,负载电容又会通过NMOS向地放电。ITurn就是不断对负载电容充放电所产生的开关电流。

一个CMOS反相器由开关电流引起的平均动态功耗是:PTurn=CLVDD2f其中,CL是负载电容,VDD是电路的电压,f是时钟频率。所以,要想降低电路的功耗就应该降低电路的电压和频率。

寄存器传输级的低功耗设计

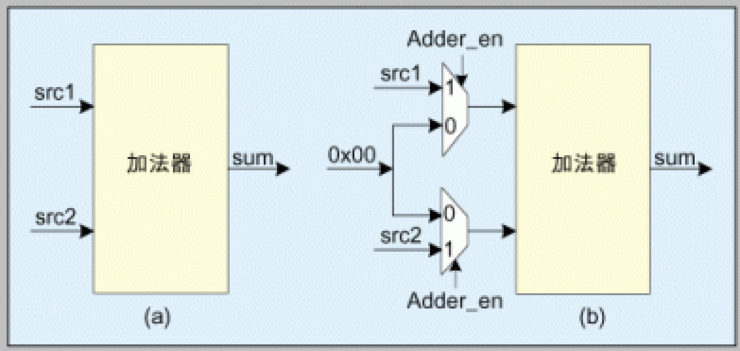

图3a:最基本的加法器设计。图3b:采用操作数隔离方法设计的加法器。

寄存器传输级的低功耗设计方法有很多种,本文只列举三种最为常用的设计方法:门时钟、操作数隔离及存储器分区访问。

1.门控时钟

从上面的讨论知道,CMOS电路的功耗是和频率有着密切关系的,因此动态的关闭处于空闲状态的时钟具有明显的节电效果。

图2a是传统的设计:系统的时钟直接接到D触发器的时钟输入端,不管什么情况,只要输入的Clock翻转,触发器就会工作,整个系统也一直不断的运行。而图2b是增加了门控时钟的设计:当系统正常工作时,译码出来的En信号为高,则触发器可以正常锁存数据;当系统处于空闲状态时,把En信号清零,这样,由于给触发器的Clock一直保持零,不会发生翻转,所以触发器不会锁存新的数据,整个系统被挂起,系统将进入低功耗模式。

在电路中加入门控时钟很容易,可以用Verilog直接在描述中加入,也可以通过Synopsys的工具PowerCompile自动加入。通过加入门控时钟,系统可以有选择的停止不相关模块的时钟,以最大程度的节省动态功耗。

2.操作数隔离

这种方法主要是对系统中的算术、逻辑运算模块进行低功耗设计,其主要思想就是:在不进行算术、逻辑运算的时候,使这些模块的输入保持“0”,不让操作数进来,输出结果不会翻转;而如果进行这方面的运算时,再将它们打开。

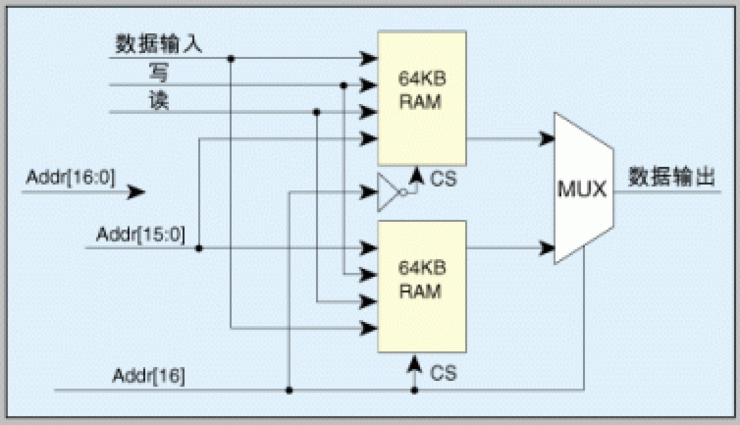

图4:存储器分块访问实例。

这种方法在很多人看来是理所当然的,认为就应该是这样设计。然而在实际中,设计者一方面关心模块的功能,另一方面迫于设计时间的压力,所以很多设计中的细节没有考虑。如图3a,一个加法器的两个输入端没有经过任何逻辑直接进入加法器,系统不管是否需要加法运算,加法器都一直工作着,输出不断翻转着,这对系统的动态功耗是很大的浪费,而且数据总线越宽浪费的功耗越多;图3b 则用操作数隔离的方法进行设计:当系统不需要加法运算的时候,Adder_en信号为“0”,则加法器的两个输入端都保持“0”, 其输出不会发生任何翻转,不会产生动态功耗,而如果需要进行加法运算时,Adder_en变成“1”,加法器正常工作。

当对系统里所有的算术、逻辑运算单元都用上这种方法必然会对系统的动态功耗有很大的优化,在芯片面积方面,如图3b所示的,所增加的逻辑仅仅是几个多路器而已。

3.存储器分块访问

一个系统里少不了存储器,存储器的功耗在整个系统里所占的比例不可忽视。因而降低存储器的功耗,对于整个芯片系统的功耗优化很有帮助。

这里提出一种叫做存储器分块访问的方法来降低存储器的功耗。主要思想是:将系统所需要一定容量的存储器分成两块,然后用高位地址线进行片选译码。结合下面的实例:

假设一个系统需要128K的RAM,如图4所示,我们选用两块64KB的RAM。CPU给出了17位地址线,其中低16位地址线直接提供给两个RAM,最高位地址线接到下面RAM的片选端CS,而这根地址线经过一个反相器接到另一个RAM的片选端。通过这种方法,不管从CPU 出来的什么样的地址,则每次只会选中一个64KB的RAM。如果采用单块128KB的RAM,则每次都要选中一块128KB的RAM。众所周知,一块64KB RAM的功耗要远小于一块128KB RAM的功耗。这样从存储器这一方面,又为系统节省了功耗。

功耗和面积永远是相矛盾的,如果想要降低系统的功耗,必然要加上一些控制逻辑来进行功耗优化,而这部分逻辑会增加芯片的面积,所以在功耗和面积之间就要有个折衷。上面的三种寄存器传输级的低功耗设计,不会增加很多逻辑,因而对芯片面积的影响不大。而经过了这三种低功耗设计,使整个系统动态功耗的改善很明显。例如,使用功耗仿真工具powermill对一款SIM卡芯片设计进行管级功耗仿真,这里采用的是华杰的0.25um的标准单元库,表1是优化前后功耗及芯片面积的对比。

可以看到,经过低功耗设计后的芯片平均动态电流比优化前降了16%,然而优化前后芯片的面积没有发生改变,因而,上面的三种设计方法对于降低系统动态功耗是非常有效的。

审核编辑:汤梓红

-

寄存器

+关注

关注

31文章

5336浏览量

120230 -

存储器

+关注

关注

38文章

7484浏览量

163763 -

晶体管

+关注

关注

77文章

9682浏览量

138080 -

低功耗

+关注

关注

10文章

2396浏览量

103672

发布评论请先 登录

相关推荐

STM32低功耗

430低功耗问题

Stm32的低功耗模式介绍

MAX11120-MAX11128低功耗,逐次逼近寄存器串行ADC

在学习低功耗设计看看如何解决寄存器传输功耗问题

DSP不同层次的低功耗设计研究思路综述

芯片RTL设计中如何做到低功耗设计

MCU学习笔记_STM32低功耗模式概述

STM32超低功耗进阶之电源管理库函数(一)

在学习低功耗设计?看看如何解决寄存器传输功耗问题

在学习低功耗设计?看看如何解决寄存器传输功耗问题

评论