由于微控制器激增到越来越多的权力受限的设计,加工效率成为越来越多的关注,以系统设计。该驱动器来获得额外的处理能力以更低的功率是由电池不仅是重要的操作的产品,但是,越来越多的功率也制约了许多“插件”模块,其中功率由模块规格的限制。在这些情况下,一个有效的设计将能够提供更多的功能,并创建一个竞争优势一个效率较低的实施。 MCU设计的一个被忽视的方面是在时钟控制区。设计人员往往可以通过使用时钟控制模块的高级特性来调整时钟为CPU,外设和其他耗电的资源打造更高效的设计。本文将探讨先进的时钟控制模块一些常用功能的能力,并展示它们的使用如何能改善大多数MCU为基础的设计处理效率。

时钟源

MCU的总体操作由一个时钟控制块和许多时钟控制块管理具有的功能,可用于选择,控制和管理的时钟源的CPU,内存,外围设备,和模拟模块。通过控制时钟这些块,甚至关闭的时钟不被在某些处理程序使用的功能,功率可以被应用到需要它和MCU的只是部分只是在需要时,使得对于一个非常有效的实现。的起点的时钟管理和控制是可使用的不同的时钟源的各种子模块。了解每一个时钟源的优点和缺点是起点的高效的MCU执行。许多共同的时钟源和控制功能中提供了意法半导体ST32F37xx MCU的时钟控制块。例如,高速外部(HSE)时钟,如图1所示的左中,使用任一外部晶体/陶瓷谐振器或现有的用户提供的时钟。外部晶体/陶瓷谐振器可以操作4至32兆赫,并产生一个非常精确的主时钟速率。如果现有的外部时钟已经可用,或如果用户希望实行额外控制的时钟源(可能停止或更细的低功率操作控制减慢时钟),外部时钟输入都可以使用。这也释放了一个附加的GPIO引脚,因为少了一个引脚,需要在谐振器实现。

(意法半导体公司提供)的高速内部从内部的8 MHz的RC振荡器产生(HIS)的时钟信号,并且可以直接用作系统时钟或由两个分割所使用由PLL之前。所述HIS RC振荡器具有以低成本提供一个时钟源,因为它不使用外部元件的优点。它还具有比HSE晶体振荡器更快的启动时间;然而,即使使用校准的频率比外部晶体振荡器或陶瓷振荡器不太准确。注意,CPU时钟只能通过的高速时钟的一个或从PLL的输出来驱动。该STM32F37xx也有两个低速时钟源。的低速外部(LSE)晶体/陶瓷振荡器示出在图1的顶部,并使用高精度32.768kHz的谐振器来创建精确时钟源的实时时钟(RTC)的外围。低速内部RC振荡器提供用于自动唤醒从低功耗停止/睡眠模式时,它驱动独立看门狗定时器和可选的RTC 40kHz的信号。低功耗时钟从高速时钟独立运作,以便他们外设可以当主系统时钟被关闭,从而节省显著电源也能工作。这些时钟源均显示出典型的来源,你会发现在大多数微控制器。时钟源,如在图1中所见只是的起点,在大多数的MCU的时钟架构。一般的时钟可被进一步选择,加工(通常与一个或多个锁相环,或PLL,块),或启用的所有下控制MCU。我们将继续我们的时钟控制的探索通过查看下一节一个PLL模块的典型功能。

锁相环操作

不同的时钟操作的模块,例如在锁相环(PLL)和锁频环(FLL)块,是最重要的,但典型地小于理解在一个时钟控制模块元件。飞思卡尔的Kinetis K10子系列MCU具有多用途时钟发生器(MCG)模块,其中包括一个FLL和PLL,所以它是一个很好的例子来审查。该的Kinetis K10 MCG FLL是可控通过任何一个内部或外部参考时钟。该PLL是可控的外部基准时钟。该模块可以选择的FLL-或PLL输出时钟的内部 - 或外部参考时钟或任一作为MCU系统时钟源。 MCG的操作与一个晶体振荡器,其允许外部晶体,陶瓷谐振器,或其他外部时钟源,以产生所述外部参考时钟一起使用。

(飞思卡尔提供)的FLL块,在图2的中间所示,它选择的时钟源,且运行在它创建所需的时钟频率。输入时钟可以通过十六个不同的值进行划分,从1至1536,以创建之间31.25kHz到39.0625千赫的基频。基频,然后通过数字控制的振荡器(DCO)相乘来创建从20兆赫和96兆赫之间的所需输出频率。从多种频率,通过使用FLL进行选择的能力,可轻松调整时钟速率为只是操作所需的特定模式的正确的频率,提高了处理效率。该PLL操作以类似的方式,但采用的是电压控制振荡器(VCO)来调整时钟输出频率。的输入时钟的PLL能够由一个预定标器被除以2至25.一种相位检测器的因子结合了PLL的输入时钟与VCO输出时钟由一个因子乘以输入信号从24至55 。所有这除法和乘法的结果是一个时钟信号,它是所需要的应用的精确值。通常有由PLL在FLL需要额外的电源,但PLL有更精细的调整,提高精度。注意,无论是在PLL或FLL可被禁用,以降低功耗,如果他们不要求产生所需的应用,例如频率,在外部时钟信号提供所需的精确频率的情况。

外设时钟控制

后的源时钟进行了调整(如果需要)通过使用有PLL它是由时钟分配网络提供单独的时钟为每个键的MCU块。该CPU及其相关存储系统将需要自己的时钟,但通常各种外设都会有自己的时钟,以及。更细碎的外设时钟网络是,越容易分别选择和控制的时钟,以及调节操作频率,以该应用程序所需。时钟网络被控制的通常的方法是添加时钟分频器电路(因为它是通常用于将外围的运行速度比在CPU慢)和偶数时钟禁止电路中,如果外围不需要在所有。更控制可用的更多的功率和性能可以进行调整,但在某些方面的附加模腔(及其相关的成本),并需要额外的功率必须考虑。通常,制造商限制从提供完全灵活性的时钟网络,而是试图提供足够的能力,对于大多数应用程序来获得显著能力和处理效率。 NXP,其LPC15xx MCU,已分割的时钟分频器每个键外围功能,如图3中,沿着非常实用线,因此很容易确定的设置要使用的每个子块。例如,该时钟信号到USART块,在图3的中部右侧所示,从主时钟源,但是使用USART外设时钟分频器可以预先分割(通过从1到255或完全禁用) 。这个时钟信号可以被用于个人分数波特率发生器(含16位时钟除数可用),每个USART模块中,可以很容易单独设置波特率每个USART的。其它外设时钟分频器上提供一个共同的功能的基础上可以很容易地配置和控制的性能,并且因此所有的关键周边块的功耗。

(恩智浦提供)分组外设时钟按照职能是一个简单的概念,而是一个变得更加复杂,当外围设备能协同工作。例如,注意,ADC时钟分频可以从SC定时器PLL进行采购。这似乎是不必要的连接,直到你认识到ADC可结合工作与SC定时器以周期性的转换,而无需CPU干预。护理在创造所需的所需操作的灵活性,而不会加重与外部复杂的时钟控制模块的其他级别,是一个经过深思熟虑的实施标志。

动态时钟控制

一旦你选择的时钟在大多数电源和加工效率的方式不同外设,你可能会认为你完成。为了获得更大的性能和功耗控制,你可能也想动态调整的视功能或模式MCU在某些加工或周边块的速度。灵活的时钟选择网络是利用动态时钟所需的关键功能。于Silicon Labs MCU壁虎时钟控制模块,如图4所示的部分,说明了这一点。在图的左上侧的高频时钟交换机可以从任一高频时钟(HFXO或HFRCO)或低频时钟(LFXO或LFRCO)选择。这样就可以很容易地“混搭”低频源或高频源取决于模式的设备在操作类型

(Silicon Labs公司提供)动态时钟选择可进入和走出了一条传统的低功耗模式时,需要太多的最有用的“启动”时间(即使是高能效的Gecko MCU系列可能需要2微秒唤醒弥补了EM2低功耗状态和高达160微秒的极低功耗EM4状态)。通过动态地选择一个低频率的时钟,该功率节省是少的,但在快速响应时间(通常在仅仅时钟周期的量级)的速度要快得多。这可以使捕获异步事件或缺失其之间的差异。有时钟控制水平也可以增加使用低功耗状态时,在工作状态需要一个中档的处理性能。寻找动态时钟控制的机会,在您的设计实现最功耗和处理效率水平。

摘要

高级时钟控制模块提供了一些令人惊讶的功能,可以帮助管理一个MCU中的电源使用。控制时钟的外围设备,管理CPU的时钟速率,并在处理期间动态地改变时钟速率都只是一些可以被用来创建更高效的设计的技术。

审核编辑 黄宇

-

微控制器

+关注

关注

48文章

7712浏览量

152612 -

mcu

+关注

关注

146文章

17455浏览量

354314 -

时钟控制

+关注

关注

0文章

17浏览量

6892

发布评论请先 登录

相关推荐

智能摊铺压实监测管理系统有效提高了沥青道路施工质量和耐久性

SMT技术:电子产品微型化的推动者

如何通过直流负载箱优化电源测试效率?

Dali通信如何提高能源效率

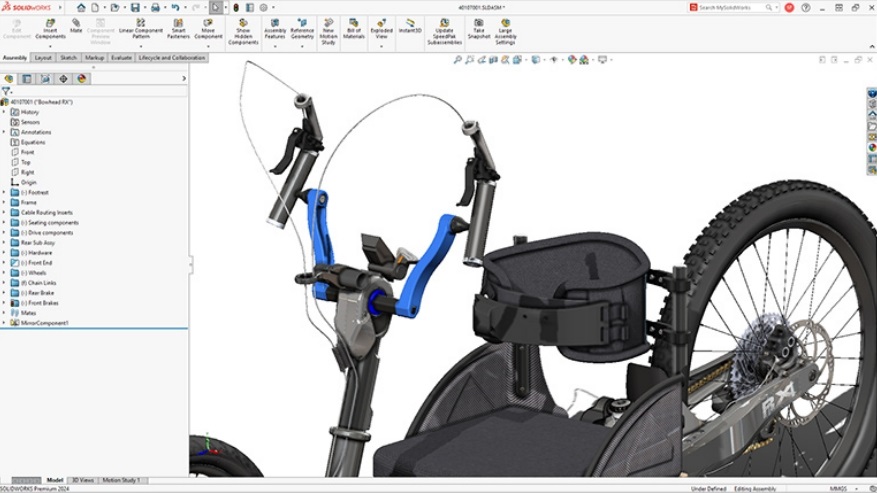

SOLIDWORKS 2025提高数据效率

智能摊铺压实监测管理系统不仅提升了施工质量,还显著提高了工程管理的效率

AG32 MCU 的电机控制方案

并联电容器提高了电路的功率因数,能否改变感性

利用TI GaN中的集成电流检测功能更大限度提高系统效率

利用先进的时钟控制功能在MCU设计提高了处理效率

利用先进的时钟控制功能在MCU设计提高了处理效率

评论