今天我们介绍的时序分析基本概念是 Virtual Clock ,中文名称是虚拟时钟。我们通常说的create_clock, create_generated_clock 都是real clock。而virtual clock则不挂在任何port或者pin上,只是虚拟创建出来的时钟。如下所示:

#定义虚拟时钟

create_clock -name VCLK -period 10 -waveform {0 5}

为什么我们要定义virtual clock?

我们通常会把input/output delay挂在virtual clock上,因为input/output delay约束本来就是指片外的时钟,所以挂在virtual clock上较为合理。

如上图所示:片外的时钟CLK2和片内的时钟CLK1频率不同。这样的情况下,如何来定义input port {in1}上的约束?

这时,我们就可以给input port {in1}创建一个virtual clock。

create_clock -name VCLK2 -period 10 -waveform {2 8}

create_clock -name CLK1 -period 8 -waveform {0 4} [get_ports clk]

set_input_delay -clock VCLK2 -max 2.7 [get_ports in1]

-

时序分析

+关注

关注

2文章

127浏览量

22612 -

虚拟时钟

+关注

关注

0文章

5浏览量

6608 -

虚拟机

+关注

关注

1文章

931浏览量

28408 -

CLK

+关注

关注

0文章

127浏览量

17234 -

时序分析器

+关注

关注

0文章

24浏览量

5292

发布评论请先 登录

相关推荐

时序分析基本概念介绍<Operating Condition>

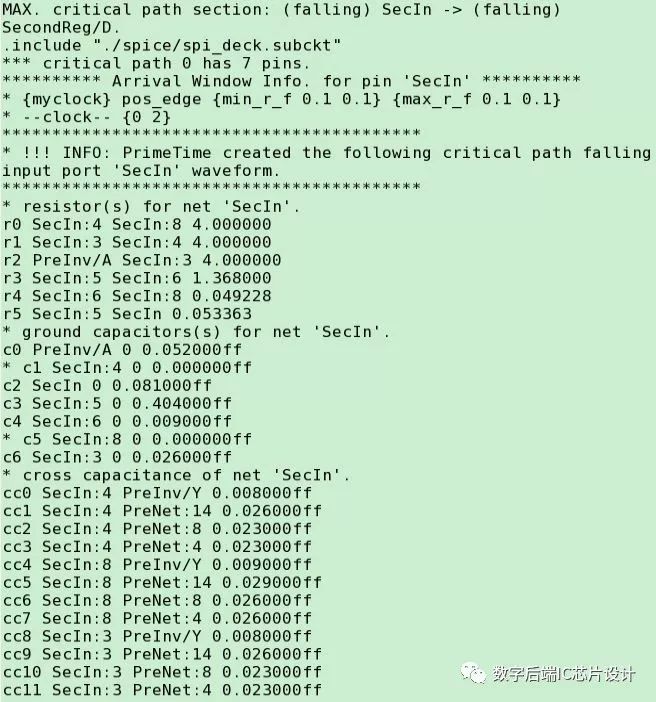

时序分析基本概念介绍&lt;spice deck&gt;

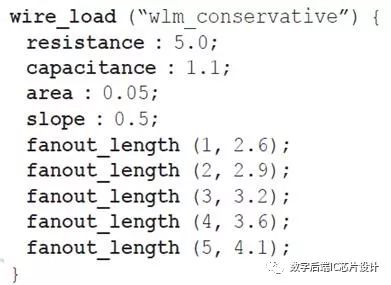

时序分析基本概念介绍&lt;wire load model&gt;

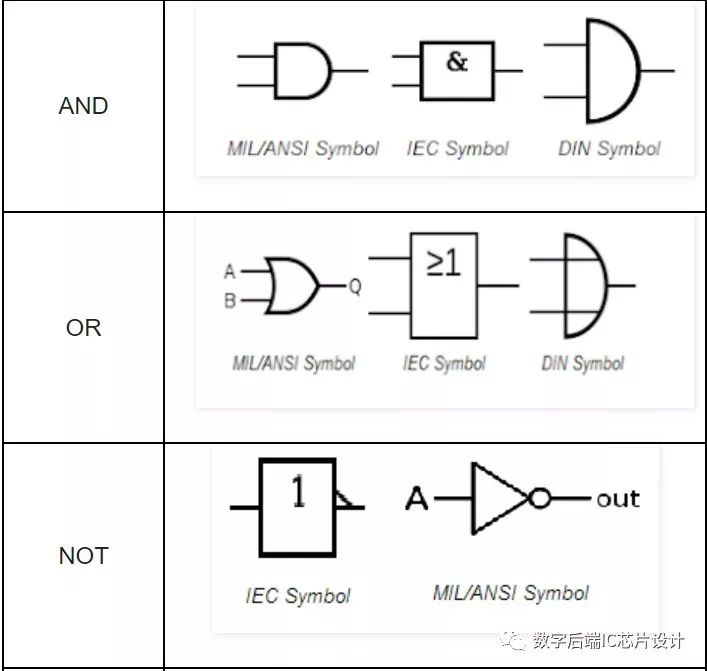

时序分析基本概念介绍&lt;Combinational logic&gt;

时序分析基本概念介绍<Virtual Clock>

时序分析基本概念介绍<Virtual Clock>

评论