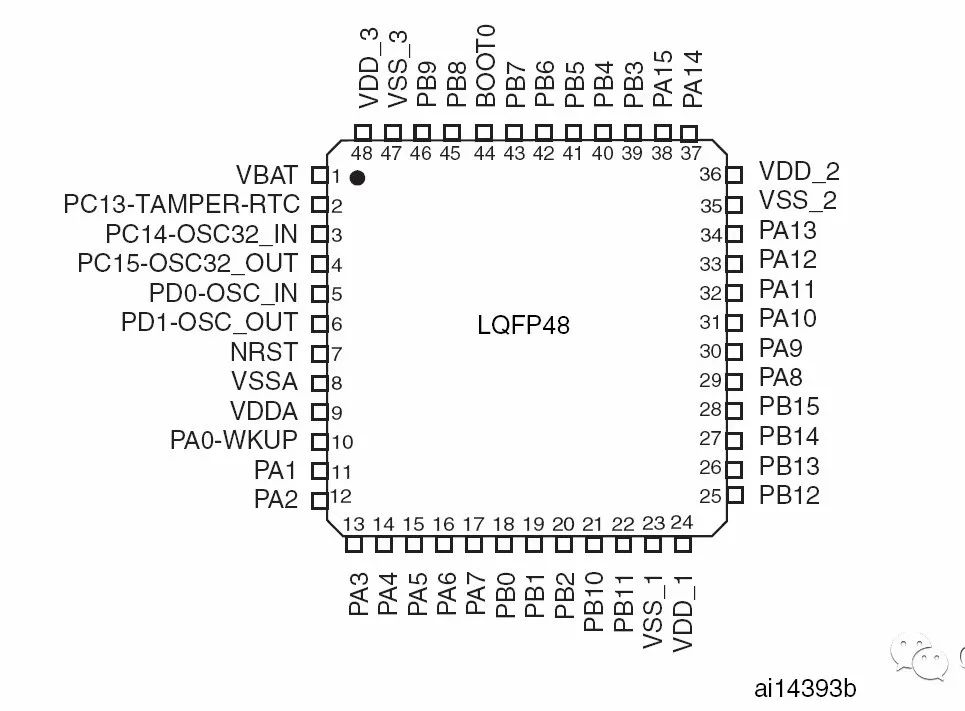

2.1 STM32F103xx增强型LQFP48引脚分布

2.2 STM32F103xx概述

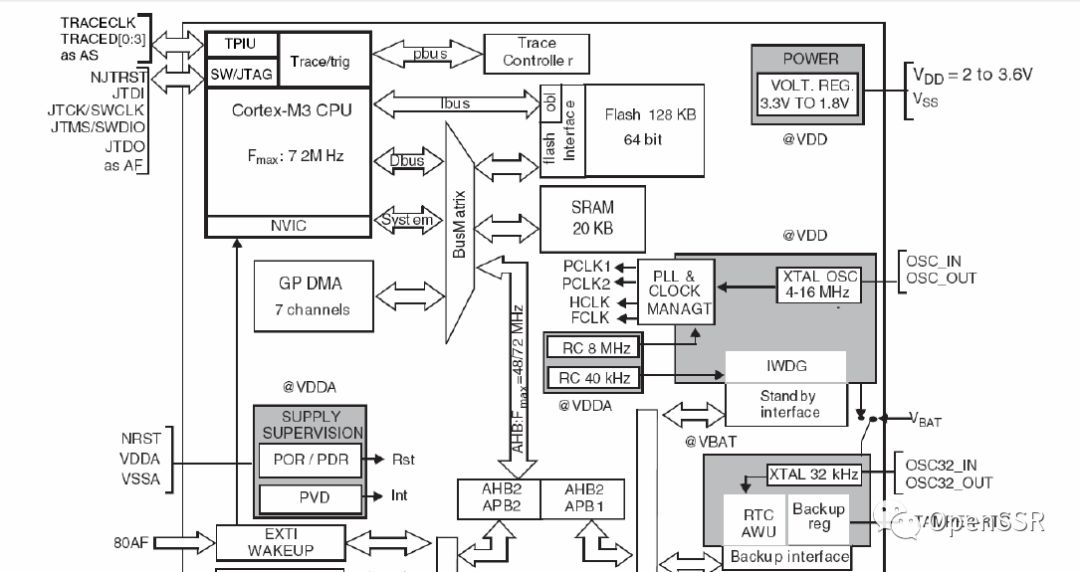

2.2.1 ARM®的Cortex™-M3核心并内嵌闪存和SRAM

ARM的Cortex™-M3处理器是最新一代的嵌入式ARM处理器,它为实现MCU的需要提供了低成本的平台、缩减的引脚数目、降低的系统功耗,同时提供卓越的计算性能和先进的中断系统响应。

ARM的Cortex™-M3是32位的RISC处理器,提供额外的代码效率,在通常8和16位系统的存储空间上发挥了ARM内核的高性能。

2.2.2 内置闪存存储器

64K或128K字节的内置闪存存储器,用于存放程序和数据。小R使用的开发板内置闪存存储器为64K。

2.2.3 CRC(循环冗余校验)计算单元

CRC(循环冗余校验)计算单元使用一个固定的多项式发生器,从一个32位的数据字产生一个CRC码。在众多的应用中,基于CRC的技术被用于验证数据传输或存储的一致性。

2.2.4 内置SRAM

20K字节的内置SRAM,CPU能以0等待周期访问(读/写)。

2.2.5 嵌套的向量式中断控制器(NVIC)

STM32F103xx增强型产品内置嵌套的向量式中断控制器,能够处理多达43个可屏蔽中断通道(不包括16个Cortex™-M3的中断线)和16个优先级。

● 紧耦合的NVIC能够达到低延迟的中断响应处理

● 中断向量入口地址直接进入内核

● 紧耦合的NVIC接口

● 允许中断的早期处理

● 处理晚到的较高优先级中断

● 支持中断尾部链接功能

● 自动保存处理器状态

● 中断返回时自动恢复,无需额外指令开销

该模块以最小的中断延迟提供灵活的中断管理功能。

2.2.6 外部中断/事件控制器(EXTI)

外部中断/事件控制器包含19个边沿检测器,用于产生中断/事件请求。每个中断线都可以独立地配置它的触发事件(上升沿或下降沿或双边沿),并能够单独地被屏蔽;有一个挂起寄存器维持所有中断请求的状态。

EXTI可以检测到脉冲宽度小于内部APB2的时钟周期。多达80个通用I/O口连接到16个外部中断线。

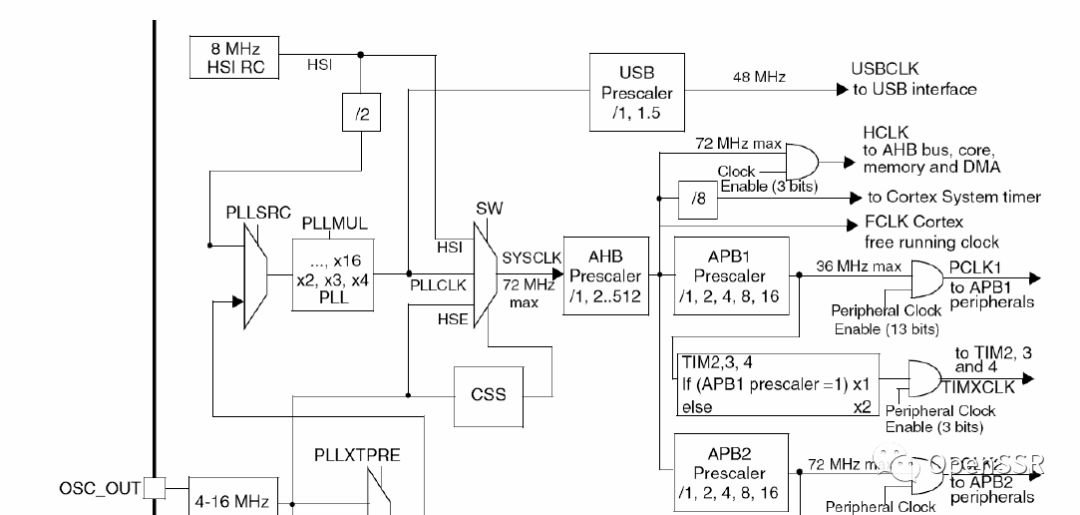

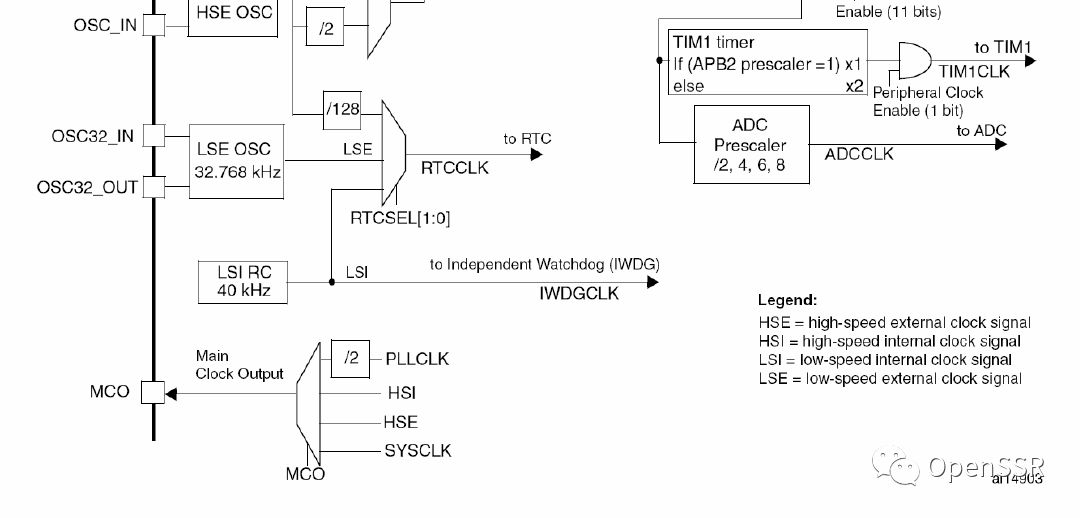

2.2.7 时钟和启动

系统时钟的选择是在启动时进行,复位时内部8MHz的RC振荡器被选为默认的CPU时钟,随后可以选择外部的、具失效监控的4~16MHz时钟;当检测到外部时钟失效时,它将被隔离,系统将自动地切换到内部的RC振荡器,如果使能了中断,软件可以接收到相应的中断。同样,在需要时可以采取对PLL时钟完全的中断管理(如当一个间接使用的外部振荡器失效时)。

多个预分频器用于配置AHB的频率、高速APB(APB2)和低APB(APB1)区域。AHB和高速APB的最高频率是72MHz,低速APB的最高频率为36MHz。

2.2.8 自举模式

在启动时,通过自举引脚可以选择三种自举模式中的一种:

● 从程序闪存存储器自举

● 从系统存储器自举

● 从内部SRAM自举

自举加载程序(Bootloader)存放于系统存储器中,可以通过USART1对闪存重新编程。

2.2.9 供电方案

● VDD = 2.0~3.6V:VDD引脚为I/O引脚和内部调压器供电。

● VSSA,VDDA = 2.0~3.6V:为ADC、复位模块、RC振荡器和PLL的模拟部分提供供电。使用ADC时,VDDA不得小于2.4V。VDDA和VSSA必须分别连接到VDD和VSS。

● VBAT = 1.8~3.6V:当关闭VDD时,(通过内部电源切换器)为RTC、外部32kHz振荡器和后备寄存器供电。

2.2.10 供电监控器

本产品内部集成了上电复位(POR)/掉电复位(PDR)电路,该电路始终处于工作状态,保证系统在供电超过2V时工作;当VDD低于设定的阀值(VPOR/PDR)时,置器件于复位状态,而不必使用外部复位电路。

器件中还有一个可编程电压监测器(PVD),它监视VDD/VDDA供电并与阀值VPVD比较,当VDD低于或高于阀值VPVD时产生中断,中断处理程序可以发出警告信息或将微控制器转入安全模式。PVD功能需要通过程序开启。

2.2.11 电压调压器

调压器有三个操作模式:主模式(MR)、低功耗模式(LPR)和关断模式

● 主模式(MR)用于正常的运行操作

● 低功耗模式(LPR)用于CPU的停机模式

● 关断模式用于CPU的待机模式:调压器的输出为高阻状态。

2.2.12 低功耗模式

STM32F103xC、STM32F103xD和STM32F103xE增强型产品支持三种低功耗模式,可以在要求低功耗、短启动时间和多种唤醒事件之间达到最佳的平衡。

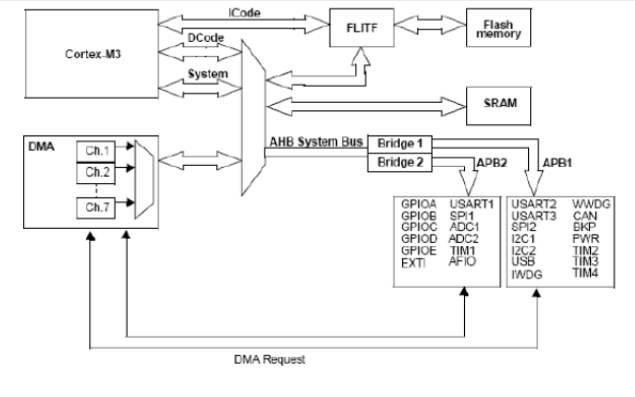

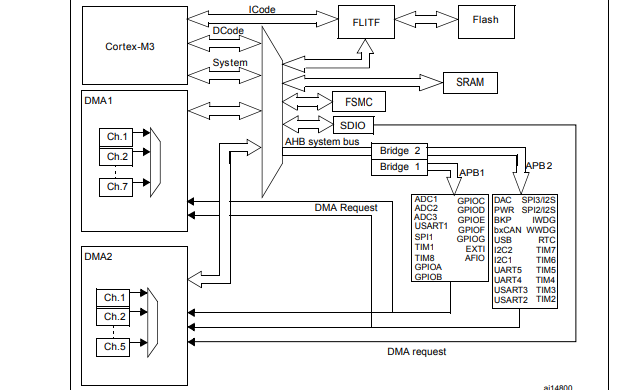

2.2.13 DMA

灵活的7路通用DMA可以管理存储器到存储器、设备到存储器和存储器到设备的数据传输;DMA控制器支持环形缓冲区的管理,避免了控制器传输到达缓冲区结尾时所产生的中断。

每个通道都有专门的硬件DMA请求逻辑,同时可以由软件触发每个通道;传输的长度、传输的源地址和目标地址都可以通过软件单独设置。

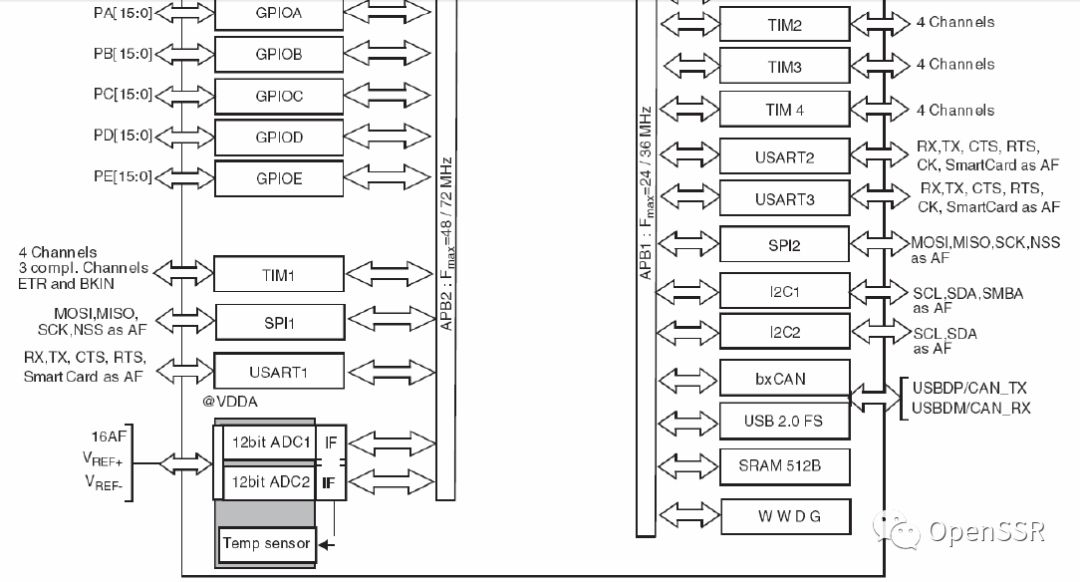

DMA可以用于主要的外设:SPI、I2C、USART,通用、基本和高级控制定时器TIMx和ADC。

2.2.14 RTC(实时时钟)和后备寄存器

中等容量的STM32F103xx增强型系列产品包含1个高级控制定时器、3个普通定时器,以及2个看门狗定时器和1个系统嘀嗒定时器。

高级控制定时器(TIM1)可以被看成是分配到6个通道的三相PWM发生器,它具有带死区插入的互补PWM输出,还可以被当成完整的通用定时器。四个独立的通道可以用于:

● 输入捕获

● 输出比较

● 产生PWM(边缘或中心对齐模式)

● 单脉冲输出

配置为16位标准定时器时,它与TIMx定时器具有相同的功能。配置为16位PWM发生器时,它具有全调制能力(0~100%)。

通用定时器(TIMx)

STM32F103xx增强型产品中,内置了多达3个可同步运行的标准定时器(TIM2、TIM3和TIM4)。每个定时器都有一个16位的自动加载递加/递减计数器、一个16位的预分频器和4个独立的通道,每个通道都可用于输入捕获、输出比较、PWM和单脉冲模式输出,在最大的封装配置中可提供最多12个输入捕获、输出比较或PWM通道。

它们还能通过定时器链接功能与高级控制定时器共同工作,提供同步或事件链接功能。在调试模式下,计数器可以被冻结。任一标准定时器都能用于产生PWM输出。每个定时器都有独立的DMA请求机制。

这些定时器还能够处理增量编码器的信号,也能处理1至3个霍尔传感器的数字输出。

2.2.16 IIC总线

多达2个I2C总线接口,能够工作于多主模式或从模式,支持标准和快速模式。I2C接口支持7位或10位寻址,7位从模式时支持双从地址寻址。内置了硬件CRC发生器/校验器。它们可以使用DMA操作并支持SMBus总线2.0版/PMBus总线。

2.2.17 通用同步/异步收发器(USART)

USART1接口通信速率可达4.5兆位/秒,其他接口的通信速率可达2.25兆位/秒。USART接口具有硬件的CTS和RTS信号管理、支持IrDA SIR ENDEC传输编解码、兼容ISO7816的智能卡并提供LIN主/从功能。

所有USART接口都可以使用DMA操作。

2.2.18 串行外设接口(SPI)

多达2个SPI接口,在从或主模式下,全双工和半双工的通信速率可达18兆位/秒。3位的预分频器可产生8种主模式频率,可配置成每帧8位或16位。硬件的CRC产生/校验支持基本的SD卡和MMC模式。所有的SPI接口都可以使用DMA操作。

2.2.19 控制器区域网络(CAN)

CAN接口兼容规范2.0A和2.0B(主动),位速率高达1兆位/秒。它可以接收和发送11位标识符的标准帧,也可以接收和发送29位标识符的扩展帧。具有3个发送邮箱和2个接收FIFO,3级14个可调节的滤波器。

2.2.20 通用串行总线(USB)

STM32F103xx增强型系列产品,内嵌一个兼容全速USB的设备控制器,遵循全速USB设备(12兆位/秒)标准,端点可由软件配置,具有待机/唤醒功能。USB专用的48MHz时钟由内部主PLL直接产生(时钟源必须是一个HSE晶体振荡器)。

2.2.21 通用输入输出接口(GPIO)

每个GPIO引脚都可以由软件配置成输出(推挽或开漏)、输入(带或不带上拉或下拉)或复用的外设功能端口。多数GPIO引脚都与数字或模拟的复用外设共用。

除了具有模拟输入功能的端口,所有的GPIO引脚都有大电流通过能力。在需要的情况下,I/O引脚的外设功能可以通过一个特定的操作锁定,以避免意外的写入I/O寄存器。

在APB2上的I/O脚可达18MHz的翻转速度。

2.2.22 ADC(模拟/数字转换器)

STM32F103xx增强型产品内嵌2个12位的模拟/数字转换器(ADC),每个ADC共用多达16个外部通道,可以实现单次或扫描转换。在扫描模式下,自动进行在选定的一组模拟输入上的转换。

ADC接口上的其它逻辑功能包括:

● 同步的采样和保持

● 交叉的采样和保持

● 单次采样

ADC可以使用DMA操作。

模拟看门狗功能允许非常精准地监视一路、多路或所有选中的通道,当被监视的信号超出预置的阀值时,将产生中断。由标准定时器(TIMx)和高级控制定时器(TIM1)产生的事件,可以分别内部级联到ADC的开始触发和注入触发,应用程序能使AD转换与时钟同步。

2.2.23 温度传感器

温度传感器产生一个随温度线性变化的电压,转换范围在2V < VDDA < 3.6V之间。温度传感器在内部被连接到ADC12_IN16的输入通道上,用于将传感器的输出转换到数字数值。

2.2.24 串行单线JTAG调试口(SWJ-DP)

内嵌ARM的SWJ-DP接口,这是一个结合了JTAG和串行单线调试的接口,可以实现串行单线调试接口或JTAG接口的连接。JTAG的TMS和TCK信号分别与SWDIO和SWCLK共用引脚,TMS脚上的一个特殊的信号序列用于在JTAG-DP和SW-DP间切换。

2.3 STM32F103xx增强型模块框图

2.4 STM32F103xx时钟树

-

嵌入式系统

+关注

关注

41文章

3839浏览量

134023 -

ARM处理器

+关注

关注

6文章

361浏览量

43411 -

STM32F103

+关注

关注

34文章

499浏览量

68313 -

中断控制器

+关注

关注

0文章

64浏览量

9865 -

闪存存储器

+关注

关注

0文章

21浏览量

9298

发布评论请先 登录

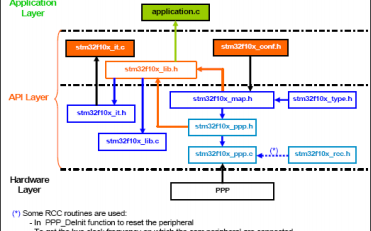

STM32F101xx 和STM32F103xx固件库(CN)

STM32F101xx和STM32F103xx的固件函数库详细整理资料免费下载

STM32F101xx和STM32F103xx微控制器的数据手册免费下载

基于ARM的32位MCU STM32F101xx和STM32F103xx的参考手册资料免费下载

32位基于ARM微控制器STM32F101xx与STM32F103xx固件函数库

32位基于ARM微控制器STM32F101xx与STM32F103xx的固件函数库

AN2604_使用STM32F101xx和STM32F103xx进行RTC校准

STM32F101xx和STM32F103xx微控制器手册

STM32F101xx和STM32F103xx中文教程及参考手册

使用STM32F101xx和STM32F103xx的智能卡接口

STM32F103xx内部资源介绍

STM32F103xx内部资源介绍

评论