锁相环 (PLL) 是电子系统中最通用、最灵活和最有价值的电路配置之一,因此在许多应用中都有使用。它用于时钟重定时和恢复,作为频率合成器和可调谐振荡器,仅举几个例子。因此,在包括无线电接收器和测试设备在内的许多 RF 设备项目中都可以找到 PLL。根据其具体实现,它可以服务于近直流到 GHz 和更高的频率,在系统和电路中发挥许多关键作用。

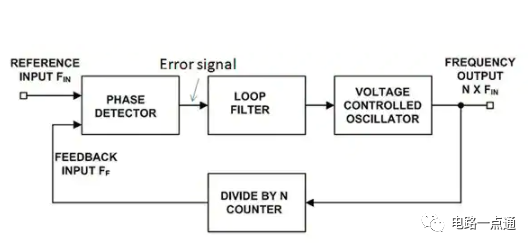

PLL 是闭环(负反馈)架构,基本 PLL 由以下模块组成(图 1):

图 1:基本 PLL 是一个闭环负反馈系统,其中参考信号和 VCO 输出之间的误差用于校正该输出;低通滤波器是建立环路动态的关键要素。

相位/频率检测器 (PFD)(通常简称为相位检测器 PD)将输入信号与参考信号进行比较,并产生与其相位差成正比的误差信号(请记住,相位和频率密切相关,因为频率是相位的时间导数);相位检测器的输出通常进入电荷泵,将小电流差转换为更大的电压

一个低通滤波器 (LPF),它对误差信号的频谱进行整形;这种滤波器的设计通常是工程科学和直观艺术的结合,并且是设置 PLL 操作的许多动态的主要因素

输出相位/频率由误差信号控制的压控振荡器 (VCO)

VCO 输出端的可选分频器,它使 PLL 以参考频率的倍数 N 生成频率;N 可以是整数,许多 PLL 设计支持小数 N 非整数除法

VCO(和分频器,如果使用)的输出进入相位/频率检测器以完成反馈环路。在操作中,误差信号随着相位差的增加而增加。这会以相反方向驱动 VCO 相位,从而减少误差信号。结果,输出的相位被锁定到另一个输入的相位。

当 PLL 输出密切跟踪输入并且误差信号较小且相对稳定时,PLL 被称为“锁相”或简称为“锁相”。根据应用,系统中使用的 PLL 系统的输出要么是 VCO 的输出,要么是 VCO 的控制信号。

当然,PLL 最初是在 1920 年代左右使用真空管设计的。随着 1970 年代第一款大众市场 PLL 作为 IC Signetics NE565 用于 0.001 Hz 至 500 kHz 工作频率的推出,它们的受欢迎程度显着扩大。虽然这部分现在显然已经过时(Signetics 早已不复存在),但其数据表已存档并可在线获取1。

PLL 可以使用模拟、数字或混合信号电路构建。早期的 PLL 是全模拟的,带有模拟鉴相器、低通滤波器、VCO 和可选的分频器;除法器很快升级为数字除法器,以允许整数和小数整数除法。数字 PLL 现在用升降计数器代替相位检测器,该计数器在数字域中执行类似功能,并且还可以使用数字滤波器,误差信号驱动直接数字合成器作为 VCO。

由于其内部结构的模块化、广泛使用和广泛应用,PLL 是莎士比亚或詹姆斯乔伊斯作品的工程对应物,因为它已成为无数文章、论文和书籍的主题。他们通过广泛的定性讨论和高度详细的定量模型对 PLL 进行了广泛的分析;几乎所有此类分析都始于 Gardner 和 Viterbi 的经典著作2,3。

可用的技术论文涵盖了 PLL 的性能,包括每个功能块中的多种噪声、抖动、漂移、非线性、失真和其他电路缺陷,以及多种输入信号的性能。其中包括在时域和频域中检查 PLL 操作的论文;一些专注于简单的一阶模型,而另一些则使用高度复杂的模型来捕捉 PLL 电路和信号的许多真实世界的细微之处。

PLL 参数满足应用目标

与大多数电子电路一样,有一些基本参数适用于几乎所有应用,有些在特定情况下更为关键。通过调整相位检测器、低通滤波器、VCO 和分频器的一些设计细节,PLL 设计可以在这些参数之间权衡性能,以最好地满足应用优先级。顶级因素包括:

工作频率:PLL 及其 VCO 的标称、自由运行频率

工作范围:PLL 和 VCO 将工作的频率跨度。这包括 PLL 可以获取信号并实现锁定的拉入范围,以及一旦实现它可以保持锁定的更宽范围

转换或捕获时间:PLL 捕获并锁定在操作外部限制的信号所花费的时间,这在很大程度上由低通滤波器决定;带宽较窄的滤波器具有较长的捕获时间,但会限制噪声和抖动,而带宽较宽的滤波器具有更快的响应,但允许更多噪声通过 PLL 系统

噪声和抖动:由 PLL 的元件添加并因此出现在其输出端的任何噪声或抖动,即使是完美的信号也是如此。整体噪声品质因数 (FOM) 以 dBc/Hz 表示,有几种不同类型的 FOM

死区:当相位/频率检测器的两个输入非常接近时,检测器可能看不到这一点,因此不会产生错误输出;这有点类似于电子滞后或机械静摩擦

许多其他因素也可能适用于不同应用中的 PLL,例如无杂散动态范围 (SFDR)、失真、截距和温度系数;完整的列表可能很长。

PLL IC 在频率、性能、集成度方面不断提高

为了实现给定应用的最佳性能因素组合,PLL 用户将购买并连接单独的模块:相位/频率检测器、定制滤波器、VCO 和其他元件。当然,模块和混合设备制造商很快通过组合多个单独的 IC 芯片和分立元件,提供完整的 PLL 作为完全表征的单元。

然而,对更高频率的无线系统的需求,例如对软件定义无线电、智能手机、雷达系统和许多其他应用的需求,一直激励 IC 供应商开发能够产生高性能单片 PLL 的工艺和设计。其中许多集成了大部分或所有功能块(取决于频率和所需的性能),从而减少了设计时间、风险、电路板空间和功耗。

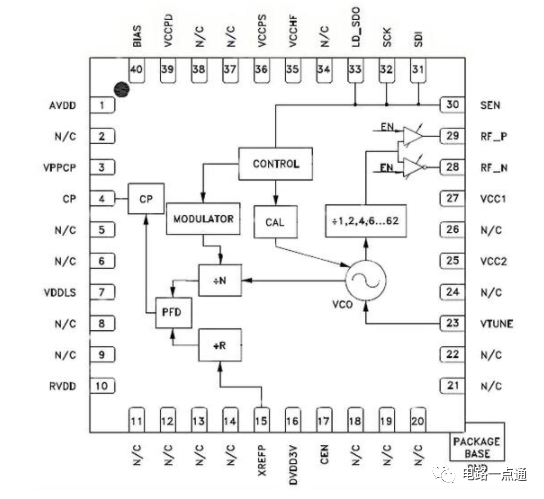

例如,Hittite(现为 Analog Devices 的一部分)的HMC830LP6GE PLL是一个小数 N PLL,工作频率范围为 25 MHz 至 3 GHz。它针对蜂窝/4G 基础设施、中继器和毫微微蜂窝以及通信测试设备,以及具有 -110 dBc/Hz 的超低带内相位噪声、-227 dBc/Hz 的 FOM 和低于 180 fsec 的 rms 抖动的其他应用。

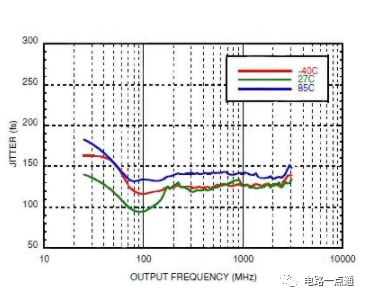

该 IC 包括一个集成 VCO(图 2),传统上它一直是最难集成的功能,同时仍能在高频下实现高整体性能。与大多数 PLL 一样,数据手册有十多个详细图表,显示了 PLL 在各种条件下的许多方面的性能。图 3 显示了 PLL 在不同温度下工作范围内的集成 rms 抖动。

图 2:Analog Devices 的 HMC830LP6GE 代表了过去几年的趋势:将 VCO 与 PLL 的其余部分一起放入 IC 中,同时扩展频率范围且不影响品质因数。

图 3:PLL 数据表通常有许多性能图表,例如 HMC830LP6GE 的这张图表,显示了 -40⁰C、27⁰C 和 85⁰C 时的 rms 抖动 (fsec) 与频率的关系;请注意在该范围内的性能稳定性。

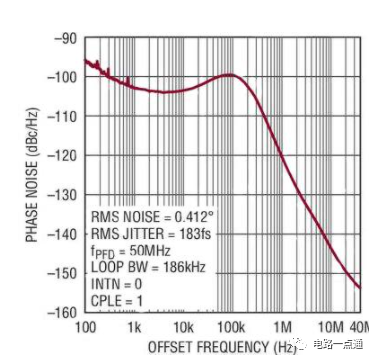

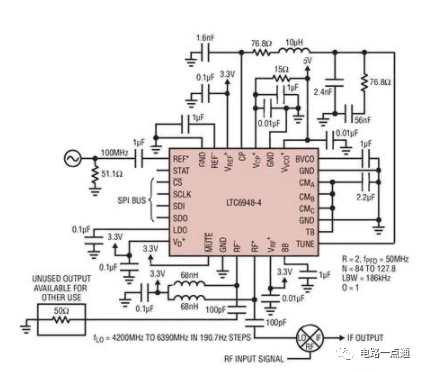

另一个具有集成 VCO 的 PLL 是凌力尔特公司的LTC6948,它是一款 370 MHz 至 6.39 GHz 小数 N 器件,还具有超低噪声。它还包括一个参考分频器、相位/频率检测器、电荷泵、分数反馈分频器和 VCO 输出分频器。归一化带内相位噪底 FOM 为 -226 dBc/Hz,宽带输出相位噪底为 –157 dBc/Hz(图 4)。

图 4:除其他参数外,Linear Technology 的 LTC6948 数据表还包括归一化带内相位本底噪声 FOM 和宽带输出本底相位噪声;后者在最高频率下从 –100 dBc/Hz 下降到 –157 dBc/Hz。

它支持高达 425 MHz 的参考输入频率,以实现快速频率切换。该IC非常适合无线基站(LTE、WiMAX、W-CDMA、PCS)等应用;微波数据链路和军用/安全无线电,它可以用作高速、可调谐 6.39 GHz 宽带接收器的核心(图 5)。

图 5:即使是高度集成的 IC 也需要无源元件支持,正如该基于 LTC6948 的高速、可调谐 6.39 GHz 宽带接收器的原理图所示。

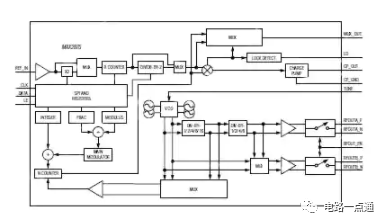

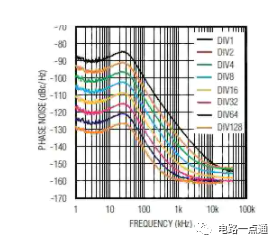

Maxim Integrated 的 MAX2870是一款 23.5 MHz 至 6 GHz PLL,带有小数/整数 N 合成器和 VCO(图 6)。该设备通过覆盖 3 GHz 至 6 GHz 的多个 VCO 实现其超宽频率,可以自动选择或在用户控制下(通过串行接口)选择;用户提供环路滤波器和参考。相位/频率检测器在整数 N 模式下工作至 105 MHz,在小数 N 模式下工作至 50 MHz,并接受高达 200 MHz 的参考频率。PLL 在多个分频器设置中显示出出色的 6.0 GHz 相位噪声性能(图 7)。应用包括无线基础设施、测试和测量、卫星通信和无线局域网。

图 6:Maxim Integrated 的 MAX2870 通过使用多个内部 VCO 实现了 6 GHz 额定值,这些 VCO 可以自动选择或由用户主动选择。

图 7:PLL 供应商再次提供了详细的性能规格,例如 MAX2870 在工作带宽内的相位噪声图,具有不同的分频系数。

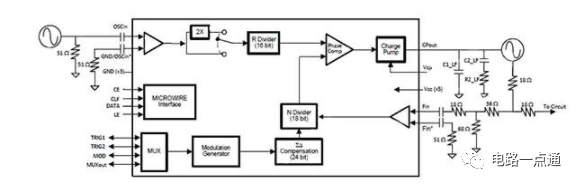

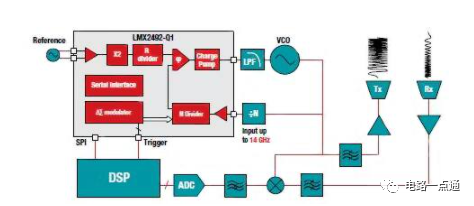

尽管Texas Instruments LMX2492小数分频 PLL(图 8)不包括集成 VCO,但它使用外部 VCO 可在 500 MHz 至 14 GHz 范围内工作;其 FOM 为 -227 dBc/Hz。当与合适的环路分频器结合使用时,它可以用作 77 GHz 汽车雷达系统的核心(图 9);它还包括针对这一重点应用的斜坡/啁啾生成。

图 8:Texas Instruments LMX2492 PLL 不包括 VCO,但在 -227 dBc/Hz 的 FOM 下达到 14 GHz 性能。

图 9:LMX2492 面向 77 GHz 汽车雷达等应用,具有雷达所需的集成斜坡和啁啾功能。

由于其 200 MHz 相位检测器响应,该 PLL 还可用于非雷达应用,例如移动无线、紧凑型射频、雷达模块、微波回程、示波器、频谱分析仪、陆地移动无线电和软件定义无线电。尽管其额定频率很高,但该 IC 采用 3.15 至 3.45 V 电源供电,耗散电流仅为 60 mA。

除了 RF 性能之外,许多 PLL 现在还包括 SPI 或 I 2 C 串行接口,因此系统处理器可以设置和更改一些 PLL 参数,例如增益、滤波器带宽或范围。这使软件能够调整给定电路中的这些因素以满足不断变化的场景,或者允许在多个设计中使用相同的组件。

概括

几十年来,PLL 一直是许多用于通信、合成、时钟、信号生成和信号恢复应用的电子系统的关键部分。新 IC 正在将频率、噪声和抖动性能方面的性能规范推向新的水平,同时将更多功能集成到单个设备中。通过在环路设计本身内添加数字功能,或作为建立 PLL 工作点的控制功能,PLL 的多功能性和灵活性进一步增强。

-

锁相环

+关注

关注

35文章

590浏览量

87945 -

振荡器

+关注

关注

28文章

3858浏览量

139487 -

pll

+关注

关注

6文章

781浏览量

135386 -

信号

+关注

关注

11文章

2812浏览量

77216 -

负反馈

+关注

关注

6文章

218浏览量

30182

原文标题:锁相环 (PLL)电路、信号、模块组成

文章出处:【微信号:电路一点通,微信公众号:电路一点通】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

锁相环(PLL)电路的组成和参数

锁相环(PLL)电路的组成和参数

评论