套刻计量(Overlay metrology)工具可提高精度,同时提供可接受的吞吐量,解决日益复杂的设备中的竞争要求。

在一场永无止境的竞赛中,领先设备的产品套刻公差( overlay tolerances )正在迅速缩小。对于 3nm 代(22nm 金属间距)器件,它们处于个位数纳米范围内。新的覆盖目标、机器学习和改进的光学覆盖系统有助于加快必要的检查,以确保 5nm 和 3nm 节点的良率。

在光刻中,套刻精度(overlay accuracy)已成为最关键的良率限制因素之一。套刻控制(Overlay control)就是要确保一个掩膜层上的特征与下面的层之间的特征精确对齐。对于像 5nm 这样的前沿节点,套刻公差(overlay tolerance :通常为特征尺寸的 30%)必须保持在几纳米以下。“领先的内存和逻辑客户正在运行 2 到 2.5nm 的on-product overlay,”ASML 研究员 Jan Mulkens 说。

一个典型的器件可能有 50 个或更多的掩模层级,其中只有一些是关键层并且需要 EUV (13.5nm),而非关键层使用 ArF (193nm) 曝光。EUV 扫描仪、检测和算法级别的主要进步协同工作,以提供严格的覆盖控制(overlay control )和更高良率的晶圆。

overlay 的一些趋势包括:

通过对光波长不透明的新硬掩模向更长的波长(近红外)移动以对齐层;

更好地模仿设备的覆盖目标;

增加计量采样

ML 算法可以更快地处理大量数据以获得更好的内联结果。

此外,一些检查工具硬件的变化,如卡盘改进,有助于抵消弯曲效应。

EUV 工具级开发

获得良好的overlay从光刻开始。扫描仪的目标是以高分辨率打印微小特征,并精确对齐它们。为了实现这一点,在晶圆和光掩模上都放置了微小的对准标记。在扫描仪中,晶圆台和光罩台将适当的标记相互对齐。扫描每个掩模版的曝光,然后步进、对齐和曝光晶圆上的下一个芯片,直到它完全图案化。

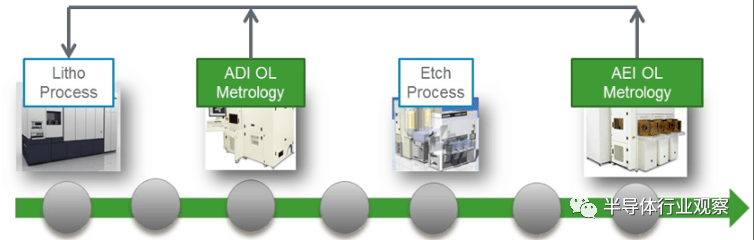

图 1:在光刻图案化后(显影检查后)和特征蚀刻后 (AEI) 测量覆盖层。资料来源:KLA

在光刻cell中,overlay是在非常相似的光学计量系统上测量的,一个位于图案化层之后(显影检查之后),另一个位于蚀刻后 (AEI)。

ASML 应用工程主管 Jim Kavanagh 说:“我们发现,内存客户似乎正在更快地增加蚀刻后检测的使用,而不是在过去它是一个更加静态的事情。” “确保它们捕获蚀刻引起的覆overlay fingerprint 中的差异至关重要,特别是在 3D NAND 通道孔中,晶圆间、批次间和腔室间的差异可能很大. 从逻辑上讲,由于它们具有多种特征类型,因此更难锚定代表设备的 overlay特征,因此他们在 ADI 做得更多。”

在晶圆厂中,每个EUV光刻系统可以使用2-4个覆盖测量工具。ASML、KLA 和 Applied Materials 提供针对两个叠加步骤优化的 CD 和叠加计量工具。使用了基于图像的叠加 (IBO) 方法以及基于衍射的叠加 (DBO, aka scatterometry),并且一些系统结合了这两种技术。覆盖目标具有顶部和底部光栅,因此当以某个角度成像并被检测到时,它会产生与图像中边缘到边缘差异相对应的信号差异。

ADI 和 AEI 之间的反馈以及来自扫描仪传感器的输入用于进行叠加校正。例如,进行 x 和 y 方向的线性校正以及旋转校正。但凭借先进的光刻和收缩功能,扫描仪现在可以实现更高阶的校正,以达到令人难以置信的精度要求。

“在扫描过程中,扫描仪可以纠正平移和旋转错误,但它也可以处理更高阶的纠正,”Fractilia 的首席技术官 Chris Mack 说。die周围划线中的Overlay targets 为覆盖测量提供了基础。“高阶错误不仅仅是四个角落(four corners)发生的事情——例如设备中间的变化——因此晶圆和掩模的扫描运动可以实现这些校正。你拥有的测量点越多,你就能做出越精确的动作。”

边缘放置错误

overlay 的预算不断缩小,不仅因为特征尺寸越来越小,掩模级别越来越高,还因为随机效应。随机指标也会影响叠加和 CD 测量。

“在过去,CD 不均匀性和重叠是我们所谓的边缘放置错误(EPE) 的主要贡献者。但随着缩放,特别是双图案化,EPE 有多种成分,”Mack 说。总 EPE 本质上是工程师打算在晶圆上打印的内容与实际制造的特征之间的差异。按重要性排序,这些包括四个组成部分——CD 均匀性随机性(线宽和线边粗糙度)、OPC CD 误差和全局 CD 均匀性误差。

“EPE 的最大来源是随机指标,因此更多的重点放在减少overlay errors上,因为随机指标很难控制,”麦克说。“事实上,随机指标预计将占 3nm EPE 的 50%。那么这一切对overlay control意味着什么呢?晶圆厂仍然需要制造边缘放置误差小的设备。但现在他们的 CD 均匀性和覆盖预算不到一半。因此,对覆盖和 CD 均匀性的要求比以前缩小得更快。”

其他人指出了类似的问题。“随着 5nm 节点的 EPE 预算持续缩减,EPE 预算的overlay elements缩减最快,场内变化更大,” KLA工艺控制解决方案总监 Andrew Cross 说。

这导致更高的光学叠加采样、改进的叠加测量技术以及在 AEI 和 ADI 引入基于 SEM 的叠加测量。光学计量工具使用 500 至 650nm 范围内的波长,这是许多工艺层和条件的最佳选择,但现在长波长 (900nm) 激光器可以通过不透明硬掩模成像,特别是在 NAND 和 DRAM 中用于特定层。结果是更灵活的计量系统可以满足最大数量的需求。

覆盖层测量、校准

在光刻胶显影后首先检查图案放置,如果overlay不可接受,可以对晶圆进行返工。在大批量制造中,晶圆厂可以监控 CD 均匀性并在每批和每批或可能每隔一批的选定 (6) 个晶圆上覆盖。ASML 的叠加监控方法包括编译和处理大量数据。

ASML 的 Mulkens 解释了覆盖的组件。“客户从划线中的目标进行衍射测量。然后,当然,我们需要知道目标上的测量overlay与设备上的overlay相比如何。我们称之为 device overlay。通常,光学目标的间距为数百纳米,而器件的间距为 20 到 30 纳米。因此,客户可以测量和校准设备偏移量 (MTD)。然后,当然,你仍然不在那里,因为 EUV 可能存在非常局部的错误,随机指标。人们使用电子束系统来测量这些非常局部的误差,可能是几纳米的量级。对于 CD 和叠层错误,您最终可能会产生 4 到 5 纳米的overlay和放置错误。”

SEM 捕获局部随机数据,与叠加测量一起用于确定扫描仪上的叠加校正和 CD 校正。

图 2:扫描仪和计量数据的前馈和反馈,以纠正overlay和 CD 误差。资料来源:ASML

当涉及到新技术的发展和光学测量系统的相关性时,电子束成像被广泛使用。只有电子束工具才能通过检测来自背散射电子的信号来检测埃级的表面特征。在生产中,虽然一些制造商谈到需要使用更多的在线电子束测量,但较慢的吞吐量仍然限制了工具的使用。

由于 SEM 越来越多地用于CD SEM测量,因此 CD SEM 和本地 CDU 测量是否可以组合在一个系统中引发了疑问。

“它们往往有不同的电压要求和其他差异,因此虽然在某些情况下可以将叠加和 CD SEM 结合起来,但这并不典型,”Mack 说。“[使用基于物理的模型],我们正在开发同时进行overlay和随机测量的能力,例如粗糙度以及同时导致边缘放置错误的所有组件。考虑到正确的算法,我们相信这就是行业的发展方向。”

目标修改

覆盖测量依赖于对目标进行的测量——划线中的特征或设备内的选择性特征。目标是具有光栅的薄膜叠层,其使用比设备本身更宽松的尺寸(数百纳米),针对该层量身定制以捕获设备内覆盖。

目标设计在overlay测量精度和准确度方面发挥着重要作用,但也受到划线中的尺寸限制。这会导致一些移动到更小、更详细的目标(每侧 4 到 8µm)。传统的目标是bar-in-bar 或box-in-box 设计,25 x 25µm,但更敏感的版本如图 3 所示。

图 3:目标设计改进了对重叠误差的捕获。

资料来源:SPIE

KLA应用程序开发团队负责人 Shlomit Katz描述了overlay目标设计的最新变化,例如更多地使用莫尔效应目标。使用通过overlay但略微偏移的图案产生的overlay干涉图案,莫尔效应可以被移位、旋转或具有略微不同的间距,从而产生相位感应干涉。NAND 和 DRAM 的新目标“被证明对对称和非对称工艺变化都具有鲁棒性,通过波长提高对比度并提高总测量不确定性,”Katz 说。

曝光前扫描仪中的APC

晶圆上测量有助于实现高质量的曝光,但它们也可以揭示为过程控制回路提供信息的关键信息。例如,晶圆形貌图可检测由于重叠采样可能遗漏的焦点造成的局部重叠误差。

ASML 和 STMicroelectronics 最近提供了使用基于overlay的计算校正的晶圆厂中下一代覆盖控制的一瞥。通过将物理建模与机器学习相结合,他们表明扫描仪测量可用于预测晶圆或批次上的overlay性能,而这些晶圆或批次没有通过计量来检测潜在的偏移。

“为了获得扫描仪的准确性,我们有我们的内置传感器、对准传感器和水平传感器,它们测量每个晶圆,并以非常密集的水平测量晶圆。事实上,这是客户可能拥有的为数不多的表征每个晶圆的高空间指纹的数据集之一。因此,我们推导出一些算法,并将这些传感器与扫描仪外部的测量值与覆盖设备相结合。当您正确执行此操作时,客户可以最大限度地减少扫描仪外部的测量量,或者他们可以使用该数据对扫描仪外部的测量密度进行上采样,”ASML 的 Mulkens 说。

密度正在推动许多变化。“我们看到的一个关键趋势,加上对更高精度和更高精度的需求,是更大的采样以捕获整个晶圆的指纹,但同样重要的是捕捉晶圆和批次之间的差异,”Mulkens 说. “我们在使用基于光学目标的计量工具和蚀刻后测量 ADI 时都看到了这一点。然后,当然,使用电子束工具,人们正在关注本地放置。”

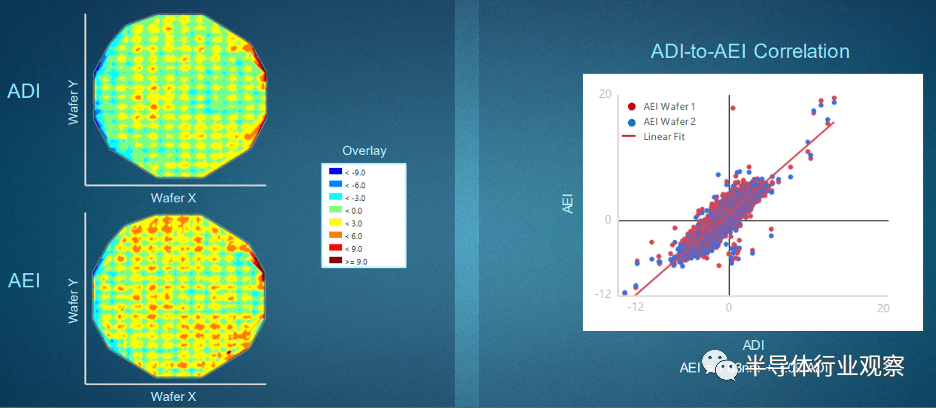

应用材料公司还谈到了对晶圆进行更多采样以提高准确性并检测晶圆间的变化或指纹。例如,该公司的电子束工具旨在同时测量多个级别的边缘位置和 CD。对于稳健的过程,ADI 和 AEI 之间的相关性是叠加过程控制的基础(见图 4)。

图 4:用于覆盖控制的显影后和蚀刻后检查之间的相关性。资料来源:应用材料

结论

虽然最先进设备的叠加控制力求更快地将数据反馈到扫描仪以补偿在线误差,但下一代工具,High NA EUV,将面临其自身的挑战。它使用变形镜头,支持一个方向放大 8 倍,另一个方向放大 4 倍。因此场大小减少了一半,两个掩模的结果在晶圆上缝合在一起。

“借助变形光学器件,6 英寸的掩模导致我们称之为半场,”Mulkens 说。“现在,当您在High NA 系统上打印关键层而在低 NA 系统上打印不太关键的层时,您需要能够将半场与全场匹配,反之亦然。为了提出匹配算法,我们进行了非同心匹配,这将是高 NA 方面的重大overlay创新。”

-

内存

+关注

关注

8文章

3080浏览量

74549 -

光刻

+关注

关注

8文章

330浏览量

30327 -

机器学习

+关注

关注

66文章

8459浏览量

133371 -

EUV

+关注

关注

8文章

609浏览量

86345

原文标题:Overlay如何与EUV图案保持同步

文章出处:【微信号:半导体设备与材料,微信公众号:半导体设备与材料】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

EUV光刻机就位后仍需解决的材料问题

NI_vision Overlay的示例

包含overlay的图像怎么保存啊

EUV热潮不断 中国如何推进半导体设备产业发展?

一幅图上有很多个overlay,如何清除指定区域的overlay呢? 用clear overlay是清除所有的。

CAD图案填充:什么是CAD线图案?

台积电要想保持优势,就必须要加快7nm EUV的进程!

台积电为保持业界领先地位大规模购买EUV光刻机

极紫外(EUV)光刻技术将如何影响掩模收入?

基于Video Overlay Circuit视频系统的参考设计

euv光刻机原理是什么

EUV***市场:增长趋势、竞争格局与前景展望

为什么需要Overlay网络?Overlay网络是如何形成的?Overlay网络的应用有哪些?

Overlay如何与EUV图案保持同步

Overlay如何与EUV图案保持同步

评论