前言:

双电阻和三电阻的采样方案比较常见了,原理比较简单。随着成本的压力和技术的进步,现在单电阻采样的方式越来越常见。

正文:

双电阻和三电阻,为了能采样到三相电流,必须在零矢量时刻采样,基于Ia+Ib+Ic=0前提下,三相电流形成了回路。

单电阻采样不能在零矢量时刻采样,因为零矢量时刻,唯一的直流电阻采样到的电流就是零。

那么反过来说,单电阻采样必须在非零矢量时刻进行。

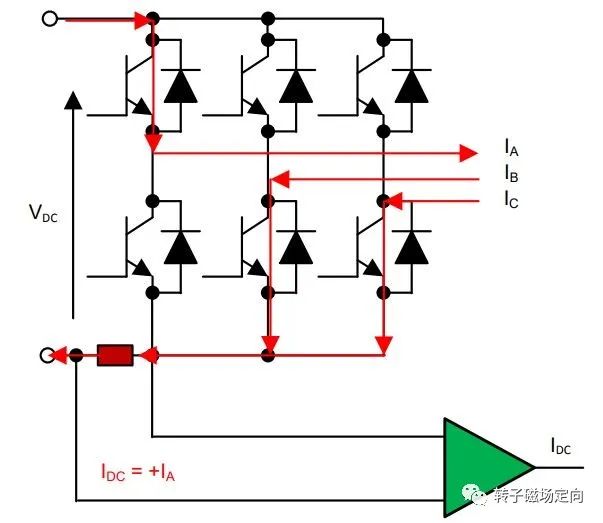

100矢量

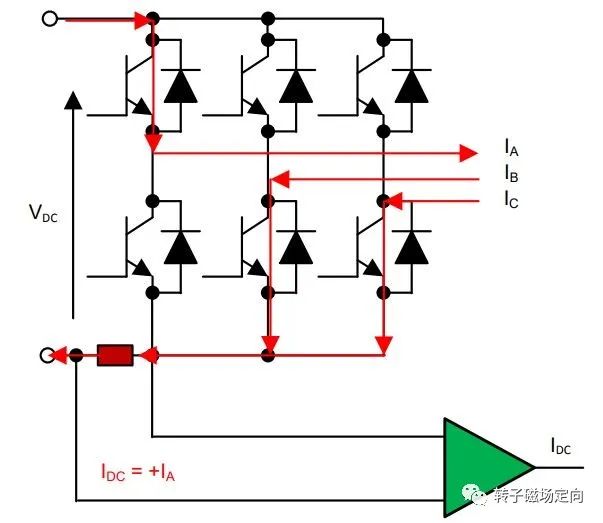

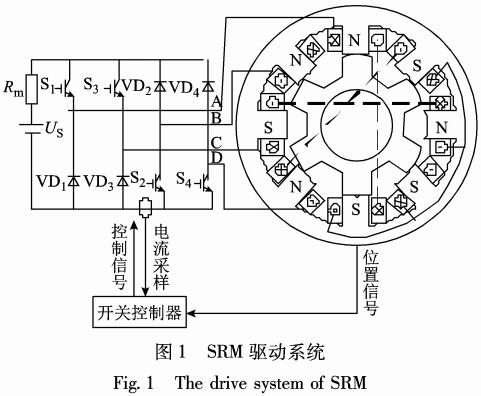

采用七段式SVPWM模式下,当100矢量下,A相开上管,B/C相开下管。

在电动模式下,电流从A相上管MOSFET流入电机,然后从电机流入B/C下管MOSFET。

在发电模式下,电流从B/C相下管的续流二极管流入电机,从电机经由A相上管续流二极管流入直流电容。

无论上述哪种情况,流经DC-采样电阻的直流电流都是Ib和Ic,根据Ia+Ib+Ic=0的前提下,可以采样到Ia。

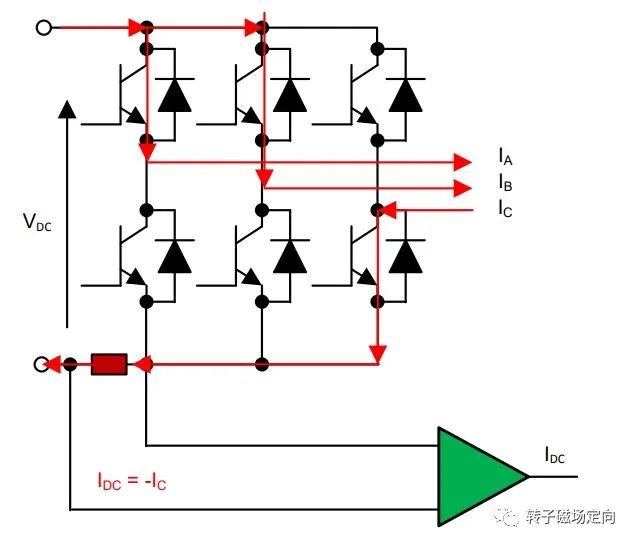

110矢量

采用七段式SVPWM模式下,当110矢量下,A/B相开上管,C相开下管。

在电动模式下,电流从A/B相上管MOSFET流入电机,然后从电机流入C下管MOSFET。

在发电模式下,电流从C相下管的续流二极管流入电机,从电机经由A/B相上管续流二极管流入直流电容。

无论上述哪种情况,DC-直流电流的都是Ic,进而采样到Ic。

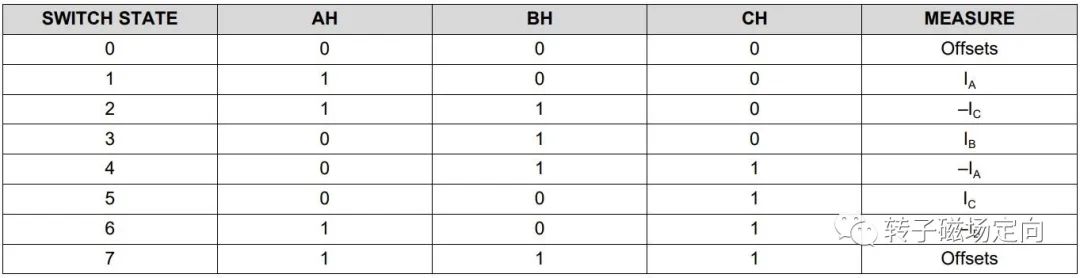

所以说,在同一个开关周期内,两次非零矢量下,根据不同的矢量,直流电流代表了不同的相电流。矢量和相电流对应关系如下:

矢量和相电流对应关系

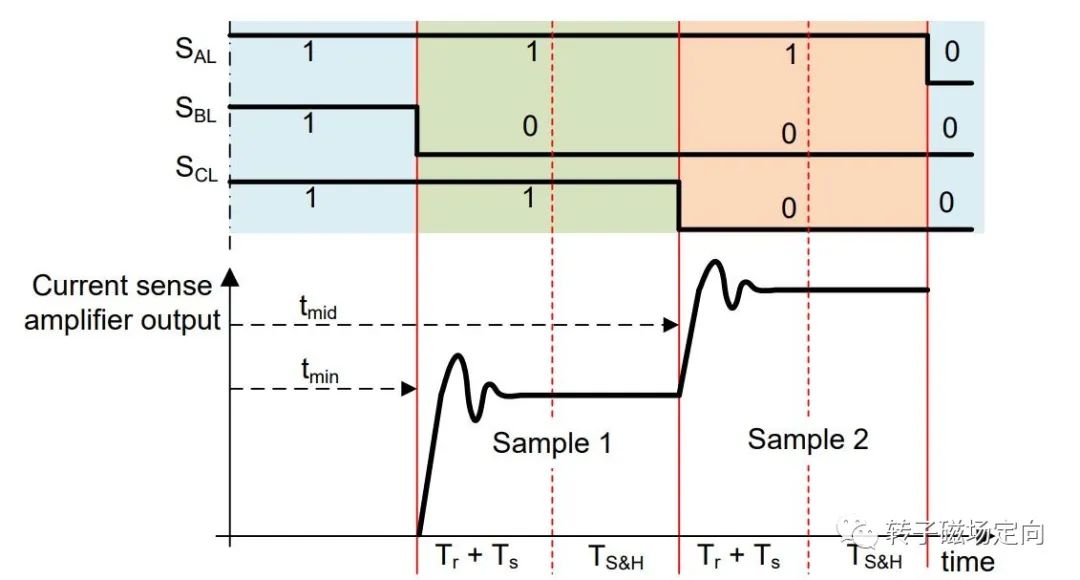

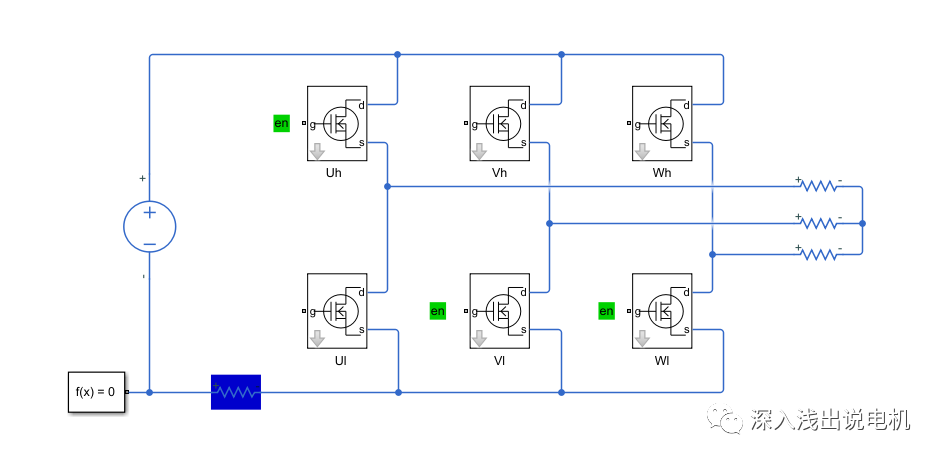

一个开关周期内两次采样

如上图所示,在000和111矢量下,直流电流为零,这时候采样直流电阻电压,只能作为电流采样偏置使用。

在101和100矢量下,可以分别采样两次相电流,并且因为矢量不同,是不可能两次采样同一相电流的。

对于一次采样行为,该矢量被分为两段,一段是相电流的上升和稳定时间,另外一段是等电流稳定后即可进行ADC采样。所以说,采样点是不固定的,采样得到的电流和相对应关系也是和SVPWM矢量息息相关的。

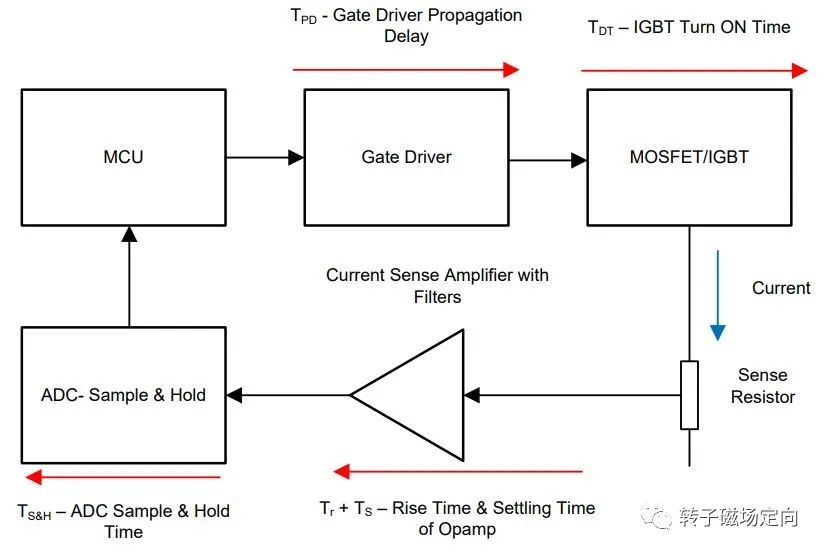

电流采样回路的延时

电流采样的延时,具体包括以下环节:

Tr 运放的压摆率决定的上升时间,us级

Ts 运放输出稳定时间,us级

TPD MOS门级驱动器的传输延时,ns级

TS&H ADC采样、保持、转换时间,us级

TDT 开关器件的开关延时以及死区,us级

一般确定采样点,需要考虑以上延时。因为所有的采样点基于MCU的计数器来确定,但是最后执行到开关元器件,再到最后运放建立输出,是存在以上延时的。重点是运放输出,以及开关器件执行的延时以及死区导致的偏移。

另外ADC触发采样后,要留足宽度用于ADC的保持、转换。

当处于某些矢量情况下,采样宽度不够时,就必须对计算出的矢量进行偏移操作,移动出足够用于采样的脉宽,这就是单电阻采样的难点。

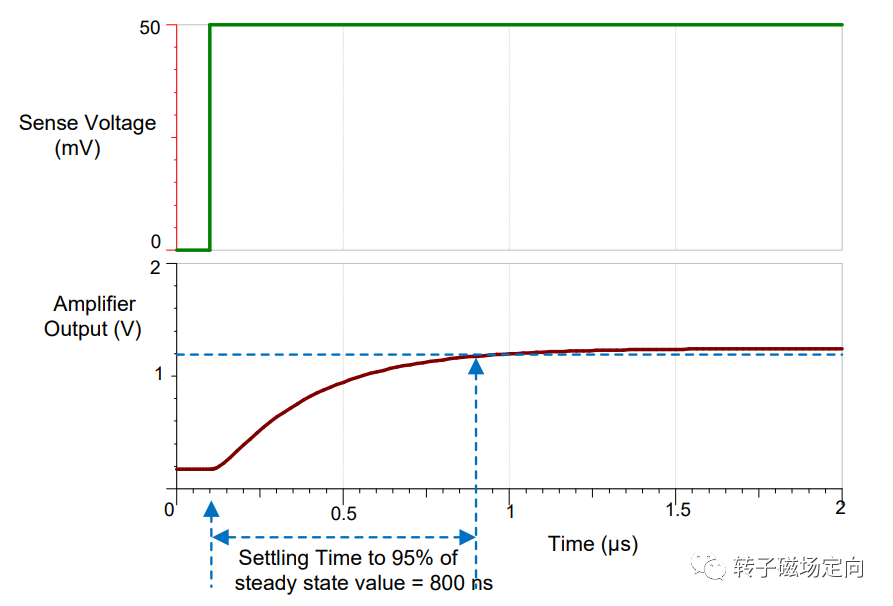

压摆率:

压摆率,直接决定了运放的输入到输出上升的时间。其稳定时间取决于运放的带宽,增益以及精度等其他指标。

运放的输入到输出

以上图为例,绿色是检测电压,到运放1.2V的输出存在800ns的延时,说明其压摆率为:1.2V/800ns=1.5V/us,这个指标是偏低的。

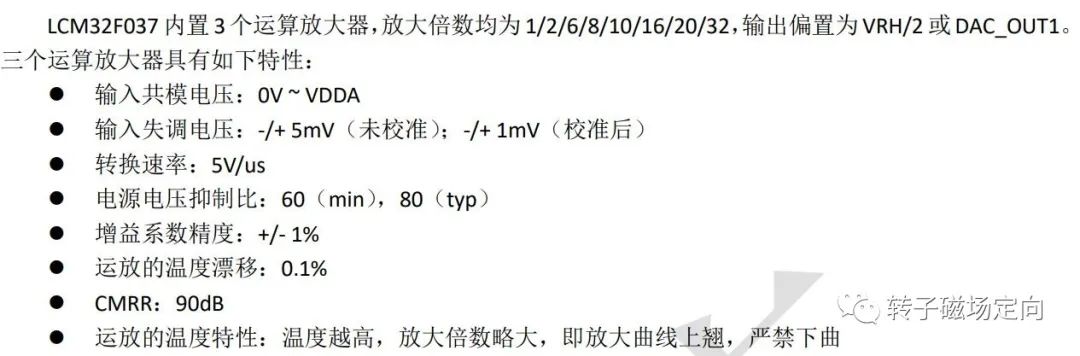

以领芯微的LCM32F037系列为例,压摆率达到了5V/us,保证了运放输出能够快速建立。

领芯微MCU内置运放

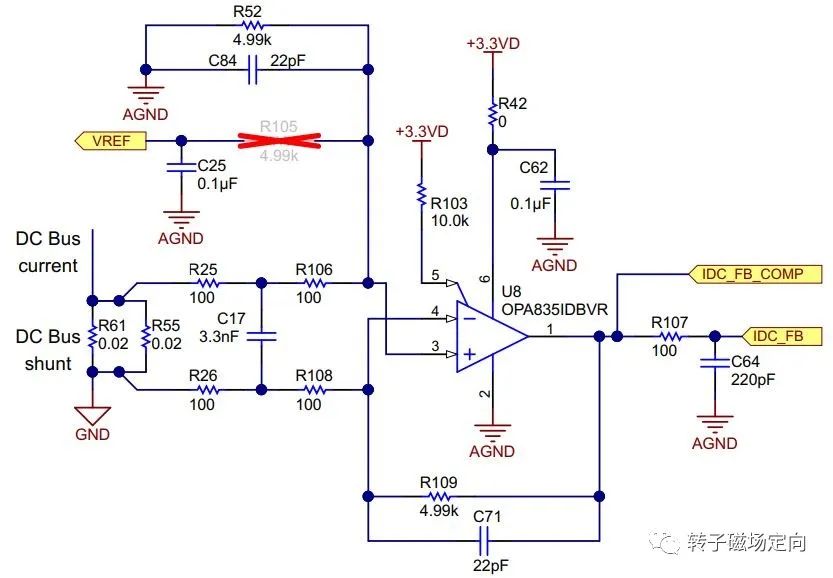

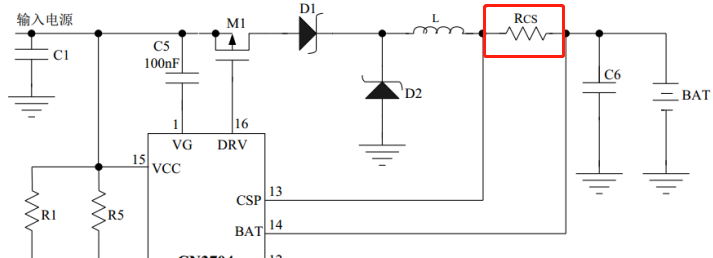

TI常用的单电阻采样电路如下图:

TI单电阻采样电路

上图是经典的差分放大电路,DC Bus shunt 是单电阻,R25+R106与R26+R108,R109,R52构成差分放大电路,+3.3VD提供直流偏置。

大家需要注意的是,整个采样电路,输入端口仅仅只有C17这一个差分滤波电容,C84属于共模噪声抑制电容。

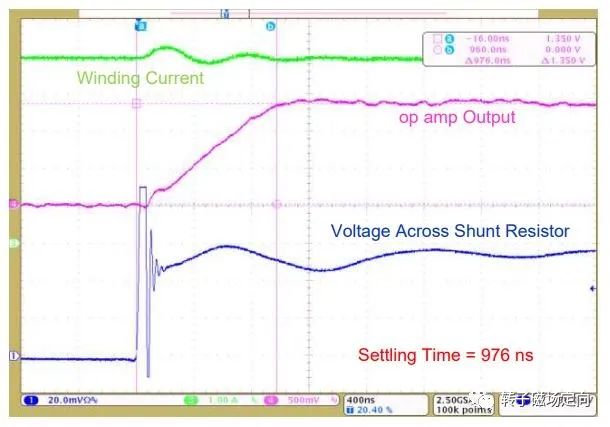

当R25=R26=100ohm, C17=3.3nF, 运放输入和输出是如下波形:

运放稳定时间976ns

运放的上升加稳定时间大约是976ns,蓝色是电阻流过电压,因为线路板寄生电感以及开关器件的耦合,产生了较大幅度尖峰,所以需要C17进行滤波,设置相对低的滤波截至频率,虽然上升时间较长,但是可以快速稳定,防止运放输出的振荡。

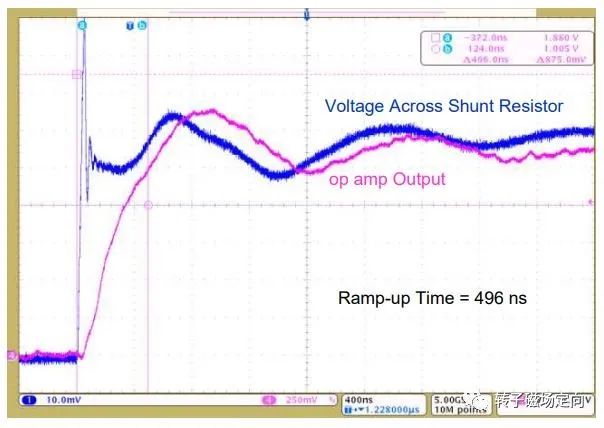

如下图,R25=R26=100ohm, C17=330pF, 可以快速上升496ns, 但是运放输出会振荡,需要一定的稳定时间。

运放输出振荡

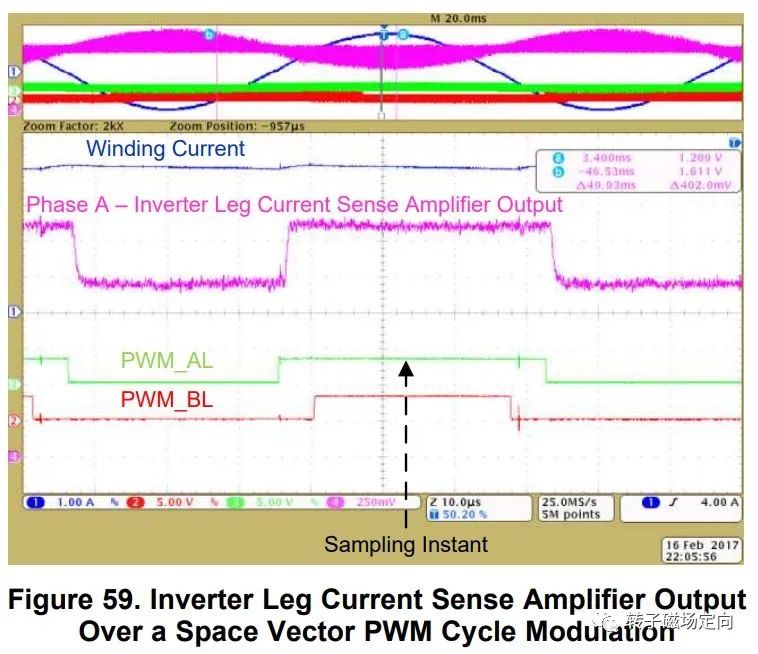

错峰采样

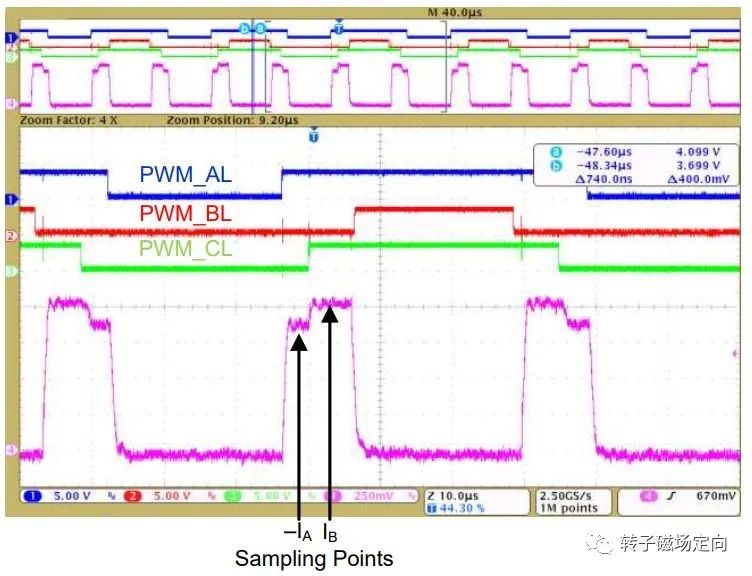

前文提过,单电阻采样,必须在两个非零矢量的时候分别采样两相相电流。如下图所示,粉红色是运放输出电压,因为运放电路设计合理。所以运放输出快速建立并稳定,ADC能够采样到真实电流:

非零矢量错峰采样

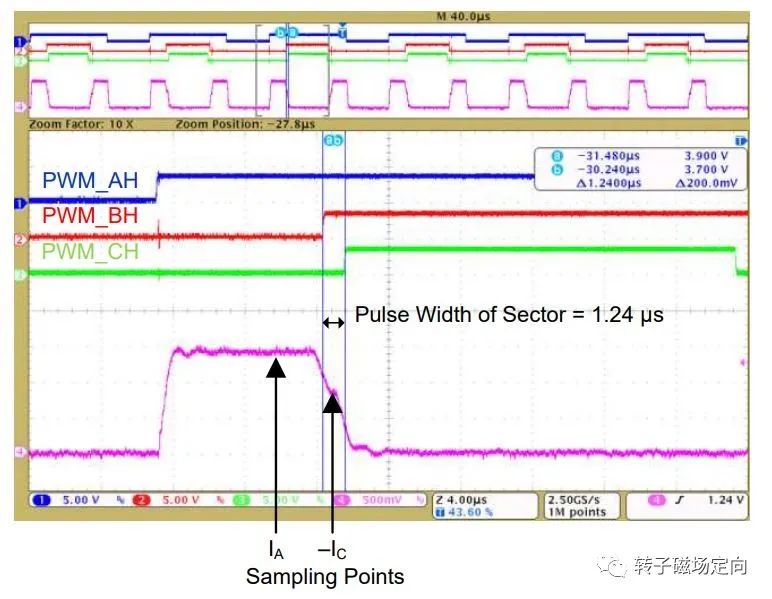

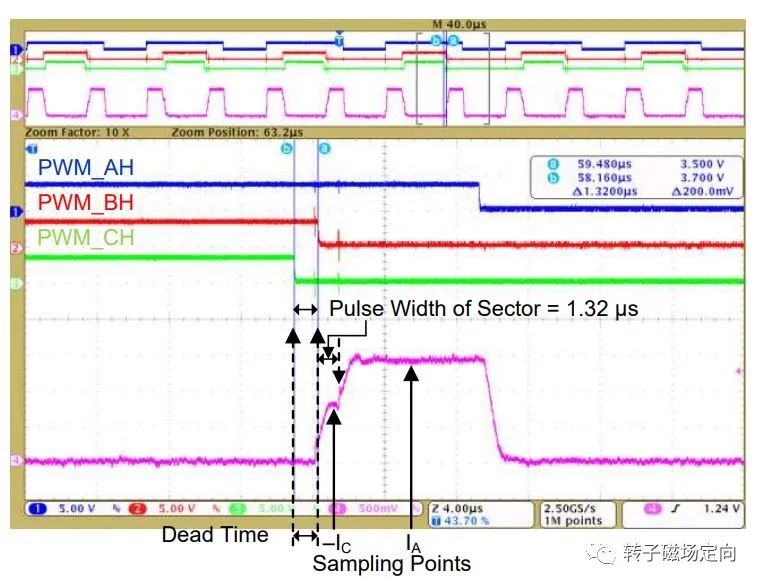

如下图,如果ADC性能好,采样电路噪声小,哪怕采样窗口仅仅1.24us也能采样到相电流。这种情况,说实话我觉得比较极限。一般能做到3us,已经很好了。

采样窗口仅仅1.24us

下图我是没想明白,为什么死区会造成电流的延时出现?这里就必须考虑偏移采样点。

电流偏移到采样窗口外

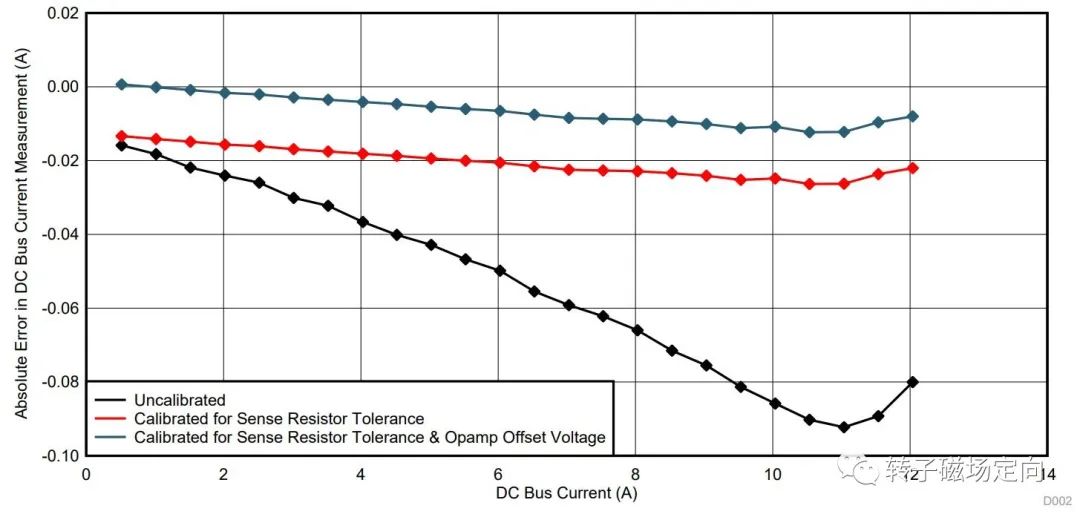

实际项目,除了合适的采样窗口和采样点,电路设计,还需要对采样增益和采样偏置进行校正,有效提升了采样精度:

采样误差

双电阻/三电阻采样

对于双电阻或者三电阻采样,因为是在零矢量的中间采样,可以留出更大的脉宽,所以说单电阻采样对运放带宽要求更高。

双电阻采样点

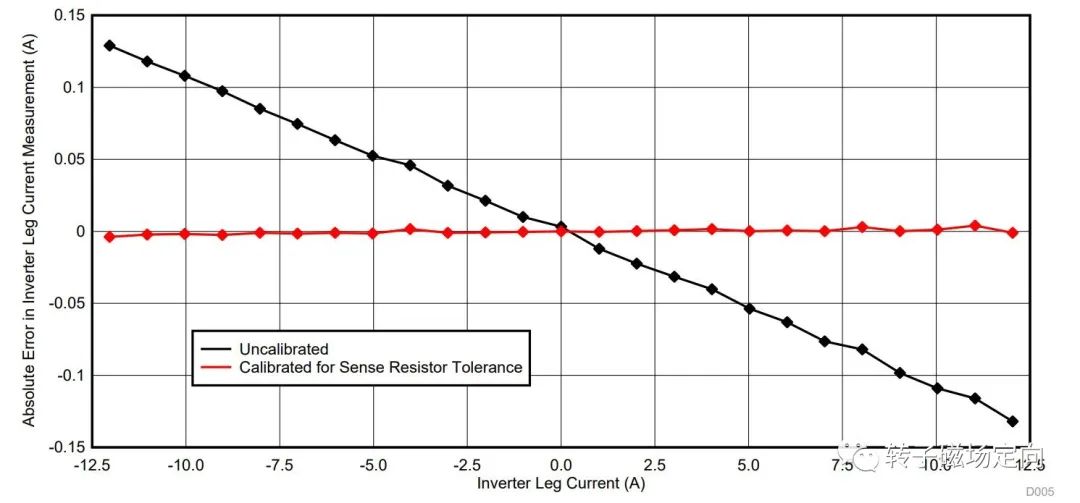

双电阻采样也需要对采样增益和采样偏置作校正,校正前后误差对比如下:

双电阻采样误差校正对比

领芯微参考设计

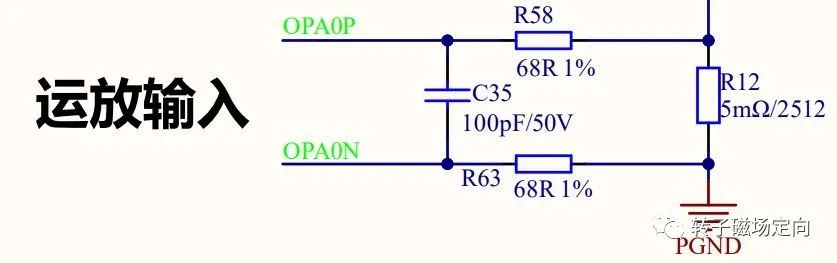

领芯微单电阻采样

领芯微的单电阻设计和TI类似,除了C35的100pF滤波电容,没有其他电容。尤其是OPA0N/OPA0P,千万不能对地加滤波电容,会直接改变电阻上电压的波形,最后影响运放输出的建立,采样失败。MOS的ds也不要加电容,有可能导致电流波形的畸变,因为单电阻采样对电流流过电阻的信号是非常敏感的。

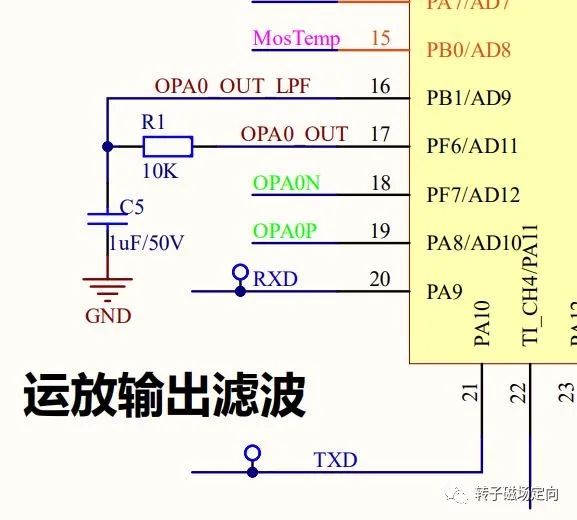

C35滤波后电压直接输入MCU,内置运放和差分放大电阻,集成度相当高。

运放接MCU

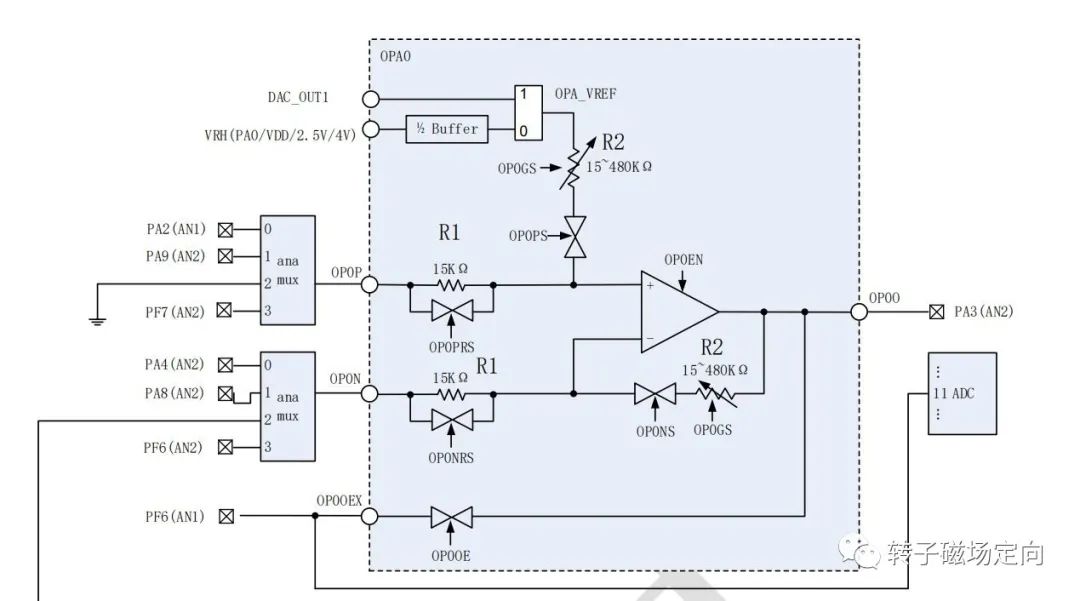

运放内部结构

运放的内部结构如上图,通过OP0P和OP0N输入到运放,内部电阻R1是15k,R2可以从15k到480k通过寄存器配置,放大倍数从1到32倍。集成了ADC_REF/2的偏置电压,运放输出和ADC,比较器,输出都可以灵活配置。

-

驱动器

+关注

关注

54文章

8402浏览量

147833 -

电阻器

+关注

关注

21文章

3869浏览量

62659 -

续流二极管

+关注

关注

5文章

143浏览量

14320 -

SVPWM控制

+关注

关注

0文章

26浏览量

5667 -

直流电容

+关注

关注

0文章

10浏览量

4414

发布评论请先 登录

相关推荐

AN6415_基于MM32SPIN0280的PMSM单电阻采样矢量控制方案(中文版)

Simulink永磁同步电机控制仿真:单电阻采样时序及具体实现

解析单电阻采样的原理以及注意点

解析单电阻采样的原理以及注意点

评论