这一节来说一下简单的办法,或是说是一些常规经验。

经验1:抓大放小——如果噪声A是不相干噪声B的3倍或以上,那么我们完全可以忽略噪声B

“抓大放小”,指的是只评估大的主要的噪声源,忽略掉小的噪声源。

问题的关键在于如何判定哪些噪声源是主要的,哪些噪声源是次要的。了解主要的噪声源不仅能简化计算,也能告诉我们为了降低总噪声水平,需要关注哪些因素。比如如果运放电流噪声占主要部分,我们可以用一个 CMOS 运放,来代替 Bipolar 运放,因为CMOS的电流噪声一般要比Bipolar运放的噪声小,另外,如果电阻噪声是主导的,我们可能就需要减小电阻值。

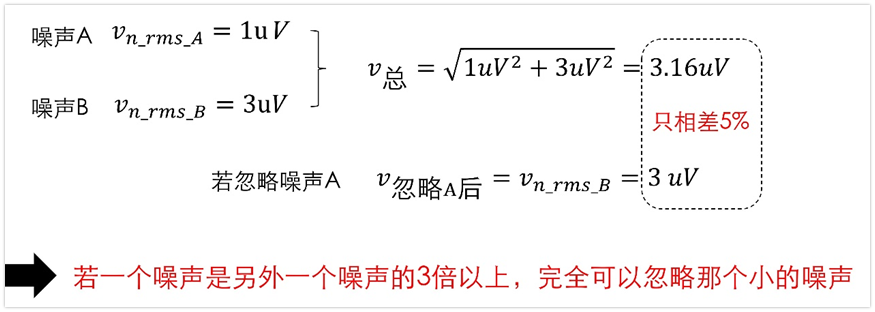

判断的方法:如果噪声A比不相干噪声B大3倍及以上,那么我们完全可以忽略噪声B。

为什么是这样呢?

举个例子,如果噪声A为Vrms_A=1uV,不相干噪声B为噪声A的3倍,即Vrms_B=3uV,根据上一节的内容可以知道,A和B叠加之后的噪声有效值大小为2者的平方和根,即为3.16uV。如果我们忽略较小的噪声A,只看B的噪声,那么就是3uV,其与3.16uV其实是相差不大的,误差只有(3.16-3)/3.26=5.3%。如果噪声B比噪声A大得更多,显而易见,忽略A带来的误差更小,总噪声基本就等于噪声B了,这个原因其实主要是因为平方和的关系,兄弟们可以算算差10倍的情况,误差只有0.5%。

对于噪声分析来讲,由于平方和的原因,差异会被放大,因此,很多时候,小的噪声都是可以忽略的。

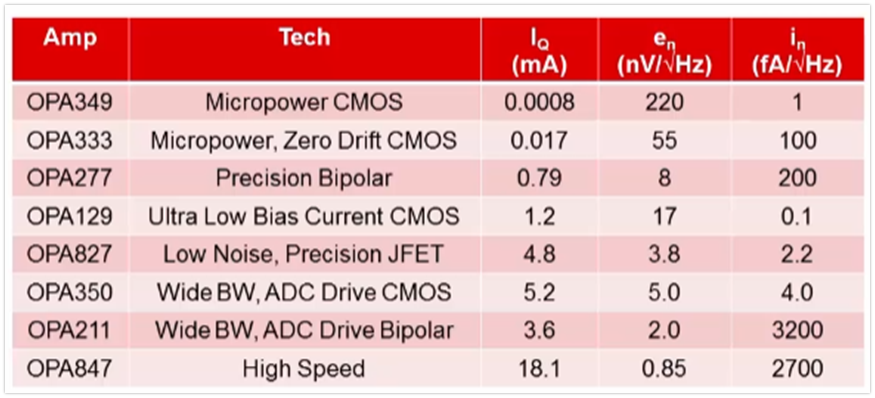

经验2:JFET/CMOS类型运放的电流噪声通常可以忽略

多数 CMOS 运放,电流噪声在fA/√Hz级别,Bipolar运放则在pA/√Hz级别。当电阻非常大时电流噪声则需要重点考虑,采用 100kohm 或者以上的大电阻,可能需要采用CMOS 或JFET 运放。

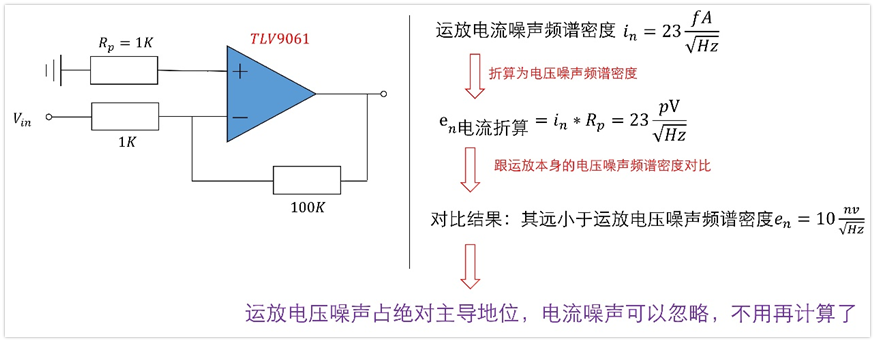

经验3:将运放电流噪声频谱密度乘以相关电阻,可转化为电压噪声频谱密度,然后与运放本身的电压噪声频谱密度对比,如此可以评估电流噪声是否主导。

我们一般评估噪声,最终还是看对输出端噪声电压的贡献,因为电流乘以电阻才等于电压,因此,最终的噪声大小还跟电路中电阻的取值有很大的关系。显然,电阻越大,那么噪声电压就越大。反之电阻越小,那么噪声就越小。

所以说,如果电阻值非常小,电流噪声常常都是可以忽略的,比如对于小于1K的电阻来说,即使使用的是 bipolar 运放,电流噪声一般也可以忽略。

确定电流噪声是否是主导,最简单的方法,就是将电流噪声频谱密度转换为等效的电压噪声频谱密度,然后将其与运放的电压噪声频谱密度直接对比就可以知道。这个其实就是利用前面的“抓大放小”经验原则,如果电压噪声要比电流噪声大很多,那么电流噪声就不用管了。

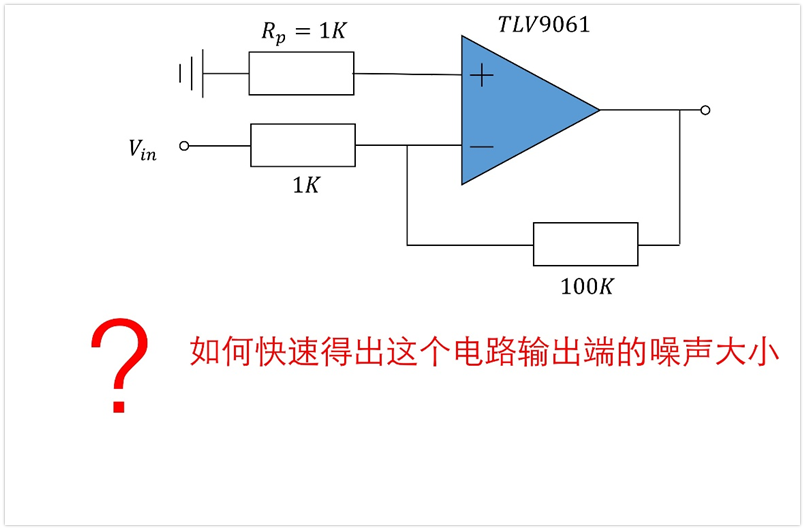

以TI的TLV9061为例,其宽带电压噪声频谱密度为10nV/√Hz,其电流噪声频谱密度为23fA/√Hz

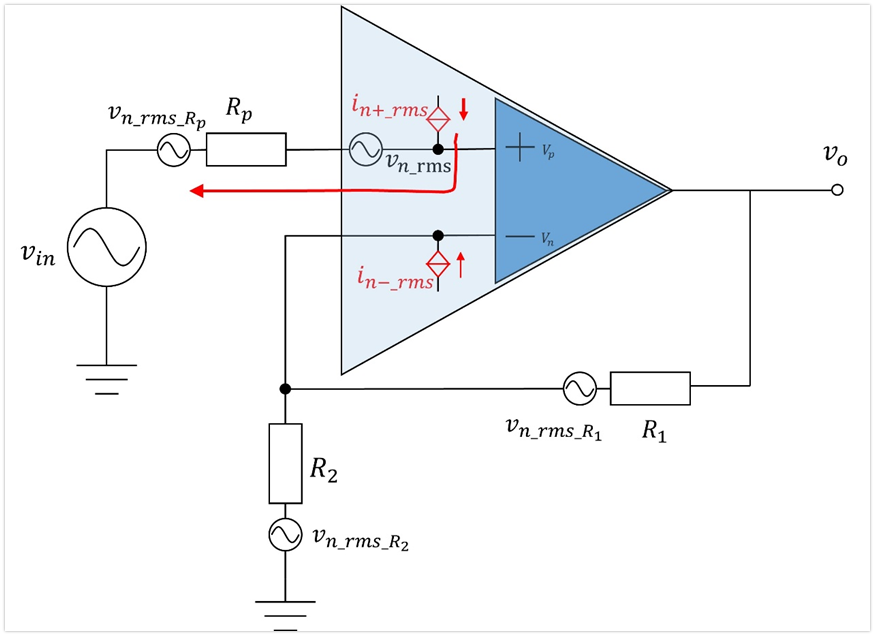

如果我们用它搭建下面的运放电路,将电流噪声频谱密度转化为电压噪声频谱密度,折算后为:e折算=23fA/√Hz*Rp=23pA/√Hz。这个值也是远小于运放本身的电压噪声频谱密度(10nV/√Hz)。那么结合经验1,我们完全可以忽略电流噪声,不用再深入去计算电流噪声具体是多少。

这里可能有一个疑问,为什么是乘以Rp?

从运放噪声电路模型上看,同相端的噪声电流全部都流过了Rp,即噪声电流引起同相端电压变化就是噪声电流乘以Rp。

如果去掉Rp,那么电流噪声引起的噪声输出就是0吗?

当然不是的,前面我们已经知道了,Rp是平衡电阻,其一般等于R1和R2的并联值大小。即使我们干掉这个电阻,同相端电流噪声引起的噪声电压为0,但是反相端同样也有电流噪声,这个是忽略不了的,其大小就是反相端噪声电流乘以R1和R2的并联值,大多数情况下也Rp乘以噪声电流。

所以说,去掉Rp仅仅是将同相端电流噪声的影响降低到0,反相端并不会有什么影响,因此并不会导致总的电流噪声有量级的变化。反之,去掉平衡Rp可能会有负面影响。

并且,一般电路Rp阻值就是R1和R2的并联值,因此同相端和反相端的电流噪声是一样的,所以我们计算一次就好了,除非说是电阻失配。因此我们评估噪声量级的时候,直接用Rp来计算下就可以了。

另外一方面,如果我们发现电流噪声频谱密度转化为电压噪声频谱密度后,比运放本身的噪声电压频谱密度还大,那就说明了我们的电阻取值过大,需要减小阻值。

经验4:当系统带宽比 1/f 噪声的拐点频率大10 倍以上,1/f噪声便可以忽略不计。对于大多数精密运放,噪声拐点频率是在1Hz到1kHz之间,因此对于带宽大于10kHz的系统,几乎可以不考虑 1/f 噪声的影响。

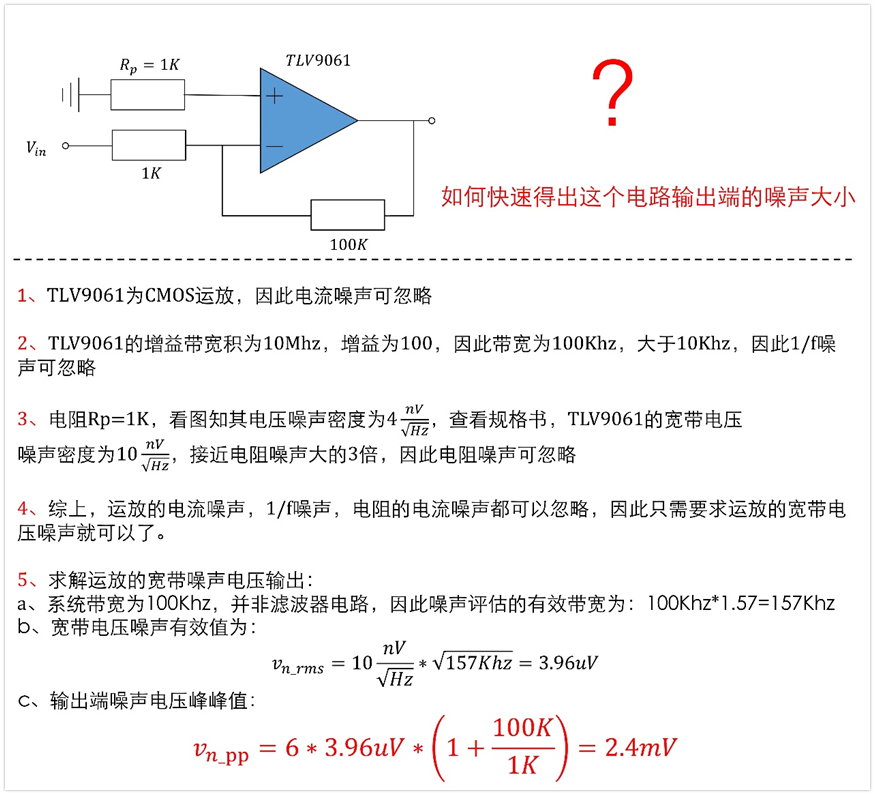

以上面的电路为例子,放大倍数为100倍,tlv9061的增益带宽积为10Mhz,因此其带宽为10Mhz/100=100Khz,是大于10Khz的。根据经验4,大于10Khz可以忽略1/f噪声,因此,我们不用再去详细计算1/f噪声了。

经验5:如果说运放本身的电压噪声频谱密度大于3倍的电阻噪声电压频谱密度,那么电阻的噪声也是可以忽略的。反之,则说明我们的电阻取值不合理,需要降低电阻阻值。

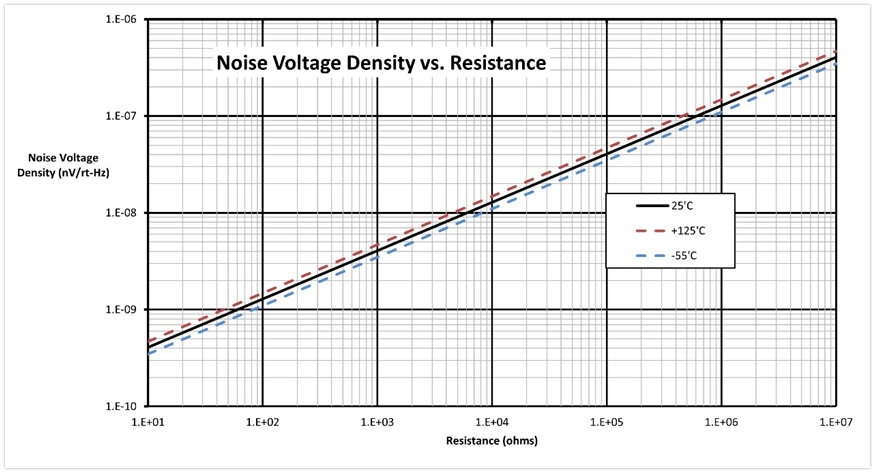

还是以这个电路为例,电阻Rp=1K的电压噪声频谱密度可以通过下图快速查出,其值为4nV/√Hz,运放本身的宽带电压噪声频谱密度为10nV/√Hz,只有2.5倍的关系,并没有到3倍,但也相差不多,至少说明电阻噪声非主导地位,但是也不是特别小。

按照经验5来说,这个电阻其实并不是特别合理,小一点会更好,500Ω电阻噪声会降低到3nV/√Hz,因此,如果选用500Ω左右的电阻应该是更好些的(仅仅从噪声角度)。

不过,我们真正设计电路的时候,并非一刀切,虽然这里说以3倍为界限,现在2.5倍那是一定不行吗?当然也不是,现在还有2.5倍的关系,说明噪声的主导地位依然是运放本身的噪声,并非电阻噪声,降低电阻阻值是可以降低噪声,但是收益不会特别高,另外一方面,降低阻值必然会增加功耗,如果对功耗非常敏感,电阻自然也不能太小。我们设计电路要综合考虑各种因素,根据需求来调整。

就上面这个电路而言,我们假设Rp这个电阻依然是1K。评估噪声的时候,如果是我,尽管电阻噪声只有2.5倍,我会认为其离3倍很接近,为了省事,会不去计算电阻的噪声的。其次,这个3倍本身就是经验值,前面知道,3倍带来的误差是5%左右,2.5倍的话,计算一下带来的误差也只是7.7%左右,粗糙评估完全没问题。

噪声计算举例

以上的经验准则我也是详细的解释了一番,所以还是显得有点啰嗦,现在我们举例实操一下,还是用上面那个电路吧,说明下计算全过程。

计算过程:

以上就是运放噪声评估简单办法的过程,可以看到,运用这几条经验,评估出来还是挺快的。至于精确的评估结果,原谅我,那个过程太繁琐了(可见上一期文章“运放-8-运放的噪声评估的来龙去脉”),我懒得算了。。。

小结

本文介绍了下运放噪声评估的简单易行的办法,主要参考的是TI的视频课程:TI 高精度实验室放大器系列 - 噪声4,链接如下:

https://edu.21ic.com/video/2596

几条经验规则汇总如下:

经验1:抓大放小——如果噪声A是不相干噪声B的3倍及以上,那么我们完全可以忽略噪声B。

经验2:JFET/CMOS类型运放的电流噪声通常可以忽略。

经验3:将运放电流噪声频谱密度乘以相关电阻,可转化为电压噪声频谱密度,然后与运放本身的电压噪声频谱密度对比,如此可以评估电流噪声是否主导。

经验4:当系统带宽比 1/f 噪声的拐点频率大 10 倍以上,1/f噪声便可以忽略不计。对于大多数精密运放,噪声拐点频率是在 1Hz 到 1kHz 之间,因此对于带宽大于 10kHz 的系统,几乎可以不考虑 1/f 噪声的影响。

经验5:如果说运放本身的电压噪声频谱密度大于3倍的电阻噪声电压频谱密度,那么电阻的噪声也是可以忽略的。反之,则说明我们的电阻取值不合理,需要降低电阻阻值。

原文授权自:硬件工程师炼成之路

如果看到这里,请点赞、收藏、分享三连!

限时免费扫码进群,交流更多行业技术

推荐阅读▼

电池、电源

硬件文章精选

-

CMOS

+关注

关注

58文章

5735浏览量

236057 -

噪声

+关注

关注

13文章

1125浏览量

47513 -

运放

+关注

关注

47文章

1169浏览量

53262 -

JFET

+关注

关注

2文章

142浏览量

22148 -

Bipolar

+关注

关注

0文章

6浏览量

6666

发布评论请先 登录

相关推荐

运放的噪声评估简单办法及举例

运放的噪声评估简单办法及举例

评论