前言

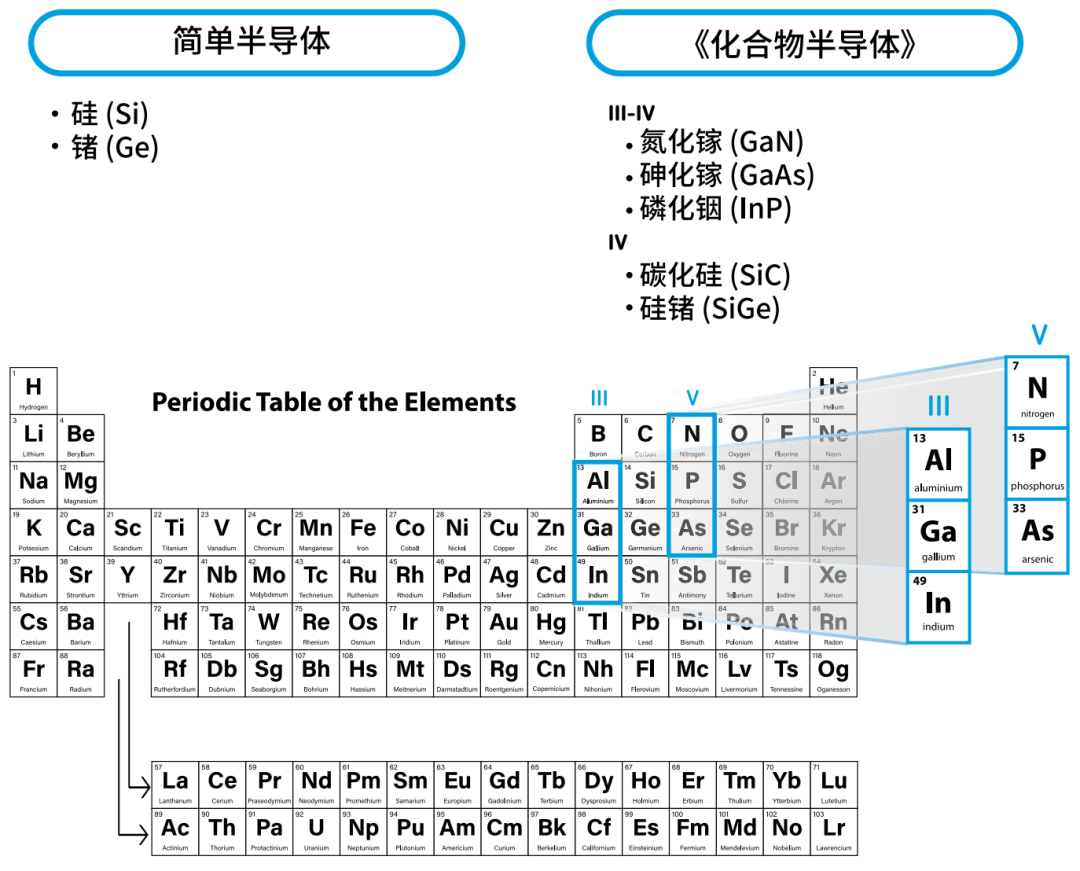

在电动汽车的逆变器中采用碳化硅 (SiC) 的理由非常充分。在取代传统的硅基逆变器时,SiC 解决方案将带来约 5-10% 的效率提升。这意味着更多的电力被输送到电机,而不是浪费在直流-交流电力转换过程中。虽然进行这种转变是有成本的,但通过减少车辆昂贵、笨重的锂电池,可以得到更多的回报。因此,世界各地的汽车制造商都在开发 SiC 逆变器,并且对碳化硅 (SiC-MOSFET) 和关键碳化硅衬底本身的需求从未如此之大。据多位分析师预测,2023 年 SiC 市场价值将达到 10-20 亿美元,并且复合年增长率达到 30%。 然而,关于这个新兴行业的未来仍然存在一些重要问题。最令人担忧的是碳化硅衬底的成本和供应。尽管Wolfspeed、Coherent和其他公司宣布在不久的将来增加晶圆供应,但材料的可用性仍然是行业的一个具有挑战性的限制,导致交货时间长和成本高。

此外,最初在 2017 年推出 Model 3 时引发 SiC 热潮的特斯拉宣布,他们将减少未来低成本、低功率汽车中SiC 的使用量。这其实可以被视为一个积极因素:这最终表明 SiC MOSFET 将用于低功率、大规模生产的电动汽车,而迄今为止 SiC 主要局限于高功率/豪华车领域。然而,鉴于该解决方案据传是混合 Si IGBT – SiC MOSFET 解决方案(尽管所有 SiC解决方案都有价值),汽车制造商仍然面临着降低 SiC 芯片成本的压力。PGC Consultancy 和 Exawatt 的成本分析显示,衬底占成品芯片成本的 40-50%,市场需要找到这种最基础材料的降本空间。

鉴于 SiC 衬底的稀缺性和成本,Soitec 的 SmartSiC 产品成为市场就该问题最常讨论的主题之一也就不足为奇,此外还有 Wolfspeed 向 200mm 的过渡以及中国厂商在市场上的崛起等。在深入探讨 Soitec 的 SmartSiC 产品时,我们着手解释它是什么、它对设备技术和成本可能产生的潜在影响以及其技术和运营模式面临的主要挑战是什么。

SmartCut 流程概述

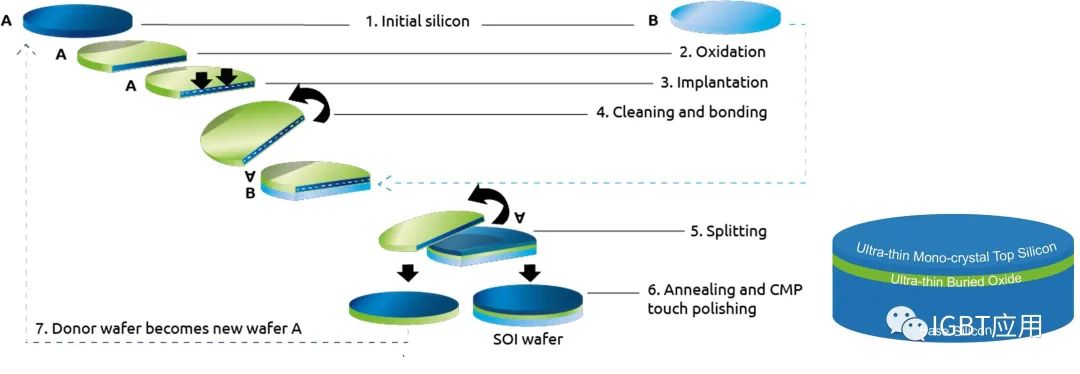

如下图所示。该工艺最初在1997年提出,从两个传统的 Si 衬底开始,一个是基础(handle)衬底,第二个是供体(donor)衬底,它将薄器件层附在最终的 SOI 堆上。首先,供体衬底被氧化,在其表面形成掩埋氧化物。然后,氢被注入到供体衬底的同一表面,氢原子停留在氧化物下方的浅距离处,相当于器件层的厚度。然后清洁并翻转供体晶片,使其氧化和氢注入的表面可以与基础衬底接触。室温亲水晶圆键合工艺暂时融合两个晶圆,然后退火导致注入的氢膨胀,分裂供体衬底,从而使器件层和掩埋氧化物保留在基础衬底上。经过高温退火以实现永久键合后,CMP 抛光完成 SOI 晶圆。剩余的供体晶圆的其余部分可以在其表面通过 CMP 抛光平滑后重新用于下一个 SOI 晶圆。

Soitec 转向碳化硅

在生产 SOI 衬底二十多年后,Soitec于 2019 年宣布,他们将把 Smart Cut 工艺应用于 SiC,生产“工程衬底”,以解决“与碳化硅衬底的供应、产量和成本相关的挑战” 。Soitec 的 SmartSiC 工艺细节于 2021 年公布,而 2022 年Soitec 和意法半导体宣布他们正在“合作”,意法半导体将在宣布后的 18 个月内对晶圆进行认证。

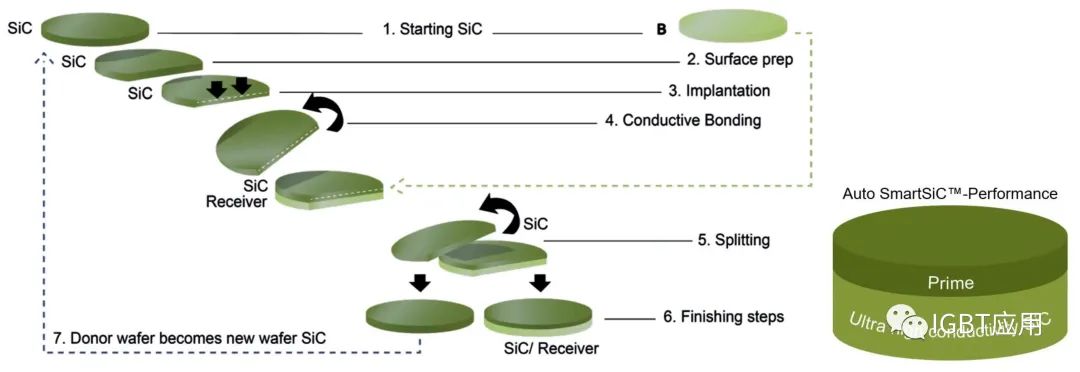

Soitec 展示的是他们的 SmartSiC 衬底。总之,这些由一薄层单晶 SiC 永久粘合到(相对)低成本、高掺杂、多晶 SiC 处理衬底(可能由Mersen提供)组成。SmartSiC 衬底制造过程如下图所示。Soitec 重复使用了他们的 SOI 示意图,用硅晶圆代替了单晶 SiC 供体晶圆和多晶 SiC 处理晶圆。这有助于与 Smart Cut(TM) 工艺进行比较:单晶 SiC 晶圆被注入轻元素(可能是氢),然后进行清洁、翻转并粘合到处理晶圆上。两次退火,第一次在较低温度下使供体晶圆破裂,第二次在较高温度下使键合永久,从而留下 SmartSiC 衬底和大部分 SiC 衬底可以抛光和重复使用。

在回答我们的问题时,Soitec 确认单 SiC 的碳面与处理晶圆键合,确保 SmartSiC 表面是单 SiC Si 面 - 与传统 SiC 衬底相同。粘合到多晶碳化硅表面的单晶碳化硅层(我们假设其厚度约为 1μm)应该是适合在其表面上生长传统外延层的种子层,然后进行器件制造。

SmartSiC 衬底的潜在优势

采用SmartSiC工艺最显著的优势之一是可以重复使用单个单SiC晶圆,根据Soitec的说法,重复使用率至少为10倍,这有助于解决目前行业普遍面临的SiC材料供应问题。然而,Soitec 似乎热衷于传达这样的信息:这并不一定意味着他们的晶圆会因此变得便宜。

相反,Soitec 认为他们拥有优质产品,基于 SmartSiC 衬底的优势,可以最大限度地减少与衬底相关的电阻。他们声称对衬底的影响将对降低总器件电阻 (Rds,on) 产生重大影响,从而允许生产在给定电阻率下更小的芯片。正如我们之前所讨论的,更小的芯片意味着每个晶圆上可以生产更多的产品,并且产量略有提高,从而降低单个芯片的成本并提高晶圆厂的产能。

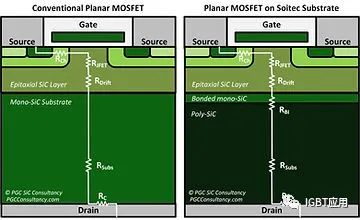

为了了解潜在的衬底电阻改进,值得回顾一下它在 SiC 功率器件中的作用,例如下图中的平面 MOSFET。功率器件垂直排列,高压漏极端子位于衬底的背面。这种布置使器件的电流密度最大化,但它需要电子向下穿过薄漂移区,然后在到达漏极之前穿过衬底。

因此,衬底是芯片成本的最大贡献者并且具有相当大的电阻,在器件中几乎不发挥积极作用。在前端制造过程中,350 µm 衬底为 5-10 µm 外延器件层提供机械支撑。然而,在此之后,在沉积漏极金属接触之前,它会被减薄至 100-180μm(取决于制造商和代次),从而最大限度地减少衬底电阻的影响。在 750V MOSFET 中,漂移区厚度仅为 6-8 µm,衬底将贡献高达器件总电阻的 17%。

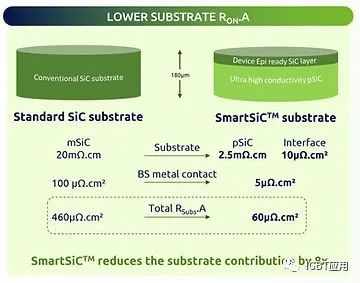

当传统的单晶 SiC 衬底通过晶种升华生长时,晶体质量(低缺陷密度)和掺杂密度(低电阻率)之间存在基本的权衡。由于衬底是后续外延生长的基础,因此衬底的质量不能受到影响,因此其电阻相对较高(通常为15-25 mOhm-cm)。衬底的有限掺杂密度还增加了衬底和漏极之间的小接触电阻(Rc)。相反,在生产多晶碳化硅衬底时,其缺陷密度并不重要,因此可以将其掺杂密度推至极限,从而最大限度地降低其电阻。

此前,Soitec 一直不愿透露太多有关其晶圆规格的信息,在营销中仅提及其电阻率的最大值。然而,最近在布鲁塞尔举行的 CS International 2023 上,Soitec 首次展示了其衬底的“典型”值,如下图所示。据此,典型的多晶碳化硅电阻率为 2.5 mOhm-cm,具有键合界面在电阻率上增加 10 µOhm-cm2。他们还表示,高掺杂几乎消除了接触电阻,将其从 50-100 µOhm-cm2 降低至 5 µOhm-cm2。

Soitec 声称的降低背面接触电阻率的值源自 2022 年向 ICSCRM 的演示。他们发现,未经激光退火的SmartSiC 衬底的接触电阻率比经过激光退火的标准单晶硅衬底的相同接触电阻率低 10 倍。因此,他们建议可以取消激光退火阶段,从而消除一项后端制造成本。

最后,在回答我的问题时,Soitec 声称他们能够实现更 flatter substrate,并分享与单 SiC 相比较低 SFQR 值的数据。虽然这将有助于加工,可能提高产量,但其好处对于本文的模型来说是无法量化的。

分析 SmartSiC 衬底的成本效益

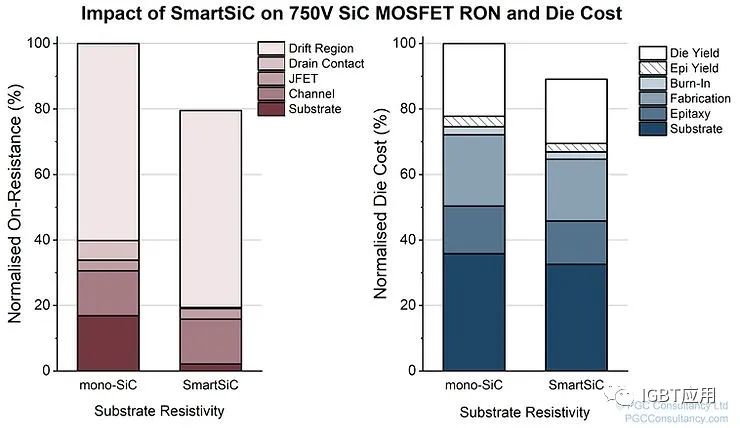

PGC Consultancy 和 Exawatt 共同创建的技术经济模型将器件技术和供应链的改进转化为成品芯片的成本。该成本涵盖了衬底、外延和制造成本,并考虑了与缺陷密度(外延良率)和器件制造(芯片良率)相关的良率。在本节中,我们将建模应用于 Smart Cut(TM) 晶圆,以评估其潜在优势。该模型使用一流的商用 15 mOhm 750V 沟槽 SiC MOSFET 作为基准,该 MOSFET 在厚度减薄至 140 µm 的传统单 SiC 衬底上形成。根据这一基准,我们使用 Soitec 的典型衬底和接触电阻率值,对在 SmartSiC 衬底上实现的相同器件进行建模,如下图所示。

结果,使用 Soitec 的“典型”电阻率值,我们的 750V 沟槽 SiC MOSFET 的总器件电阻 x 面积 (Ron.A) 降低了 20%。考虑到缩小芯片尺寸时的热效应,这意味着芯片尺寸缩小了 9.1%。较小的芯片增加了每个晶圆的芯片数量,并提高了成品率。再加上无需激光退火的制造工艺,意味着成品芯片成本降低了 10.9%。

如果 Soitec 的典型电阻率值得到验证,那么这些电阻率的降低确实会令人印象深刻。考虑到罗姆的第 4 代MOSFET 的 Ron.A 比第 3 代低约 40%,20% 的降低类似于未来 Ron.A 在单代飞跃中的降低。此外,这假设有关设备的所有内容都保持不变。例如,如果封装要逐代改进,那么更有效的散热可以进一步缩小芯片尺寸。

较小芯片的影响对 IDM 的利润率产生复合影响。新一代更小的芯片在每个晶圆上生产更多的器件,每个器件的生产成本都比上一代更低。如果芯片销售价格保持固定,且IDM 不将任何成本节省让利给客户,那么他们的利润率将大幅增加,在上述 750V MOSFET 的情况下将增加 29%。在供应受限的市场中,IDM 或许能够攫取所有利润率;然而,随着时间的推移,随着竞争的加剧和市场对价格变得更加敏感,这将允许维持之前的利润,从而将成本降低让利给客户。

当对 1200V MOSFET 应用相同的分析时,由于支持更高电压所需的更厚、更低掺杂的漂移区,衬底电阻的影响被削弱。因此,SmartSiC 衬底使器件的 Ron.A 降低了 14.2%,相当于芯片成本降低了 8.4%。假设成本节省没有让利给客户,则增加的利润为 21%。

Soitec商业模式:衬底供应商还是设备供应商?

本文中的建模假设 Soitec 充当客户的材料供应商,与 Wolfspeed、Coherent 或 SICC 相同。它还假设衬底的成本不超过 SiC 衬底的平均价格。然而,考虑到客户在较低电阻上实施其设备所带来的潜在成本效益,Soitec 似乎准备为其衬底贴上比竞争对手更高的价格标签。在考虑额外的转移成本之前,多晶碳化硅衬底相对于单晶碳化硅衬底到底有多便宜,这一问题在一定程度上强化了这一点。因此,在向公开市场发布时,其相对于现有产品的确切定价将值得关注。

然而,Soitec 热衷于提出一种替代模式,即他们可以充当技术许可公司,向客户提供 SmartSiC 工艺作为其晶圆厂的工具箱。这个想法是,这可能会导致垂直整合的 IDM 至少减少安装90%的 SiC 晶体生长炉,转为安装可以重复使用其单 SiC 衬底的 SmartSiC 系统,并具有前面提到的低电阻特性的额外优势。为了实现这一点,人们不仅需要考虑 Soitec 晶圆的技术优点,还需要考虑财务权衡。

安装 Soitec 系统的成本(即资本支出成本)需要低于安装它们将取代的晶体生长炉的成本。由此可见,运行 SmartSiC 系统的 OPEX 成本,需要低于被替代方案。根据我们利用现有的少量公开信息进行的计算,如果 10 倍重复利用乘数成立,则 150mm 衬底的成本案例似乎是可行的。

Soitec 自己表示,如果实施这一举措,衬底供应将节省资本支出和运营支出。

良率、可靠性鉴定和晶圆厂集成

前面几节中的分析列出了与 Wolfspeed、Coherent、SICC 等公司的传统 SiC 衬底相比,如果其他条件相同,使用低电阻 SmartSiC 衬底可以节省潜在的成本。这一警示很重要,因为复杂的制造工艺详细提出了许多问题,需要在其成为 SiC 供应链中广泛采用的衬底之前得到答案。

缺陷密度

第一个问题与 SmartSiC 处理步骤之后单晶 SiC 层内的缺陷密度有关。缺陷的任何增加都会对良率产生负面影响,从而减少前面概述的好处。在PGC,我们确信氢注入、键合、分裂、高温退火和抛光等复杂工艺对衬底不利;然而,这些都是相当标准的制造技术,不太可能产生缺陷(例如与外延生长不同)。

Soitec 的回应是向 ICSCRM 引用了他们自己的2021 年会议论文。在本文中,对供体和 SmartSiC 衬底对进行 KOH 蚀刻后拍摄的图像揭示了匹配的缺陷密度。尽管本文分析的总面积仅为 1 × 1 mm,但这是一个很好的分析。随着时间的推移,将该技术扩展到整个晶圆,或者更好地使用高分辨率X 射线衍射成像 (XRDI) 技术来生成智能切割层的完整 3D 缺陷图,将有助于证明整个晶圆上的缺陷密度。

可靠性

在包含键合界面的衬底上形成功率器件会带来一个经常被问到的问题:面对电动汽车使用寿命的热循环,这种键合是否可靠?Soitec 再次想方设法解决这个问题,聘请埃尔兰根的 Fraunhofer IISB 来执行功率循环测试。在 PCIM 2022 上发表,埃尔兰根的团队对许多肖特基二极管进行了测试,让足够大的电流通过它们,在 3 秒内将温度提高 120K,然后在接下来的 9 秒内让它们降温下来。

然后,他们继续重复此过程 565,000 次(相当于 79 天)监测二极管的温度变化以揭示其热阻衰退。在此期间,SmartSiC 或单 SiC 的二极管都没有出现故障。随着时间的推移,所有器件中的银烧结接点都会退化,导致热阻升高,但平均而言,SmartSiC器件的热阻上升幅度较低。这是一项非常专业且独立的研究,对 SmartSiC 键合接口的可靠性毫无疑问。随着时间的推移,对另一个标准可靠性指标(短路耐受时间)的基准比较将进一步验证这项研究。

不透明基材与透明基材

传统 SiC 衬底和 SmartSiC 衬底之间的区别在于它们的颜色和透明度。氮掺杂单晶碳化硅 4H-SiC 的独特之处在于几乎透明,据我所知其颜色接近橄榄石。明显的区别在于,多晶碳化硅是黑色且不透明的,如图 6 所示。当被问及这种变化对光刻等制造设备的影响时,Soitec 淡化了对单晶硅衬底的光学传感器的影响。对此问题,评论称他们将与客户合作做出所需的调整。对我们来说,很明显,专门针对一种晶圆类型或另一种晶圆类型的生产线设置不会有任何问题,之间的切换需要调整或重新校准。

单个SiC 衬底可重复使用 10 倍

SmartSiC 的任何价值案例背后的问题都是 10 次重复使用次数。在回答有关 10 倍数字稳健性的问题时,Soitec 表示,这是“基于对 1500 多个 SmartCut SiC 衬底的分析,并利用了每年超过 200 万个 SmartCut 硅晶圆的积累知识”。

我们仍然清楚,如果要在 IDM 内就地推出 SmartSiC 系统,则需要明确该产量是可实现转产的。

结论

SiC衬底是SiC功率器件发展中不可避免的难题。作为上述外延层的种子层,它对最终产品增加了显着的影响力,而这只能通过芯片缩放来克服。因此,传统的 SiC 衬底被减薄到制造后可处理的极限。

SmartSiC 仅使用微米薄的单 SiC 层粘合到超低电阻多晶 SiC 衬底上。PGC Consultancy 仅根据 Soitec 公开宣称的衬底值计算出,SmartSiC 衬底可将 750V MOSFET 的总电阻降低 20%,从而使每个 750V 额定 MOSFET 芯片节省 10.9% 的成本。假设客户的芯片价格不变,将节省成本与提高产量相结合,可计算出利润增加了 29%。

SmartSiC 概念的第二个好处是它有可能疏通堵塞的 SiC 供应链,一种单 SiC衬底可用于开发 10 个 SmartSiC 衬底。早些时候,许多评论家认为这意味着 Soitec 可能会寻求降低其他产品的价格。然而,现在很明显,由于它们的电阻率超低,这些实际上将是优质晶圆。Soitec 不仅仅是为晶圆供应商打开了大门,其进一步的想法是将其工艺直接安装到 IDM 中,通过将所需熔炉容量减少多达90%来节省资本支出和运营支出。

Soitec 还对常见问题做出了解答,利用 SiC 会议来证明其衬底的电阻率、低缺陷率和可靠性。最值得注意的是,他们与弗劳恩霍夫(Fraunhofer)合作证明,当受到类温度循环应力时,粘合界面是可靠的。在缺陷方面,他们在微米尺度上表明,它们没有在转移到 SmartSiC 的层中添加新的缺陷,但是未来将其扩展到整个晶圆的工作将为宏观趋势提供确定性。对这这种衬底进行独立验证的有效结果将消除有关这些问题的任何剩余技术疑虑。

审核编辑:刘清

-

电动汽车

+关注

关注

156文章

12110浏览量

231522 -

MOSFET

+关注

关注

147文章

7192浏览量

213557 -

逆变器

+关注

关注

285文章

4729浏览量

207072 -

SiC

+关注

关注

29文章

2835浏览量

62708 -

碳化硅

+关注

关注

25文章

2778浏览量

49109

原文标题:资讯 | 深入了解 Soitec 的 SmartSiC技术

文章出处:【微信号:芯长征科技,微信公众号:芯长征科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Soitec 发布首款 200mm SmartSiC™ 优化衬底,拓展碳化硅产品组合

专家开讲:深入了解电池技术 ──Part 1

专家开讲:深入了解电池技术 ──Part 2-1

专家开讲:深入了解电池技术──Part 3

专家开讲:深入了解电池技术──Part 4 (碱性电池)

专家开讲:深入了解电池技术──Part 5 (碳锌电池)

专家开讲:深入了解电池技术──Part 6 (锌空气电池)

专家开讲:深入了解电池技术──Part 7 (锂亚硫酸氯电池)

助推电动汽车发展的新动力:Soitec 的 SmartSiC™

助推电动汽车发展的新动力:Soitec 的 SmartSiC™

深入了解Soitec的SmartSiC技术

深入了解Soitec的SmartSiC技术

评论