01**

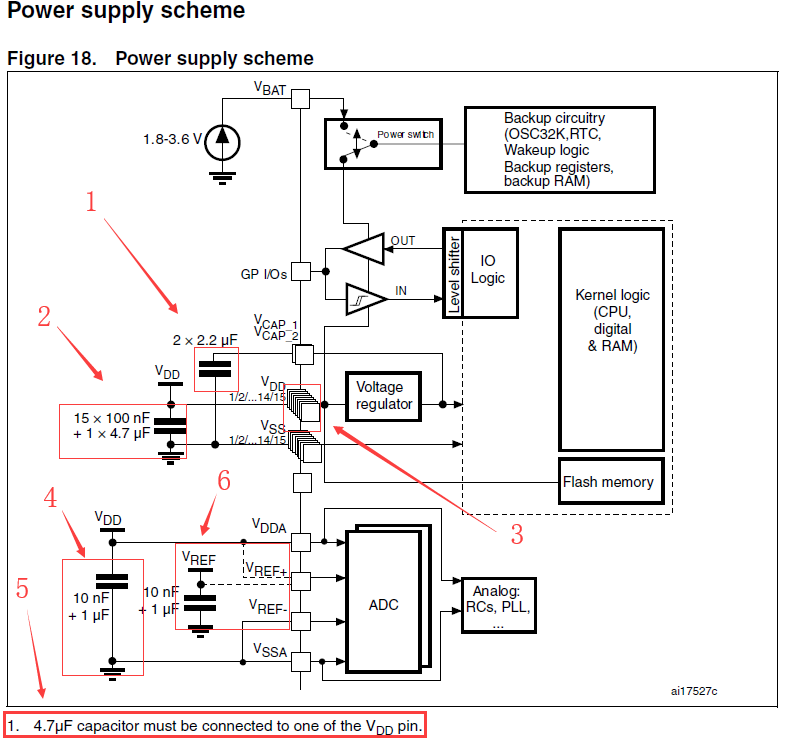

下图来自STM32F207的datasheet。

①表示Vcap1和Vcap2接了2.2uf的电容接地,每个接1个电容;

②表示VDD1到VDD15接上VDD电源,再接电容,接地。Vss接地。PCB布局,尽量把电容离管脚近;

③表示可能有15个VDD,同理Vcap1和Vcap2只有两个方块,说明有两个电源引脚;

④表示VDDA连接VDDA,VDDA和VSSA,那么就是他们给ADC等模块供电,没有的话,就是VDD和VSS供电。其中Vref+和Vref-是ADC模块基准电压,可以直接连VDDA和VSSA;

⑤必须其中有一个VDD连接上4.7uf电容,(注意:STM32F10系列必须是VDD_3连接4.7uf电容);

⑥表示Vref+可以连接其他的基准电压,但是要连接10nf电容+1uf电容,其实就是并联。

注释:

- 10nf+1uf 就是并联电容

- 100nf = 104 10nf = 103 1uf=105

02**

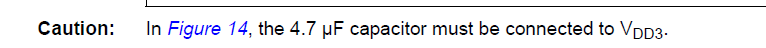

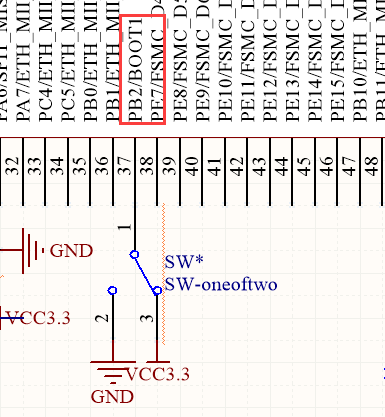

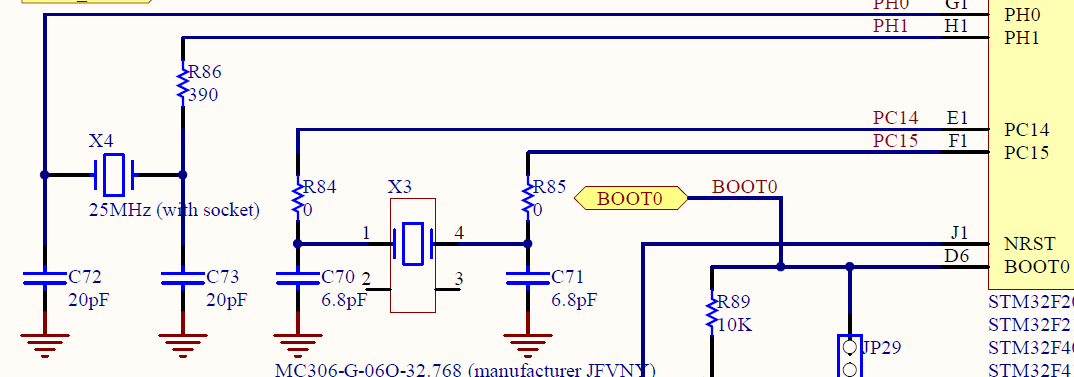

boot

下图见:STM32F207用户参考手册,编号RM0033

boot0可以不下拉电阻的,片内有下拉电阻,实际项目中,还是需要下拉电阻,保证在复杂电磁环境下从Flash启动;

采用跳电阻的形式选择,实际项目,只需要BOOT0就好,学习的板子,两个都设计吧。

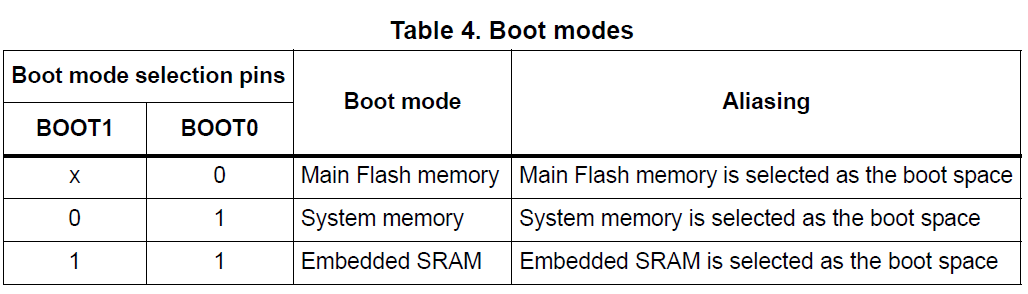

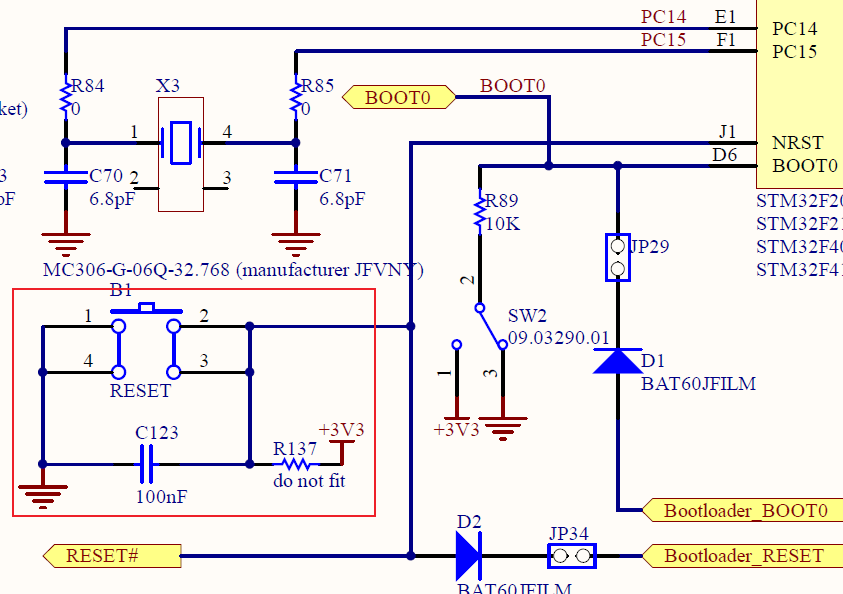

STM32F207官方评估板电路:

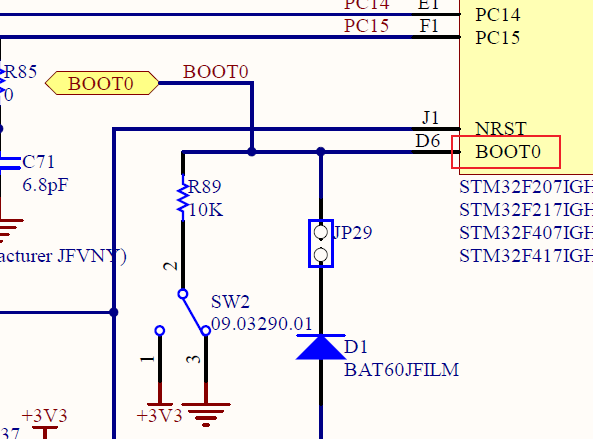

03**

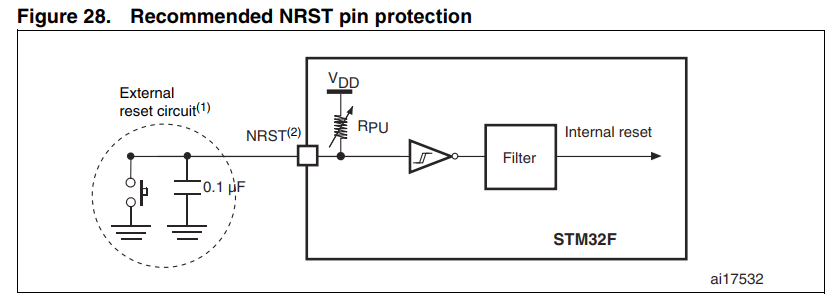

复位电路

下图见datasheet

上图看出,官方建议下拉0.1uF电容,再接复位按键,当管脚是低电平的时候复位,官方评估板电路采用电阻降压,注释donot fit,

04**

晶振

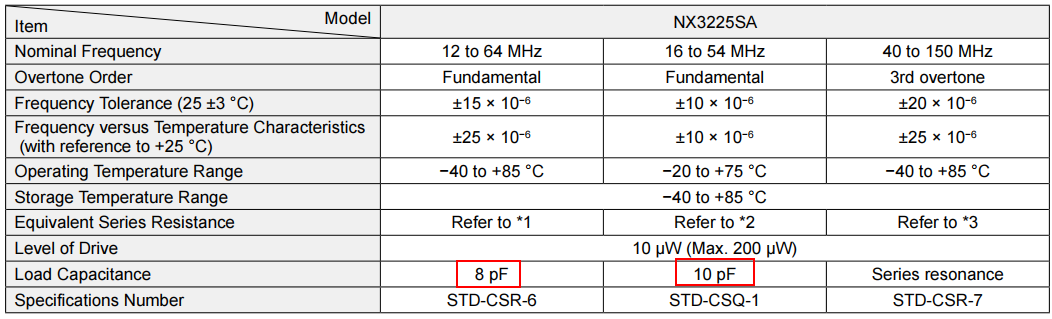

采用3225封装的无源贴片晶振。

晶振资料

Load Capacitance:负载电容

个人一般配18PF电容

下图是ST的评估板原理图

其中,低速时钟为了片内RTC

05**

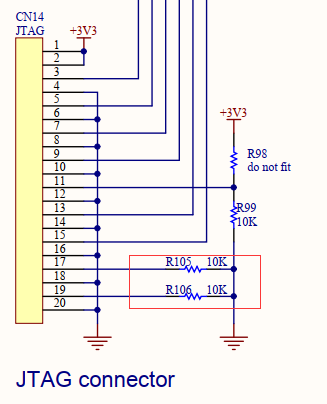

JTAG

根据ST的评估板,JTAG有上下拉电阻,实际应用中,使用SWD接口,只需要VCC,TMS,TCK,GND四根信号线,没有上下电阻也没有影响。

06**

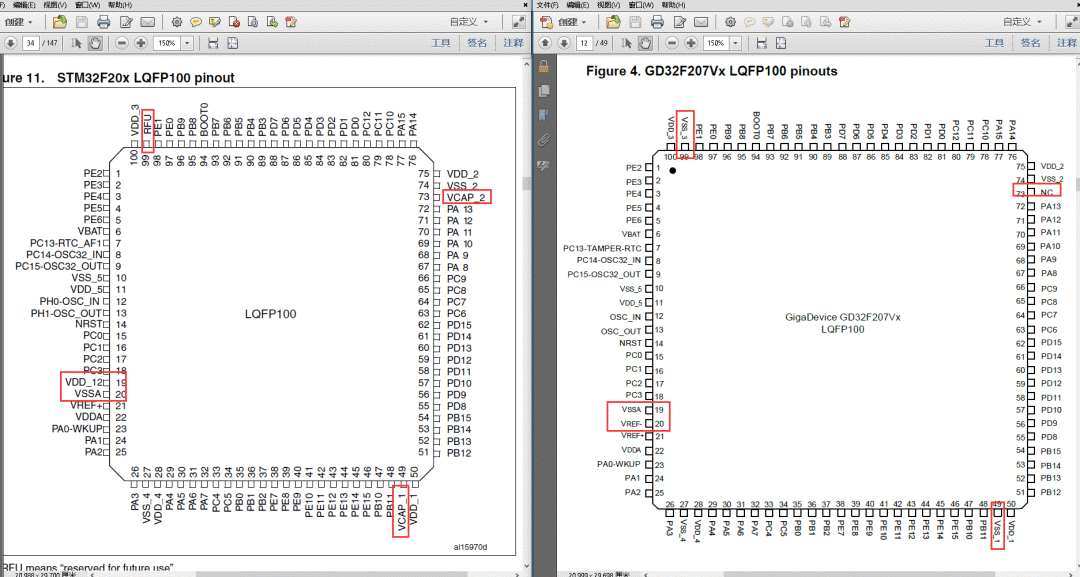

兼容设计

1、复位采用max809

2、无论是否使用模拟部分和AD部分,MCU外围出去VCC和GND,VDDA、VSSA、Vref(如果封装有该引脚)都必需要连接,不可悬空

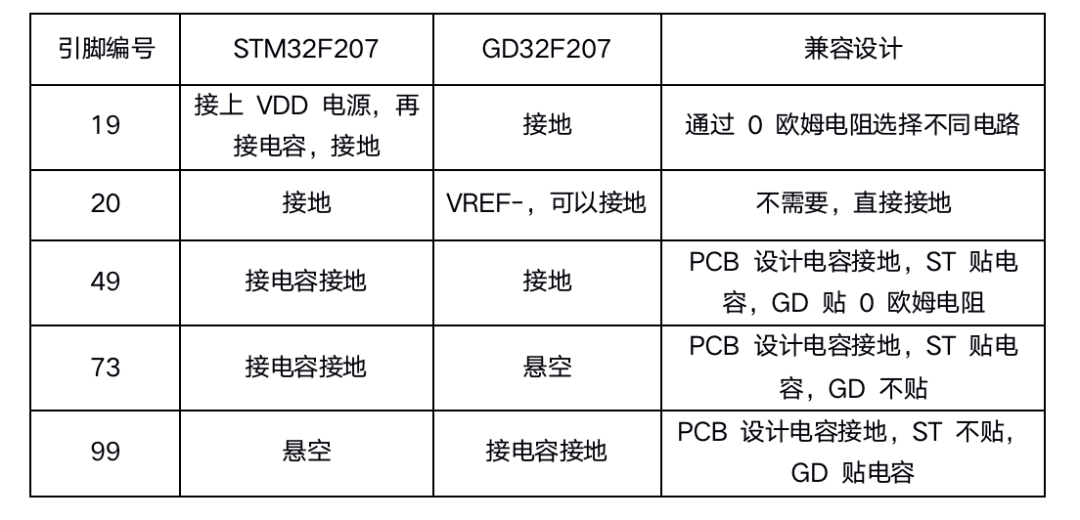

3、兼容GD207和ST207,原理图上做一下图示四种处理

差异区别:

07**

外设资源

设计兼容STM32F207和GD32F207的开发板,其他外设资源电路直接参看原理图。

板载资源有:

- USB串口

- 网口(RTL8201)

- 两颗LED

- RTC

- NorFlash

- 电源(5V转3.3V)

- TF卡

- 触摸按键

- 4个独立按键

- 8位并口LCD

- USB

- ESP8266的WIFI模块

- ESP8266的USB下载口

设计缺陷

- 四个角忘记放置定位孔

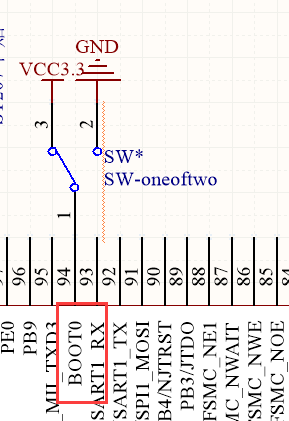

- BOOT0和BOOT1的丝印错写为GND

- 很水的原理图和layout

- 没有纽扣电池供电给RTC

-

下拉电阻

+关注

关注

4文章

147浏览量

20488 -

VDD

+关注

关注

1文章

311浏览量

33078 -

STM32F207

+关注

关注

0文章

9浏览量

6555 -

负载电容

+关注

关注

0文章

137浏览量

10424 -

GD32F207

+关注

关注

0文章

21浏览量

3956

发布评论请先 登录

相关推荐

怎么设计一款兼容STM32F207和GD32F207的开发板?

怎么设计一款兼容STM32F207和GD32F207的开发板?

评论