1.0 概述

本文所用测例RFIC是一款自研射频收发器芯片,工作于全球通用的ISM 2.400~2.525GHz频段,126通道,集成了频率综合器,功率放大器,调制和解调模块,还支持完整的数字链路层协议引擎,是真正单芯片的无线数据收发器。信道速率最高1Mbps,支持HOSTCPU下载更新内部微码,实现链路层的灵活控制;最大工作电流20mA;发射功率控制范围达33dBm,控制步长2dBm。芯片采用0.18µm RF CMOS 工艺,其中数字逻辑约2.5万门。

为了获取准确的功耗数据,采用了HSIM-VCS进行多模块数模混合仿真。由于芯片划分为模拟设计AFE和数字设计DLP两大模块,它们之间依靠大量的状态控制信号和数据信号互联,首先采用了HSIM-VCS进行全芯片数模混合功能仿真。为了获得更快的Turn Around Time (TAT), 后引入XA-VCS进行全芯片功能仿真加速。

2.0 数模混合仿真

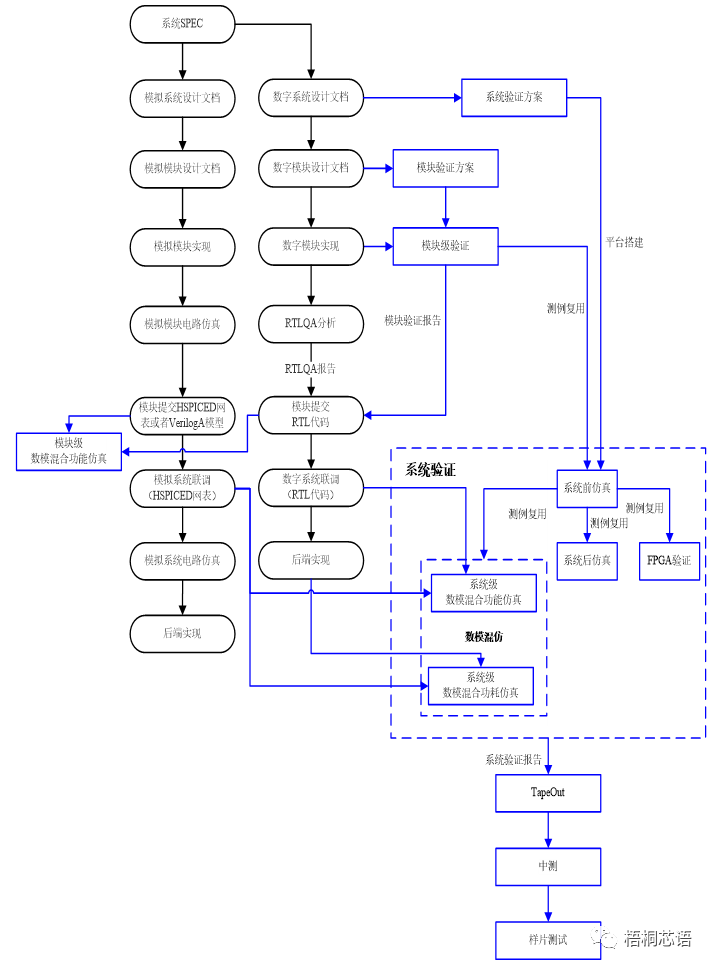

数模混合仿真的验证对象是数模混合集成电路。数模混合集成电路的设计流程是比较复杂的。如图1所示,该RFIC芯片不仅包括了单独的数字和模拟设计流程(分别用于实现数字和模拟的功能模块),在将数模电路混合时,也有其独立的设计流程去验证数模接口信号的正确性、数模混合后能否继续正常工作,以及进行数模混合电路的物理设计等。

数模混合电路是对数字电路部分和模拟电路部分分别进行不同抽象层次的仿真、集成之后进行数模混合仿真。为了尽早发现设计Bug,有功能交互的模拟模块和数字模块在分别独立验证完毕之后,进行模块级整合,分别提取Hspice网表和RTL代码,进行混数模合仿真。

电路仿真的速度和精度是经典的trade-off,同时取决于仿真环境中使用的仿真器(软件)和工作站环境(硬件)。为了加速仿真,本项目采用了“超级”Linux工作站:64G内存,584G硬盘,16核2.40GHz/6MB CPU。关于仿真器,将在后续两章做较为详细的介绍。

3.0 功耗仿真

数字逻辑电路的功耗分析手段较多。其中Synopsys公司的工具PrimeTime PX,可以通过已有的Liberty格式功耗模型,计算一段时间内电路翻转发生的总能量,进一步得出该时间段内的平均功耗,但该方法对于分析电流瞬态变化以及上电过程中的动态电流变化有很大的限制。虽然利用HSPICE等高精度Spice仿真器进行仿真可以得到最精确的结果,但对于数字逻辑这种“巨大”规模(百万门级)的电路来说,几乎根本无法进行。

Synopsys公司的HSIM工具,是一款广泛采用的Fast Spice仿真工具,利用该工具可以对大规模的电路做Spice级电路仿真,在精度和速度接受的情况下取得比较接近于实际的动态电流曲线,同时可以仿真出芯片在上电(Power Up)过程中,电源上电顺序对数字电路功能以及电流的影响。通过VPI或DKI接口将HSIM和VCS连接起来,更可以直接使用在数字验证中所使用的激励(TestBench)形成对HSIM Spice仿真的输入激励,实现数字激励和SPICE级设计的动态数模混合仿真。我们采用了VPI的HSIM-VCS数模混合验证方法。

图1项目设计流程图

3.1 目标

对于该RFIC芯片,使用HSIM-VCS进行数模混合仿真,主要是有以下分析目标:

Ø在上电过程中(从外部电源上电到数字电路上电复位信号释放的过程)电流峰值是否满足设计要求(小于10mA)

Ø当数字电路的上电复位信号释放时,系统工作电压是否能保证数字逻辑处于正常工作状态

Ø数字电路工作时,工作电压是否能够保证其正常的工作

3.2 环境

3.2.1 EDA工具以及工作站环境

Spice仿真器: HSIM 2008.03 64bit

Verilog仿真器: VCS 2006.06-SP2 64bit

服务器型号: IBM3850M2Server

系统平台: Linux RHEL v4 64bit

需要注意的是,利用VPI作为接口进行HSIM-VCS的仿真,HSIM和VCS的版本必须一一对应。

3.2.2 Spice级数字电路网表的准备

数字电路网表来自于自动布局布线工具输出的Verilog格式网表,但该网表是不能够直接用于Spice级仿真的,因此需要将网表转换成可以用Spice仿真工具进行仿真的格式。

Verilog转换成CDL

一般说来,需要将Verilog格式的网表转换成Spice仿真工具可以识别的CDL网表,HSIM自带的v2s工具,可以用来完成这个工作。下面描述的是一个将Verilog格式网表abc.cdl转换成abc.cdl的脚本,直接运行就可以完成转换:

上面的脚本里,“-bn0”表示如果是Bus信号,则使用方括号[]来描述分离的信号名,如A[0]、A[1]等。“-const 00”表示电路中常数0表示0V,同理“-const11.8”表示常数1为1.8V。“-global_const0”以及“-global_const1”指定了全局变量中电源和地的网络名,这会使产生的CDL网表中加上“.global vdd vss”命令。“-o”指定输出的CDL文件。

“-s”指定了电路中某些IP的spice级网表文件,转换工具会根据IP网表中端口的顺序进行转换。但需要注意,Bus信号顺序则不会根据网表内的顺序进行转换,而是根据Verilog格式中定义的顺序进行转换。如下所示,某个IP在Verilog格式网表中的例化方式中,busd是由高到低的:

那么产生的CDL网表中,例化的顺序就是由高到低。

XInstanceName netc neta netb bus[2] bus[1] bus[0] ReferenceName

而这与IP的Spice级网表定义的顺序不一定一致。这种情况往往发生在RAM、ROM等Bus信号较多的模块上,因此在转换完成后,建议对于IP的接口进行进一步的检查以及修正,特别是存储单元的接口。

一般说来,标准单元库的电路模型,电源是不会连接出来的,但名称都保持一致,如VDD、VSS等,只需要在Spice仿真时,设置成全局变量,就可以将他们连接在一起了。

3.2.3 添加绑定模型

集成电路的电源通常会绑定出来,由外部供电,而绑定时就会在电源连接线上产生寄生电感、电阻以及电容,如图2所示:

图 2绑定模型

图2中PadInside指芯片内的连接信号,PadOutSide指通过绑定到芯片外面后的接触点。由于这些寄生电感、电容、电阻,会使电源信号发生一定的抖动,在电源信号以及地上添加模型进行仿真,可以更加真实的反映电路的运行状态。

3.2.4 Spice网表总体框图

图3所示为Spice网表总体的框图:

图 3 Spice网表总体框图

如图所示,VDD是外部供电电源,工作范围在2.7V~3.6V,Voltage_Regulator(VR)用于产生提供给数字电路供电的电源,电压在1.8V左右。

CguAfeREF_ENB信号由数字逻辑送给VR,对其进行控制,如果该信号为数字高电平DVDD,则VR处于正常工作模式下,可以提供足够的电量给整个数字电路。当该信号为VSS时,VR工作在低功耗模式,只能提供较小的电量给数字电路。这里DCP是Digital Control Part的简称,也是整个数字逻辑电路所在,文中主要以Dlp作为其top名。powerstart信号是VR输出给Dlp的上电复位信号,为低电平时,数字逻辑电路处于复位状态,为高电平时,数字逻辑电路复位状态释放。

SPI BUS和CE信号是由Verilog格式描述的激励。

3.2.5 数模接口描述

Spice仿真的激励都是从Verilog激励输入进来的,数模接口如图4所示:

图 4 数模接口信号示意图

数模接口的信号电平等信息可以在一个配置文件cosim.cfg中描述:

这里PadMiso是SPI接口的信号线之一,由模拟电路top.cdl输出给Verilog格式仿真测例SimTop.v做逻辑判断,当电压超过2.6V后,仿真测例认为是逻辑1,当电压低于0.5V时,仿真测例认为是逻辑0。这样的信号称为a2d(analog to digital)信号。

PadSpiClk, PadCsn, PadCE以及PadMosi是SimTop.v输出给top.cdl的数字转模拟的信号,称为d2a(digital to analog)信号。当输出为逻辑1时,top.cdl接收到3.3V,而输出为逻辑0时,top.cdl接收到0V。

因此只需要编写一个配置文件,就可以将数模接口信号连接起来,使HSIM和VCS进行数模联合仿真了。

3.2.6 仿真环境的配置

启动HSIM-VCS的仿真非常容易,只需要编写一个执行文件脚本(如run_vcs)就可以直接运行了,整个运行的文件调用流程如图5所示:

图5 HSIM-VCS仿真脚本调用示意图

在“run_vcs”中调用了2个文件,“cosim.cfg”以及“FileList.v”。“FileList.v”是一个将所有verilog格式文件包含进来的文件,其中包括了仿真激励文件“SimTop.v”,以及只包含输入输出信息的顶层黑盒子申明文件“top.v”。“top.v”主要是提供VPI一个接口信息。“cosim.cfg”是HSIM-VCS数模混合仿真的配置文件。“set_args”申明了Spice仿真环境的顶层文件,叫做“test.spi”。“analog_cell”指定了Spice仿真的顶层模块名,即top,VPI会在top的Verilog黑盒子文件“top.v”中找到所有a2d和d2a的信号,并根据“cosim.cfg”中的设置进行数模信号连接。“cosim.cfg”包含的“test.spi”是Spice仿真环境的顶层,在该文件里会做HSIM相关的配置信息。

首先,HSPICE网表第一行是用来写注释的,工具不读取:

|* test.spi

HSIM的变量定义,可以是全局变量(.param),也可以是针对某个Sub-circuit的局部变量(.hsimparam subckt=xxx),如:

HSIM的 “.force”命令可以强制在某个时刻,将某个net强制设置成某一个固定的电平。

如有需要,可以为电路中所有的节点赋初值(DC Initial)。仿真到某个时刻,可以将该时刻所有节点的电压(Operating Point)记录下来,如:

.op 100u

上述命令会在100us的时候记录下所有节点的电压,并以“.ic v(…)=”的格式记录下来,输出文件名为hsim_.ic,如果下次仿真希望从这个时刻开始,则可以用“.inc hsim_.ic”命令使所有节点的值按照上次输出的电压值进行初始化,然后仿真。

3.3 仿真结果

根据3.1的仿真目标,进行了3个不同的仿真激励。

第一个是100ns外部电源上电,这样的上电过程速度很快,而VR为了达到预期的输出,会对负载进行充电,设计时对充电电流进行了限流,不希望超过10mA。这里需要注意的是,Spice仿真需要一个初始值,而电路的初始值不同,其表现也可能不同,因此在该仿真过程中,将初始节点电压都设为0V,所有电容初始状态都没有电荷,充电过程应该是一个最恶劣的情况,如果在该情况下都没有超过10mA的电流,则认为VR设计正确。

第二个是5ms慢速上电,VR输入电压不高,但却要给负载充电,则电流很小,如果100ns时都满足要求,则此处可以不用考虑电流问题,但由于充电电流相当缓慢,因此该仿真的目的在于powerreset释放时数字电路能够正常工作。

第三个是正常功能仿真,VR能够满足数字逻辑的工作需求。

3.3.1 100ns电源上电

100ns电源上电仿真波形如图6所示:

图 6 100ns电源上电仿真结果

图中I(rvdd1)是外部电源给VDD电源网络供电的电流,也就是整个芯片的电流需求。I(cdvddload)是数字系统电源外部33nf滤波电容上的电流。I(sunyq)是给数字电源系统DVDD供电的电流。从图中可以看出,powerreset释放时,DVDD已经达到1.75V,数字电路可以正常复位。同时VDD上电速度很快,但整个芯片的电流需求不大,I(rvdd1)在上电过程中比较平缓,只有在刚上电时有一点波动,因此放大一些来看:

图 7 100ns上电初期波形图

从图中可以看出, I(rvdd1)在上电初期有一个对电流需求很大的时间,是为了对33nf电容充电而产生的,但最大不超过6mA。VR满足了我们的需求。

3.3.2 5ms电源上电

下图所示是5ms电源上电的波形图:

图8 5ms电源上电波形图

由上图可知,I(rvdd1)在上电过程中非常平缓,没有超过10mA,但powerreset释放时,数字电路的供电只有1.25V左右。由于电路设计的特殊性,电路复位释放后并不会立刻工作,而是要等很久(超过百ms级)才会开始工作,而从图上看出DVDD电压仍然在上升,且1.25V,已经可以保证电路正确复位。因此这里认为,VR设计满足要求。

3.3.3 正常功能仿真

图9所示是正常功能仿真的波形图:

图9正常功能仿真波形图

从整个仿真过程看,VDD在2us时间上电,DVDD也在50us左右达到较高电压(约1.6V)。powerstart在约55us时释放,SPI在约110us时置起spicgupwrup使Dlp从PowerDown模式进入了StandBy模式,然后在StandBy模式下,SPI置起bootload信号,进入DataLoad模式并下载程序,接着退回StandBy模式。拉高CE后,系统进入发送模式,发送数据,发送进行过程中,CPU写apreg启动低功耗的AP模式,经过约100us后,SPI强制退出AP模式回到发送模式。

整个过程看来都比较正常,电流I(rvdd1)在发送模式时最大,有2mA左右(图中没有)。

可以看出整个设计满足功能需求。

3.3.4 测试结果

样片测试时,负载电容为100nF,是仿真时(33nF)的3倍,上电时间选择了9.7us,获得最大电流尖峰为8.24mA,上电充电时间约10us,DVDD达到约1.0V,如下图所示:

图10 样片测试上电波形图

用实测结果与100ns上电仿真的结果对比可以看出,DVDD上升时间从0V到1V都用了约10us,这也是对电容充电的过程。同时测试过程中的电流比100ns上电仿真的电流略大,原因是负载电容较大,需要用更大的电流进行充电。

需要注意的是对负载电容充电的电流来自于VR的1.8V DVDD输出,因此当电源(3.3V)上电速度较快的情况下,负载电容充电与上电时间没有特别大的关系。(由100ns上电仿真结果和测试结果看出,充电过程主要是在DVDD上升时开始的)

因此通过上电测试结果可以看出,VR的设计满足设计需求,上电过程中没有出现过大的电流,同时上电的特性曲线与HSIM-VCS仿真结果相近。

另外通过芯片的应用开发,也证明数字部分的设计满足需求,芯片可以正确工作。

3.4 仿真时间

整个电路有约23万个器件和10万个节点。下表所示是各测例平台运行时间以及仿真时间:

可以看出仿真时间在3天以内,且精度基本满足要求,可对分析全芯片的功耗和电流曲线提供有效帮助。

4.0 全芯片数模混合功能仿真

4.1 目标

需要进行全芯片数模混合功能仿真的功能点有:

Ø接收解调频偏调整机制

Ø数据发送通路功能

ØRFIC数据通路收发通信

Ø全芯片的寄存器功能扫描

ØRFIC全芯片的收发通信

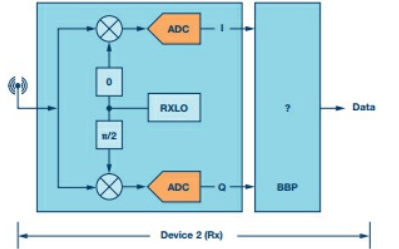

限于篇幅,笔者将重点介绍对接收解调频偏调整机制的仿真。在射频通讯系统中晶振很小的频率漂移可能会导致接收中频偏差较大,特别是在低中频方案中,当中频偏差与调频系统中的数据频偏可比拟时,数据就可能被淹没。为了解决这个问题,需要制定一种频率调整方案,这个方案可以根据接收中频的频率自动校正解调时钟,让解调时钟跟踪接收中频的偏差。接收解调频偏调整机制仿真目标如下:

Ø确认数模接口连接正确性

Ø确认频偏调整机制正确性

Ø各种特征数据的冲击

4.2 工具环境

评估初期,采用HSIM-VCS搭建混仿环境。由于设计规模较大,为了加速仿真,采用了XA-VCS搭建混仿环境,采用如下表所示的EDA工具和工作站环境。XA是Synopsys的新一代SPICE仿真工具,可以在实现仿真加速的同时得到好的仿真精度。XA可以通过DKI的方式实现与VCS的数模混合仿真验证。

4.3 仿真对象

Demodulator模块设计完成之后,与整个数字链路层整合,进行模块级数模混合仿真:

ØDLP,数字链路层,RTL代码

ØDemofdiv,分频数字模块,RTL代码

ØDemodulator,解调模拟模块,HSPICE网表

Ø其它模拟模块(Fm_Modulator、Limiter、Shifter),Verilog-A模型

4.4 仿真脚本

参照Synopsys技术支持团队提供的XA-VCS混仿范例中的以Verilog为顶层的例子,仿真脚本编写如图10。

图10仿真脚本

4.5 仿真激励

(A)Fm_Modulator的压控信号VIN输入激励:前面一段纹波较大,仿真PLL还没有完全锁定时的情形,中间一段为带+/-30KHz纹波的中频,仅接着后面为前导,然后是数据:1010001000111011100011100010101110100010。该组数据考虑了各种数据的组合。

(B)为模拟内部信号对VREF的干扰带来的影响,VREF端口激励采用下图方式:

图 11 VREF端口激励

(C)为模拟电源上纹波的影响,在电源上添加50mVp的2MHz信号和50mVp的32MHz信号。

(D)demodulator的电源AVDD、DVDD、AVSS、DVSS均添加了5nH的bonding wire 电感。

针对以上激励,做了如下内容的仿真:

(a)输入信号激励采用A中所述激励,其它如VREF、电源、地都采用理想激励,中频载波频率从从1.6M~2.4MHz,step为10KHz,共81个测例。

(b)以上A、B、C、D均采用,输入中频分别为1.6M、1.65M、1.69M、1.7M、1.71M、1.8M、1.9M、2M、2.1M、2.2M、2.29M、2.3M、2.31M、2.35M、2.4M共15个激励。工艺模型和温度划分为四种情况:TT,27℃;TT,-40℃;SS,85℃;FF,-40℃。

4.6 仿真结果

(1)仿真内容(a)的81个测例均正常。

图12仿真内容(a)结果波形

(2)仿真内容(b)的结果:60个测例中,有7个测例出现前导判决不出来的错误,即前导两个bit的宽度差异性较大,已超出了设计允许范围,不支持;其它测例结果正确。与实测结果一致。

图13仿真内容(b)结果波形

4.7 仿真时间

仿真时间记录如下:

4.8 小结

通过接收解调频偏调整机制数模混合仿真时间量化表,可以发现在同样可接受的精度情况下,XA-VCS的仿真速度是HSIM-VCS的10倍以上;所以在该RFIC全芯片的收发通信数模混合仿真中,节省的时间量级为8.5 * (10-1)days = 76.5 days = 2.55 months。

5.0 总结

在该RFIC测例中,利用HSIM-VCS和XA-VCS进行数模混合仿真,发现了设计Bug 8处,并可以节省大量的验证时间。

从该芯片的物理测试结果来看,利用该方法确实可以较为准确的获取到芯片的功耗信息,确保数模接口功能,为投片成功保驾护航。

-

功率放大器

+关注

关注

102文章

3583浏览量

131872 -

EDA工具

+关注

关注

4文章

267浏览量

31793 -

仿真器

+关注

关注

14文章

1018浏览量

83740 -

射频收发器

+关注

关注

4文章

256浏览量

25401 -

寄生电感

+关注

关注

1文章

155浏览量

14599

发布评论请先 登录

相关推荐

高性能PHS—RF收发器芯片设计方案

RadioVerse生态系统中的宽带收发器

如何采用超低功率RF收发器芯片实现体内通信系统的设计讨论

RadioVerse生态系统中的宽带收发器分享!

什么是用于RF收发器的简单基带处理器?

如何采用RF收发器实现体内通信系统的设计?

优化信号链的电源系统 — RF收发器

优化信号链的电源系统 — RF收发器

系统级RF收发芯片nRF24E1及其在无线键盘中的应用

通过采用超低功率RF收发器芯片设计植入式医疗设备的通信系统

如何使用RF收发器实现简单的基带处理器

HSIM, XA及其与VCS的混合验证方案在RF收发器芯片中的应用

HSIM, XA及其与VCS的混合验证方案在RF收发器芯片中的应用

评论