电子发烧友网报道(文/周凯扬)8年前,RISC-V横空出世,前3年似乎还默默无闻的一个ISA,到了如今已经被视为不少芯片设计公司的首选架构。也正是靠着8年间的生态发展与技术积累,RISC-V的身影已经开始出现在半导体市场的各个应用中,而去年与今年的RISC-V,更是开启了新一轮的扩张。除了常见的消费电子、工业控制这些起量迅速的应用领域,又或是AI、HPC这些新架构更容易扎根生长的领域外,如今的RISC-V早已开启了向更多应用辐射的进程。

为机械硬盘提速,支持高性能企业级SSD

随着企业与数据中心端的数据爆发式增长,根据统计数据到2026年,数据总量将达到221 Zettabytes。其中占据大头的已经不再是离线存储的冷数据,在推荐算法和生成式AI如此盛行的当下,需要被计算节点频繁访问的在线类热数据成了重头戏。也正是因为如此,不少存储厂商开始考虑设计更高性能的芯片,来满足日益增长的存储性能需求。

以希捷为例,多年以来他们一直在使用较为简单的自研ISA CPU,而到了2015年,在为这一CPU开发编译器支持时发现了RISC-V,随即决定基于RISC-V开发全新的CPU。新的CPU设计提供了超高的实时处理性能,很快就被用于希捷的机械硬盘中,用于实现硬盘电机中更为先进的控制算法。比如采用多读写臂的MACH.2机械硬盘等,多驱动系统的设计使得其IOPS性能翻倍。

在机械硬盘上获得应用后,RISC-V也很快覆盖到了固态硬盘上。去年群联发布了下一代PCIe Gen4x4的可客制化企业级SSD解决方案平台X1,希捷也借助这一平台推出了Nytro 5050系列SSD。而在X1所用主控PS5020-E20上,群联用到的正是晶心科技的N25F RISC-V内核。N25F采用了5级流水线设计,加上晶心科技提供的ACE框架,为定制化的专用指令提供了更高的灵活性,所以该内核在嵌入式控制器市场备受欢迎。

KUHAN Aurora主控 / 库瀚科技

除了PCIe 4.0的SSD主控外,国内也推出了基于RISC-V的PCIe 5.0 SSD主控,来自库瀚科技的KUHAN Aurora芯片。该芯为企业级PCIe 5.0x4、NVMe 2.0固态硬盘主控芯片,最大支持容量可以做到32TB。从其读写性能来看,Aurora可以实现14000MB/s的读取速度和10000MB/s的写入速度。此外,库瀚科技还开发了基于RISC-V架构的存储服务器专用处理器芯片(SPU),用于替代传统CPU核心的存储服务器主控,高效管理SCM、SSD和HDD等不同存储介质。

从车规MCU到ADAS

其实早在前两年,RISC-V就已经开始耕耘汽车芯片领域了,只不过当时面世的车规级芯片并不多,量产的更是寥寥无几。可随着设计流程完善、设计工具与AI车规认证完成,车厂对于跳出架构/供应商绑定、转向软件定义的意愿越来越强,RISC-V上车已经近在咫尺了。比如今年年底即将流出工程样片,计划2025年量产的Mobileye EyeQ Ultra芯片,又或是已经出货,主要用于Zone/Domain控制ECU与ICE、TCU等车身运动的瑞萨RH850/U2B MCU。

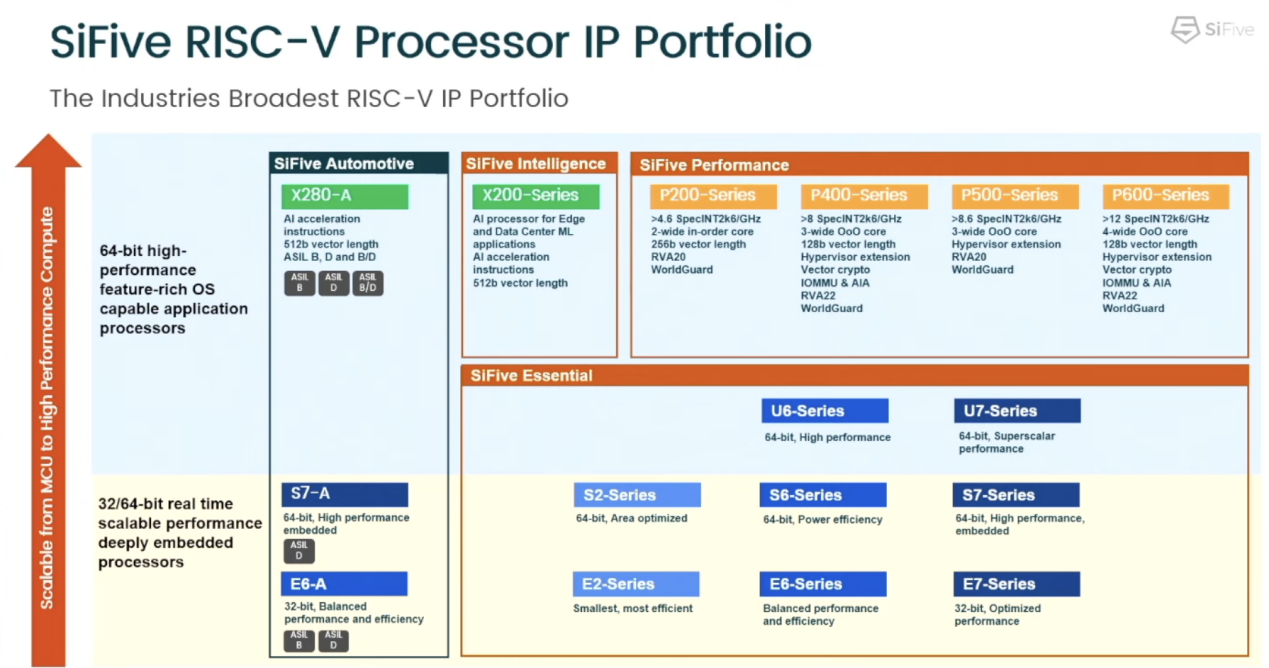

SiFive RISC-V处理器IP产品线 / SiFive

再以IP厂商SiFive为例,曾带领高通成功扩张汽车市场的高管Patrick Little成为SiFive CEO后,SiFive将更多的重心放在了AI和汽车领域,今年更是主要集中在汽车芯片IP上。从其已经公布的车规IP阵容来看,先一步面世的为用于车规MCU、系统控制器的E6-A系列,除了满足ASIL车规标准外,双核锁步等常见功能安全冗余设计也都一并支持。

其次就是将在今年推出,主打Vector运算的X280车规变体X280-A系列了。该系列主打更强的AI算力,同时也支持双核锁步、DCLS之类的特性。可即便拥有和X280相当的性能,但SiFive对X280-A的定位仍不是直接用于ADAS、IVI或中央网关,而是主打车载视觉或传感器融合之类的计算应用。不过SiFive也已经在规划更强性能的车规RISC-V IP产品系列了,相信不久后就能完善在汽车领域的IP布局。

最后则是明年才会推出的S7-A,这一核心同时兼顾了实时性和高性能,SiFive表示该IP更适合用于车规SoC中高性能安全岛的设计,因为这类应用既需要支持低延时终端,又要有着像其他主流应用处理器一样的64位内存空间可见性,也正因如此SiFive目前只为S7-A提供了ASIL-D的功能安全等级选项。

从物联网到商业化通信

多数人不知道的是,除了Wi-Fi、蓝牙之类的物联网通信芯片外,RISC-V已经进军商业化成熟度更高的5G、蜂窝通信领域。不久前我们已经介绍了国内几家厂商发布的RISC-V Cat.1芯片,而在5G基站芯片上,RISC-V也已经撕开了一道口子。例如国内厂商比科奇推出的PC802芯片,就是专为Open RAN等标准设计的4G/5G小基站基带SoC。

比科奇PC802芯片 / 比科奇

PC802基于CEVA XC12的矢量信号处理器和晶心科技的N25F标量RISC-V处理器设计,不仅支持R15和R16版本的3GPP 5GNR,还支持5GNR/LTE双模,且可对两个物理层分别处理或单芯片同时处理,非常适合用于开发4G+5G的双模小基站。随着5G小基站迈入规模增长期,PC802这样的基带芯片势必也会在运营商的大规模集采中收获更多的市场机会。

同样在这一应用场景上发力的还有EdgeQ,他们打造的5G片上基站方案采用了RISC-V用于5G信号处理,8核的Arm Neoverse CPU+NPU作为子系统的一体化SoC方案。其中信号处理部分由多个RISC-V标量核心组成,每个核心都拥有多级流水的运算单元,并支持FFT、复合调制在内的50个定制扩展/指令。目前EdgeQ已经开始和MaxLinear等厂商合作,开发一体化的5G小基站设计。

写在最后

即便如此,RISC-V还是存在不少尚未覆盖到的应用,比如目前基于RISC-V的AI芯片已经有了不少产品面世,但基于该架构的GPU却迟迟没有出现,RISC-V芯片在高级图形处理上仍然有所欠缺,所以大部分RISC-V SoC还是只能选择集成Imagination的GPU IP。

再者就是用于高端消费电子产品的芯片,比如高性能的手机或笔记本处理器等,在这类应用上,硬件性能与软件适配都有所欠缺,部分先行者已经开始布局,但仍需要大量的生态合作和创新才有可能从Arm、x86虎口夺食。

-

RISC-V

+关注

关注

44文章

2267浏览量

46114

发布评论请先 登录

相关推荐

RISC-V拥有巨大市场潜力的原因

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,赋能RISC-V高效落地

2024 RISC-V 中国峰会:华秋电子助力RISC-V生态!

rIsc-v的缺的是什么?

RISC-V适合什么样的应用场景

RISC-V在中国的发展机遇有哪些场景?

浅析RISC-V领先ARM的优势

risc-v的mcu对RTOS兼容性如何

RISC-V的MCU关于USB高速通信设计的难点

RISC-V的MCU与ARM对比

论RISC-V的MCU中UART接口的重要性

RISC-V有哪些优点和缺点

RISC-V有哪些优缺点?是坚持ARM方向还是投入risc-V的怀抱?

解锁RISC-V技术力量丨曹英杰:RISC-V与大模型探索

辐射至存储、汽车与通信市场,RISC-V的适用性毋庸置疑

辐射至存储、汽车与通信市场,RISC-V的适用性毋庸置疑

评论