信号完整性分析越来越重要

芯片和电子产品一直都在向小型化、高度集成化以及高速化的方向发展,可产品的研发周期却越来越紧迫。这对工程师们来说是一个巨大的考验。

无论是数据中心的产品、还是汽车和工业设备,甚至是我们日常使用的消费电子产品,它们的信号速率都在迅猛攀升!

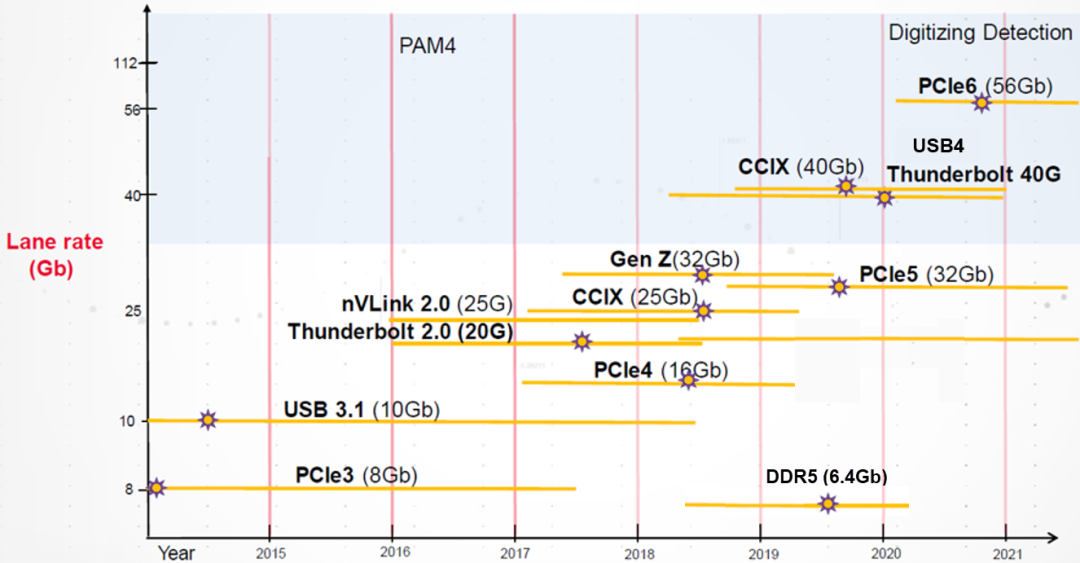

看看下面这张图,PCIe6.0的速率已经达到了56Gbps,USB4达到了40Gbps,并行总线DDR5也达到了惊人的6.4Gbps,同时,高速总线的调制模式也从以往的NRZ发展到了PAM4甚至更高阶的调制技术。

还有一些新型总线的出现,比如CCIX, GenZ,CXL等等。这些变化给工程师们带来了前所未有的挑战,也使得信号完整性分析变得比以往更加重要。

信号完整性是信号传输的一个综合指标,它涵盖了发送端、接收端以及传输路径中的PCB、连接器、线缆或其他无源器件对信号的影响。各种总线协议都对这些部分有相应的定义,例如PCIe总线。

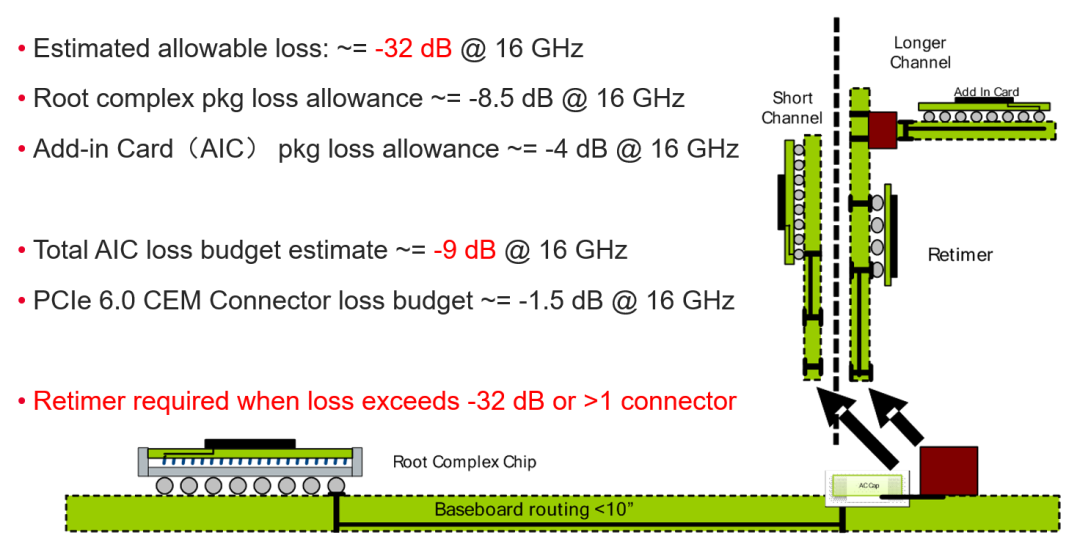

下图展示了PCIe6.0规范中对各个部分插入损耗的定义。无论是进行仿真还是测试,都需要确保满足这一标准。

PCIe6.0 InsertionLoss

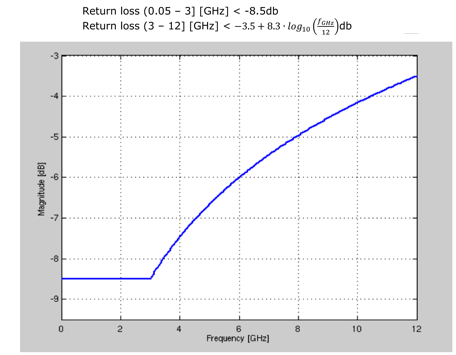

下面这张图展示了在USB4和Thunderbolt3.0规范中定义的传输通道的回波损耗。同样地,在OIF规范中,我们也可以找到插入损耗、回波损耗等等的明确定义。这些标准为我们的工程师在设计过程中提供了宝贵的参考依据。

Thunderbolt3.0 and USB4 Return Loss

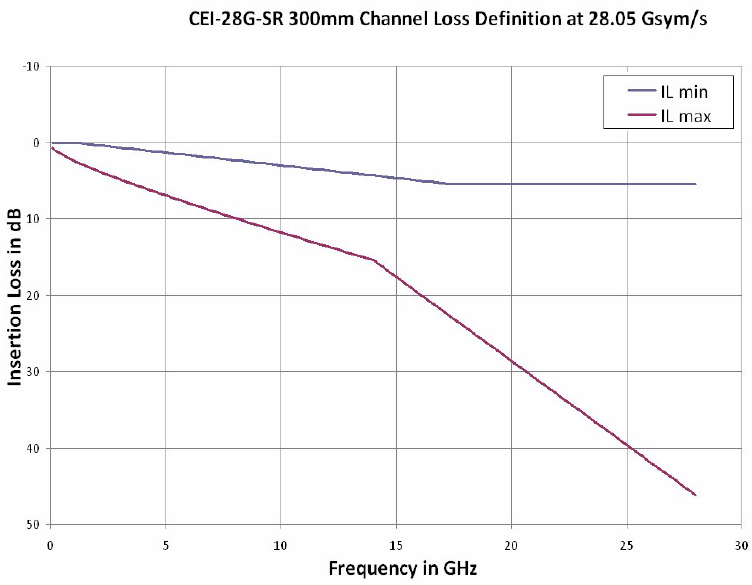

CEI-28G-SR Channel Insertion Loss

一般来说,当我们分析信号完整性时,我们会关注眼图、时序、阻抗、插入损耗、回波损耗、串扰等等因素。但随着信号速率的不断提高和传输方式的多样化,信号完整性分析的指标也变得更加多样化。在原来的基础上我们还需要考虑ICN、ICR、COM、ILD、BER等等指标。这无疑给信号完整性工程师增加了很大的工作量。

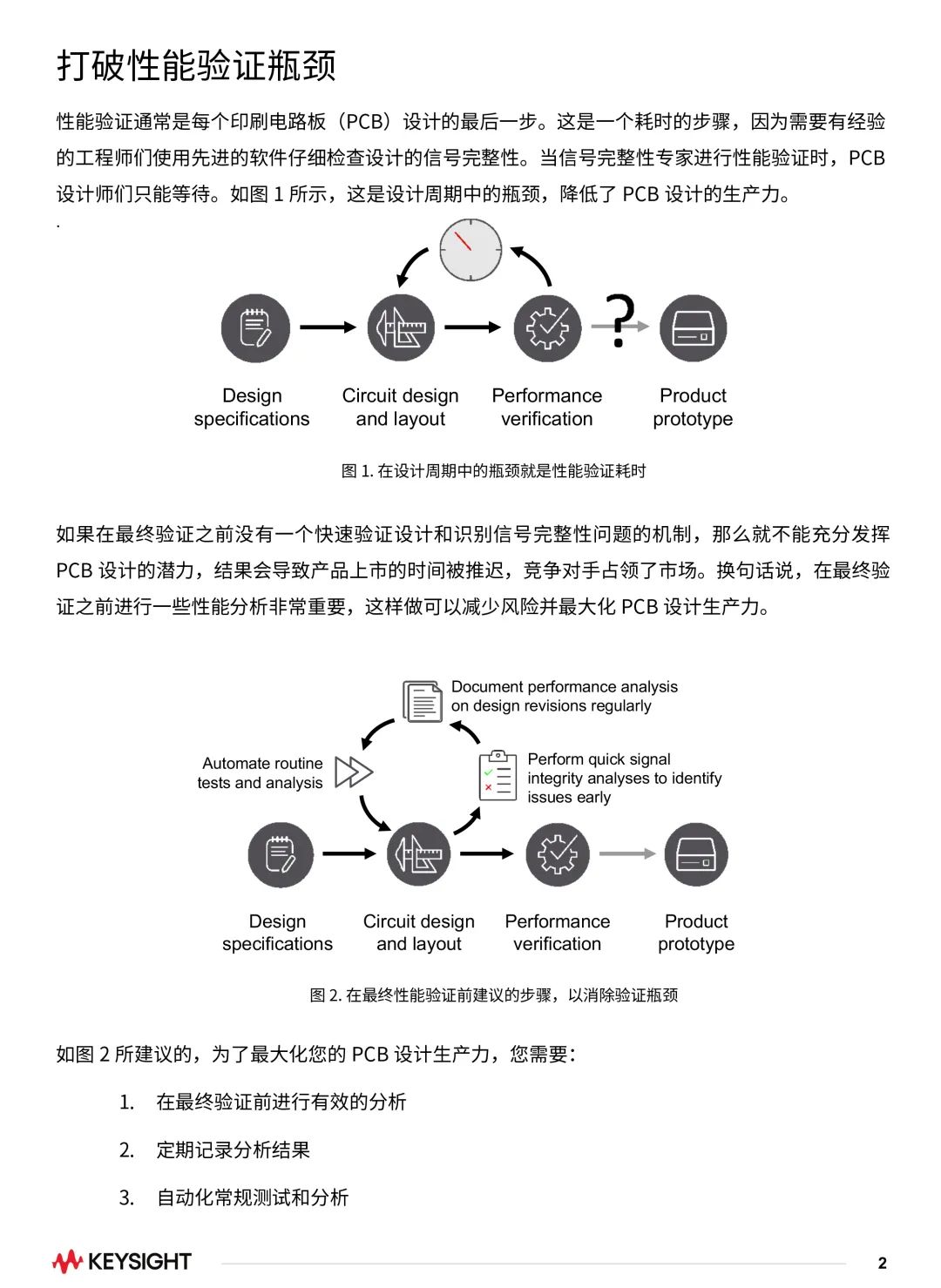

在高速数字电路设计中,硬件工程师通常会将设计交给信号完整性工程师进行分析,他们通过详尽复杂的分析来发现潜在问题和隐患。尽管现如今的信号完整性分析工具功能强大且高效,能够节省大量时间,但整个信号完整性仿真过程仍然是相当耗时的。

此外,信号完整性工程师在公司中的数量通常比硬件工程师少得多,这导致信号完整性分析成为整个设计流程的一个瓶颈。

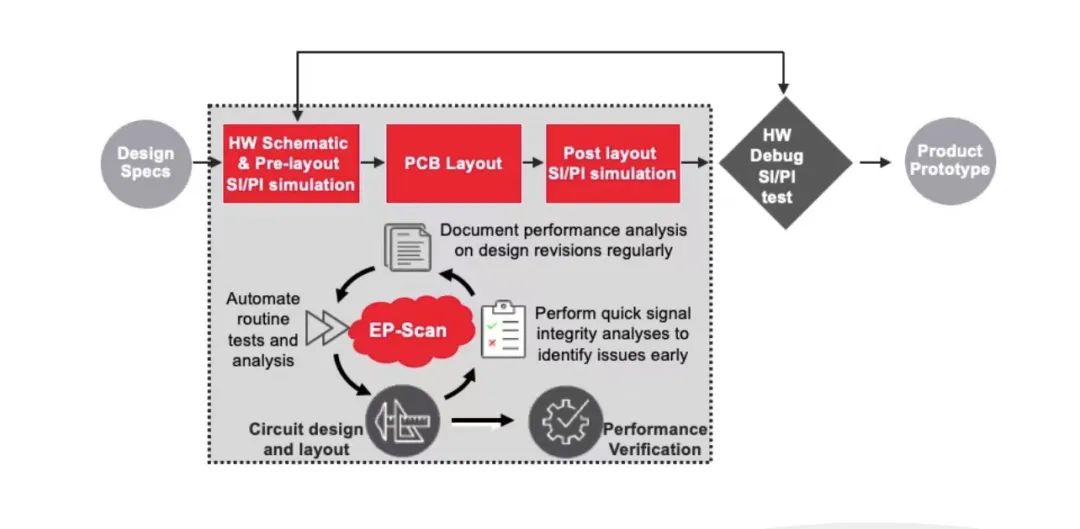

为了突破性能验证的瓶颈,是德科技在今年初推出了EP-Scan(Electrical Performance Scan)电气性能扫描软件,它为我们提供了一种快速检测电气性能的方法,让硬件工程师们能够及时发现初级的SI问题,避免后期可能出现的麻烦。有了它,硬件工程师只需简单的操作,就能进行快速扫描,查看信号的电气特性,找出潜在的信号完整性问题。

当然,对于更复杂的信号完整性分析,依然需要SI工程师们的专业知识和技能,通过深入的分析和仿真来解决。

接下来,让我们一起来了解如何通过简单的三个步骤解决信号完整性分析中的瓶颈问题。

第一步,加载设计和设置。

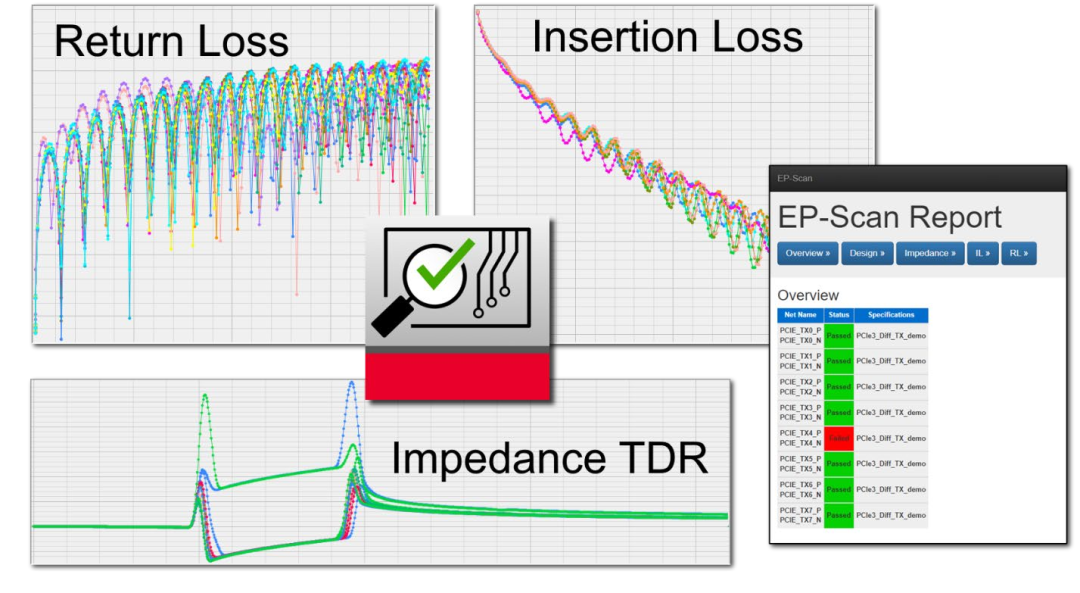

使用EP-Scan,我们可以轻松加载PCB Layout设计或导入ODB++文件。然后,我们选择特定的网络进行分析,更棒的是,我们还能为这个网络设定测试计划,并选择相应的电器规范(EP-Scan内置了一些电器规范,如PCIE、USB、DDR等),然后根据相应的电气规范对阻抗、延时、插入损耗和回波损耗等指标进行分析。

第二步,进行电气性能扫描。

这个步骤非常简单,只需轻轻按下一个按钮,就能一键运行所有的测试计划。此外,每当我们对设计进行修改时,我们可以再去自动运行EP-Scan里面事先设定好测试计划,以便轻松检查信号完整性问题。这样,我们可以在修改后立即获得反馈,确保设计的稳定性和可靠性。

第三步,生成报告和存档。

在完成信号完整性分析后,EP-Scan可以一键生成详细的报告。这个功能极大地简化了结果的展示和存档过程,避免了繁琐的复制粘贴工作。我们可以轻松地分享分析结果给团队成员或管理层,并记录下设计的进展和改进。这样,我们能够保持透明的沟通和高效的工作流程。

通过这三个简单的步骤,EP-Scan为硬件工程师提供了方便、高效的工具,简化了分析流程,节约时间和精力。它突破了性能验证瓶颈,让您专注于设计的优化和改进,更快地将产品推向市场。

EP-Scan生成的测试报告

点击查看

关于是德科技

是德科技(NYSE:KEYS)启迪并赋能创新者,助力他们将改变世界的技术带入生活。作为一家标准普尔 500 指数公司,我们提供先进的设计、仿真和测试解决方案,旨在帮助工程师在整个产品生命周期中更快地完成开发和部署,同时控制好风险。我们的客户遍及全球通信、工业自动化、航空航天与国防、汽车、半导体和通用电子等市场。我们与客户携手,加速创新,创造一个安全互联的世界。

-

工程师

+关注

关注

59文章

1566浏览量

68433 -

PCB设计

+关注

关注

394文章

4670浏览量

85248 -

总线

+关注

关注

10文章

2864浏览量

87972 -

信号完整性

+关注

关注

68文章

1397浏览量

95376 -

PCIe

+关注

关注

15文章

1217浏览量

82423 -

是德科技

+关注

关注

20文章

868浏览量

81668

原文标题:突破信号完整性分析瓶颈:3步轻松驾驭PCB设计

文章出处:【微信号:是德科技KEYSIGHT,微信公众号:是德科技KEYSIGHT】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

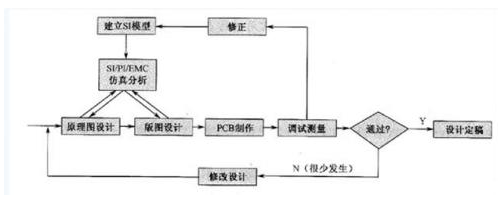

基于信号完整性的高速PCB设计流程解析

突破信号完整性分析瓶颈:3步轻松驾驭PCB设计 三个步骤解决信号完整性分析的瓶颈问题

突破信号完整性分析瓶颈:3步轻松驾驭PCB设计 三个步骤解决信号完整性分析的瓶颈问题

评论