MOSIS:ORBIT 2.0u SCNA规则

v1 Vdd Gnd 5.0

v2 Clk Gnd pulse(0.0 5.0 0 10n 10n 100n 200n)

v4 ClB Gnd pulse(0.0 5.0 0 10n 10n 1000n 1000n)

v3 Data Gnd pulse(0.0 5.0 0 10n 10n 80n 150n)

########################################

逻辑综合完成之后,通过引入器件制造公司提供的工艺信息,前面完成的设计将进入布图规划、布局、布线阶段,工程人员需要根据延迟、功耗、面积等方面的约束信息,合理设置物理设计工具的参数,不断调试,以获取最佳的配置,从而决定组件在晶圆上的物理位置。如果是全定制设计,工程师还需要精心绘制单元的集成电路版图,调整晶体管尺寸,从而降低功耗、延时。

随着现代集成电路的特征尺寸不断下降,超大规模集成电路已经进入深亚微米级阶段,互连线延迟对电路性能的影响已经达到甚至超过逻辑门延迟的影响。这时,需要考虑的因素包括线网的电容效应和线网电感效应,芯片内部电源线上大电流在线网电阻上造成的电压降也会影响集成电路的稳定性。为了解决这些问题,同时缓解时钟偏移、时钟树寄生参数的负面影响,合理的布局布线和逻辑设计、功能验证等过程同等重要。随着移动设备的发展,低功耗设计在集成电路设计中的地位愈加显著。在物理设计阶段,设计可以转化成几何图形的表示方法,工业界有若干标准化的文件格式(如GDSII)予以规范。

-

电容器

+关注

关注

64文章

6315浏览量

100645 -

电感器

+关注

关注

20文章

2345浏览量

71011 -

仿真器

+关注

关注

14文章

1019浏览量

84121 -

晶体管

+关注

关注

77文章

9830浏览量

139437 -

D触发器

+关注

关注

3文章

164浏览量

48154

发布评论请先 登录

相关推荐

D触发器,CLK突变时,输入D也突变,触发器的输出应该如何判定?

jk触发器是什么原理_jk触发器特性表和状态转换图

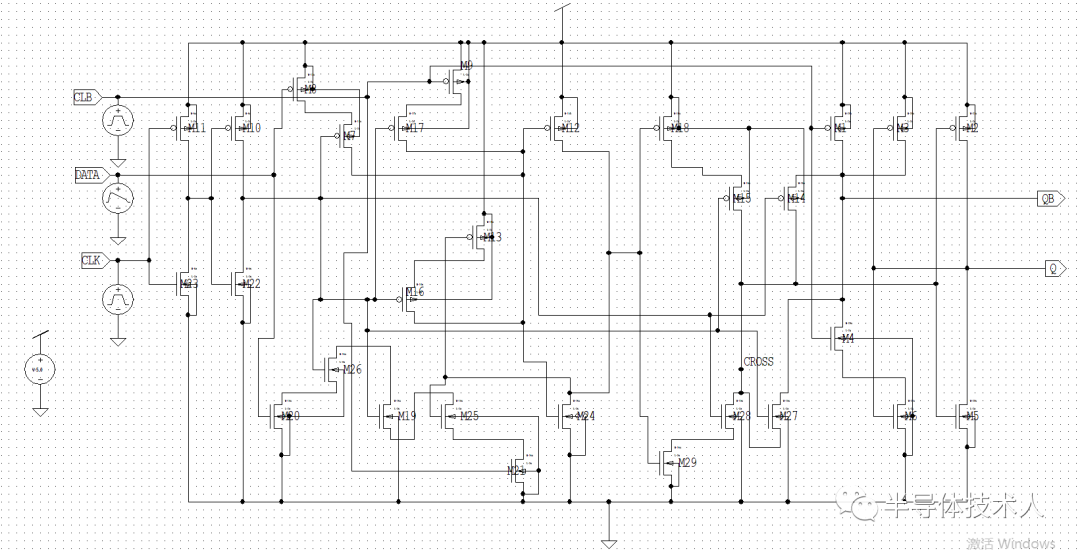

D触发器版图电路瞬态特性仿真

D触发器版图电路瞬态特性仿真

评论