11日,据韩国经济新闻报导,三星电子将4纳米node级半导体组的收益率提升到了竞争公司台积电 (TSMC)的水平。

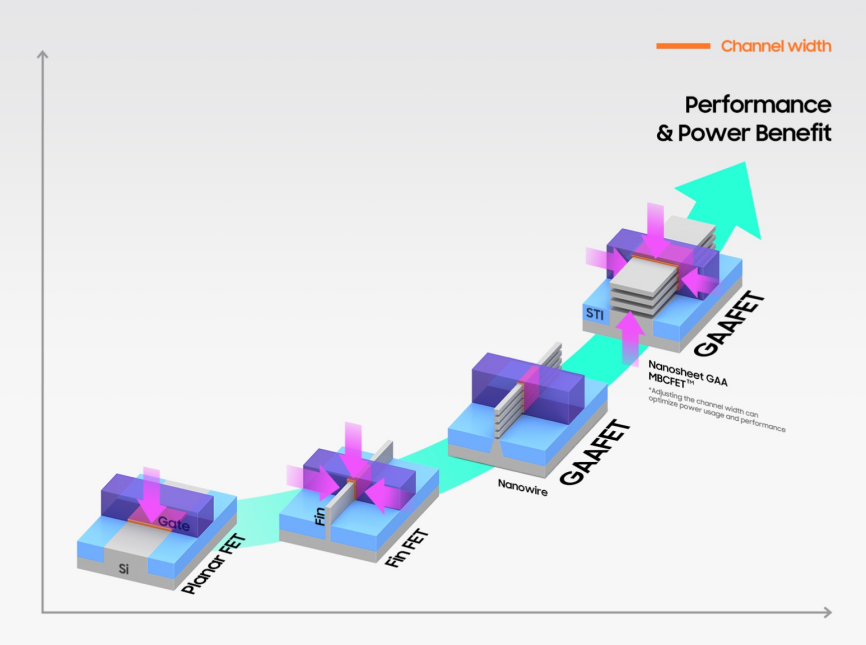

据悉,HI Investment & Securities投资证券半导体分析师Park Sang-wook发表研究报告称,三星电子的4纳米和3纳米工程节点的半导体产量分别提高到75%和60%以上。

据《韩国经济新闻》报道,直到今年年初,业界还预测三星的4纳米技术收益率为50%左右。4纳米和3纳米等尖端工程的收率超过60%,意味着使用这些工程的芯片收率处于稳定水平。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

半导体

+关注

关注

335文章

27826浏览量

223882 -

三星电子

+关注

关注

34文章

15880浏览量

181405 -

纳米

+关注

关注

2文章

699浏览量

37229

发布评论请先 登录

相关推荐

三星3nm良率仅20%,仍不放弃Exynos 2500处理器,欲打造“十核怪兽”

,导致Exynos 2500良率不佳的原因是,这颗SoC基于三星第二代3nm GAA制程工艺——SF3工艺,然而目前第二代SF

三星电子1c nm内存开发良率里程碑推迟

据韩媒报道,三星电子已将其1c nm DRAM内存开发的良率里程碑时间推迟了半年。原本,三星计划在2024年底将1c

三星1c nm DRAM开发良率里程碑延期

据韩媒MoneyToday报道,三星电子已将其1c nm(1-cyano nanometer)DRAM内存开发的良率里程碑时间从原定的2024年底推迟

台积电2nm芯片试产良率达60%以上,有望明年量产

近日,全球领先的半导体制造商台积电在新竹工厂成功试产2纳米(nm)芯片,并取得了令人瞩目的成果。试产结果显示,该批2nm芯片的良

台积电3nm制程需求激增,全年营收预期上调

台积电近期迎来3nm制程技术的出货高潮,预示着其在半导体制造领域的领先地位进一步巩固。随着苹果iPhone 16系列新机发布,预计搭载的A18系列处理器将采用台积

三星3nm芯片良率低迷,量产前景不明

近期,三星电子在半导体制造领域遭遇挑战,其最新的Exynos 2500芯片在3nm工艺上的生产良率持续低迷,目前仍低于20%,远低于行业通常要求的6

台积电3nm工艺稳坐钓鱼台,三星因良率问题遇冷

近日,全球芯片代工领域掀起了不小的波澜。据媒体报道,台积电在3nm制程的芯片代工价格上调5%之后,依然收获了供不应求的订单局面。而与此同时,韩国的三星电子在

传三星电子12nm级DRAM内存良率不足五成

近日,据韩国媒体报道,三星在其1b nm(即12nm级)DRAM内存生产过程中遇到了良率不足的挑战。目前,该制程的

台积电3nm工艺产能紧俏,苹果等四巨头瓜分

据台湾媒体报道,近期全球芯片制造巨头台积电面临了3nm系列工艺产能的激烈竞争。据悉,苹果、高通、英伟达和AMD这四大科技巨头已经率先瓜分完了台积电

三星电子:加快2nm和3D半导体技术发展,共享技术信息与未来展望

在技术研发领域,三星电子的3nm与2nm工艺取得显著进步,预计本季度内完成2nm设计基础设施的开发;此外,4nm工艺的

三星电子澄清:3nm芯片并非更名2nm,下半年将量产

李时荣声称,“客户对代工企业的产品竞争力与稳定供应有严格要求,而4nm工艺已步入成熟良率阶段。我们正积极筹备后半年第二代3nm工艺及明年2nm

台积电扩增3nm产能,部分5nm产能转向该节点

目前,苹果、高通、联发科等世界知名厂商已与台积电能达成紧密合作,预示台积电将继续增加 5nm产能至该节点以满足客户需求,这标志着其在

三星电子3nm工艺良率低迷,始终在50%左右徘徊

据韩国媒体报道称,三星电子旗下的3纳米工艺良品比例仍是一个问题。报道中仅提及了“3nm”这一笼统概念,并没有明确指出具体的工艺类型。知情者透露,尽管有部分分析师认为其已经超过

传三星4nm良率水平追平台积电,3nm提至60%以上

传三星4nm良率水平追平台积电,3nm提至60%以上

评论