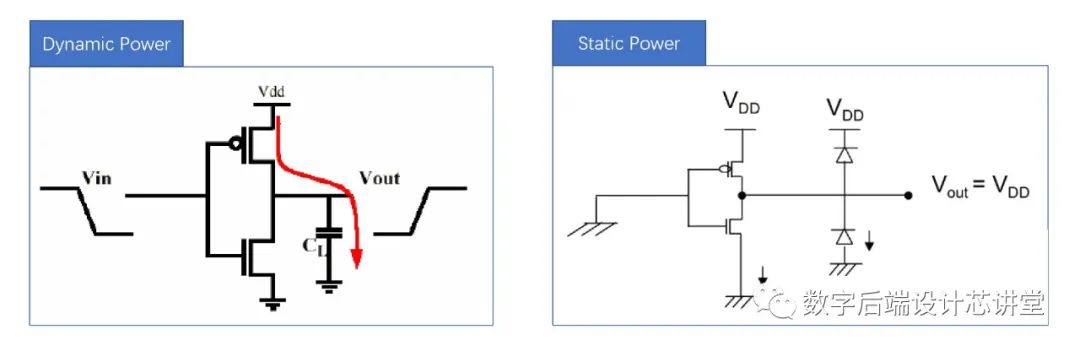

现在的深亚纳米工艺的设计中,低功耗已经是一个日渐总要的主题了,尤其是移动市场蓬勃发展起来之后,功耗的要求越来越严格,据传,在高级的手机系统开发的过程中,系统架构的设计,已经精确到每一个服务模块的毫安时(mAH)的级别,所以如果你的芯片功耗控制不下来,很有可能会被手机生产厂家踢出局。

在低功耗的世界里,我们有很多方法可做,譬如提高设计工艺(工艺节点越高,功耗就越小)UPF策略,代码优化等等。其中的clock gating方法就是一个解决内部功耗的有效办法

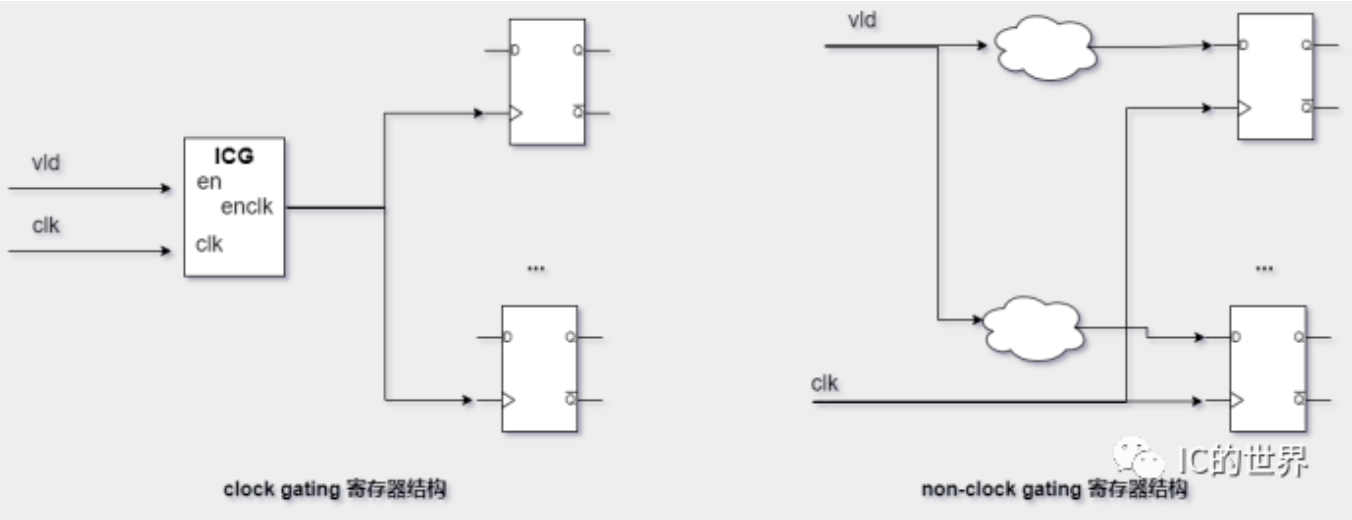

Clock gating从原理上讲,就是在FF的clock 的输入通路上,加入额外的逻辑,来使得FF在不发生变化的情况下,clock端没有反转,如果不采取这个策略,那么FF的clock pin是长时间翻转的,在D/Q都不翻生变化的时候,带来了额外功耗消耗,采用clock gating就可以有效境地这种损耗

从用途上讲,一般将Clock gating分为如下两类:

1:RTL实例化的clock gating cell

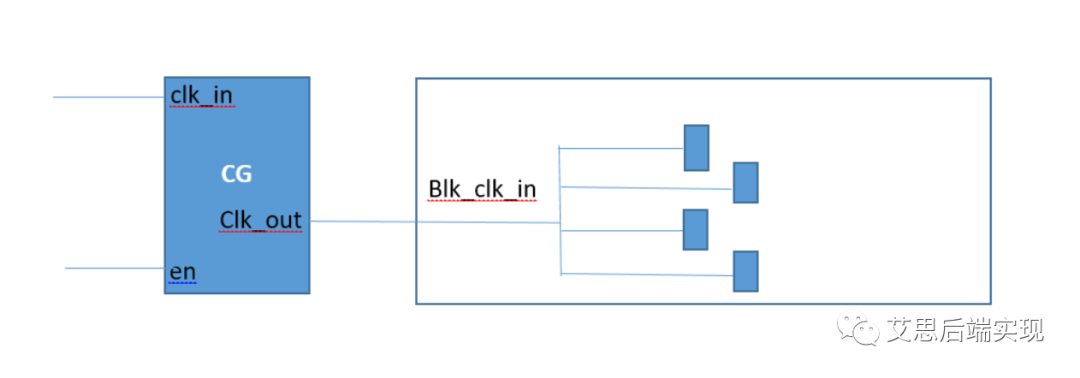

在很多的前端设计中,我们都会认为的实例化primitive clock gating cell,这里是按照前端的设计要求来的,一般这样的GC都是接近于clock 的源头,譬如一个模块的输入clock,我们使用一个实例化的GC来作为这个clock 的控制端,在不需要的时候,可以直接使用寄存器把他关断,从而达到节省模块级power的目的

这种GC结构,在结构上后端是不用干预的,但是由于这种GC的fanout 都很大,在某种情况下可能会引起比较悲观的setup violation。这个我们会在后边仔细描述

2:综合工具推断出(inferred )clock gating cell

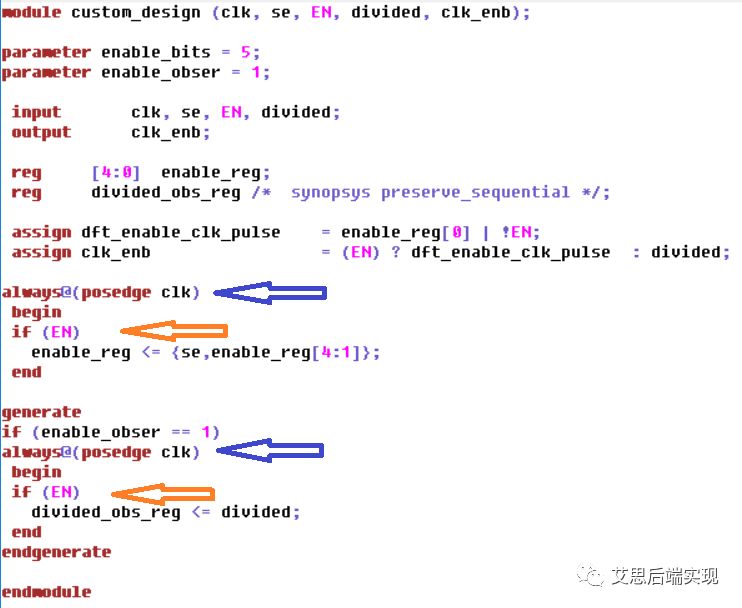

这种推断出的CG是基于综合器对RTL的理解,首先,我们的设计需要遵循一定得大妈风格(coding style),这是工具分析的基础,我们来看下面这段代码

蓝色箭头所指是clock的edge检测,这里是一个if 语句的开始,而后如橙色箭头所指,在clock edge的这个function里边,使用EN来做判别,如果EN为1的时候,产生赋值操作,这是一个标准的带同步enable的寄存器语法。

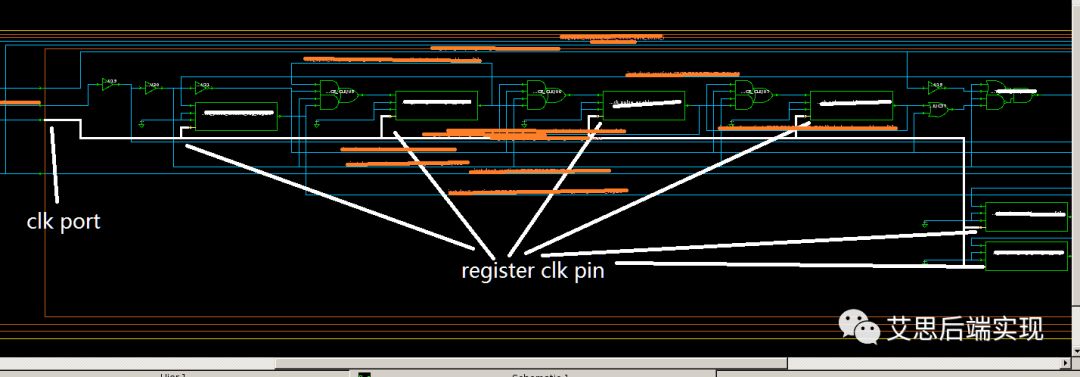

综合器会按照约定的规则来解析rtl code,然后产生对应的网表。按照通常的综合结果(compile_ultra),会得到下面这个结果

模块输入端的clock port会直接连接到所有的FF clock pin 上边,通常的器件库里边,没有带EN端的DFF,这是一种简化设计,因为所有的FF EN pin,都可以和D pin做组合逻辑,从而达到控制输出的结果。从土里可以看到,这里的EN也是被拉到了FF’D pin前级的组合逻辑的输入端,从而达到控制FF输出的结果。

这个时候,是没有clock gating的设计的,工具严格遵守RTL的设计产生了这段网表结构。

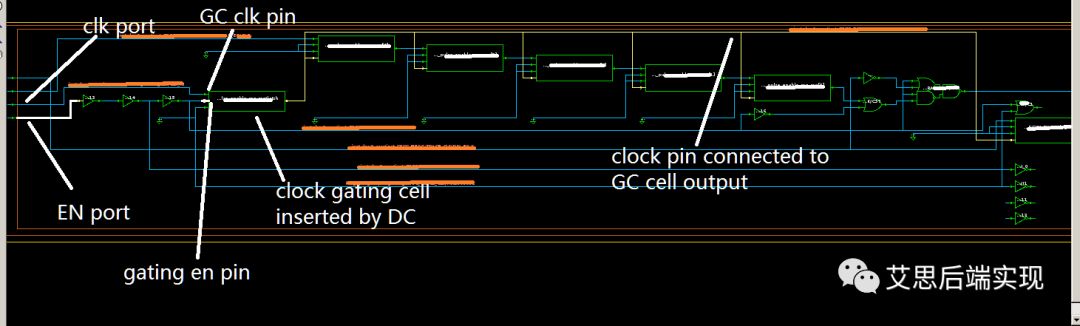

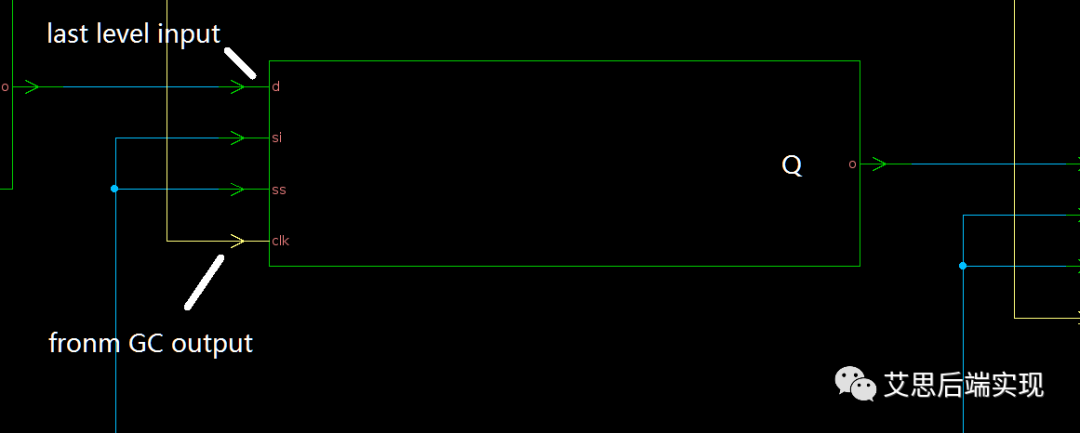

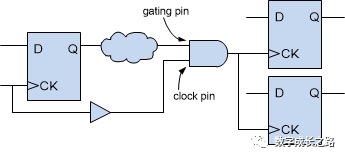

如果在综合的时候,打开inferred clock gating 选项(compile_ultra –gate_clock),这个时候会得到下面的这个结构。

这个时候的网编结构发生了变化,在紧跟clock port的后面,多了一个CG,EN的port 从之前的链接到各个FF 的D pin,到现在只连接到了clock gating cell的en pin上,通过控制FF的clk pin,来达到仅在EN使能的时候翻转clock来刷新FF的输出,从而达到省电。

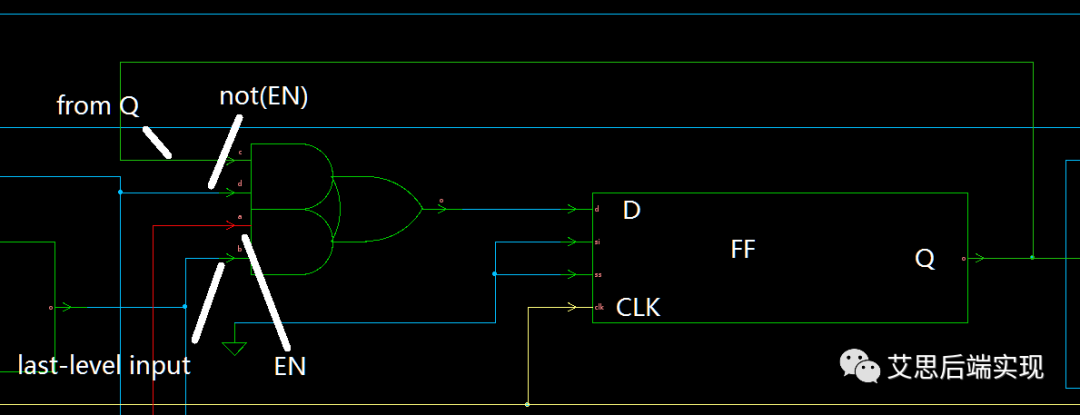

由于在没有使用CG之前,由于FF需要不停地刷新,DC为了保障FF的输出在EN端非使能的时候保持当前状态,所以一定有一条从Q到D的回路来保证FF的输出保持不变,类似下图

FF’D pin 前面的是一个四输入与或门,在EN为0的时候,FF会把Q的值反复刷新,尽管输出Q不改变,但是短路功耗是少不了的。

在使用了gate clock 以后,FF的结构变成了

可以看到,这里的FF的D输入端,变得更为简单了,以为所有前后级都被挂载到了同样的CG下面,只有当CG有输出clock的时候,这些FF才进行工作,工具就不用创建那些组合逻辑来考虑EN不使能的情况了。

就相同设计的面积比较,采用inferred CG策略的结果还可以节省面积

Area with CG: 8.0997

Area without CG: 8.3790

在一个3M gate-count的完整设计里边,可以看到,当打开gate_clock选项的时候,会增加大约7k的CG cell,时序逻辑大概增加了6%的面积,但是整个设计的std-cell的面积(组合加时序)反而降低了4%,从这方面看,综合器的这个功能对绝对面积和功耗都是有贡献的

讨论完CG的好处后,我们再来看一下Clock gating 的类别:

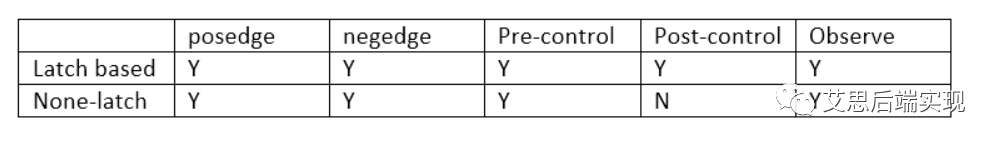

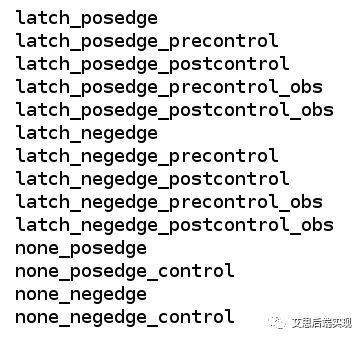

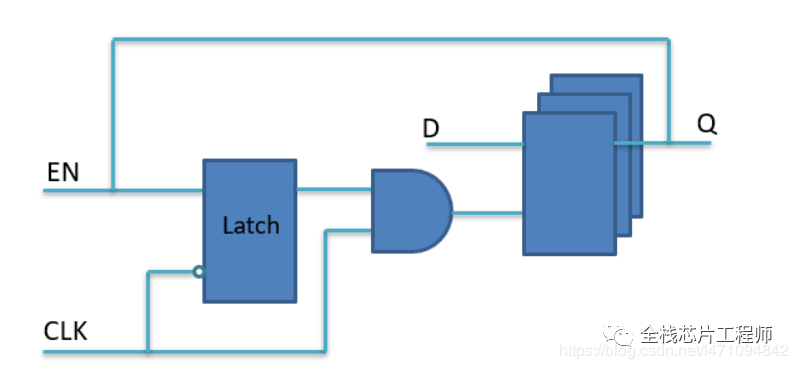

先看一下这个表格。通常上来讲,CG分为两类,一种是带latch的,另外一种是不带

latch的,由组合逻辑构成。

这里的模型规则如下

Posedge:

o Latch based:clk负沿敏感的latch

o None-latch:非或门结构的CG

Negedge:

o Latch based:clk正沿敏感的latch CG

o None-latch:与门结构CG

Pre-control:

o Latch based :latch的EN输入前插入一个或门,从而带入TE的管控

o None-latch: 在组合逻辑的EN输入侧插入一个或门,从而带入TE的管控

Post-control:

o Latch based :latch的output输出后插入一个或门,从而带入TE的管控

o None-latch: 不支持

Observe:

o再有pre/post control的设计中监控与门中非TS管控测的信号

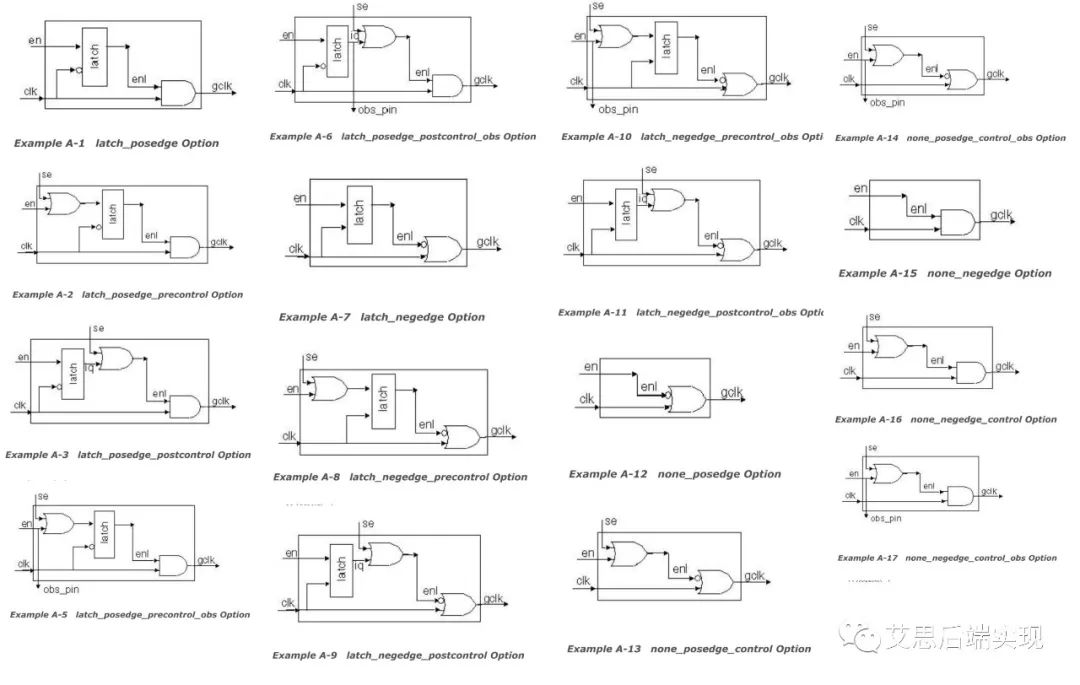

借用新思的电路图来给大家详细的示例(侵删)

由于clock是敏感信号 ,一般推荐使用latch-based gating CG,这要可以有效地过滤EN上的毛刺。

有了上边的知识,那么工具是如何识别和插入CG的的呢?

在综合的时候,需要在你的综合环境里边定义工具自动插入时可已使用的CG cell类型,然后唤起compile_ultra命令即可完成CG插入:

set_clock_gating_style -pos {integrated:CG_CELL_NAME} -control_point before -num_stages 4

compile_ultra –gate_clock

用户可以在compile结束后,使用report_clock_gating命令来查看数据库里边的CG情况。

这个报告很有意思,他可以打印出数据库里所有被CG控制的FF的情况,同时也会列出来没有被CG控制的FF的情况,并且会生成一些比率报告,有兴趣的同学可以仔细了解一下。

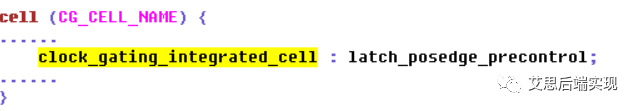

此外,这里边的CG_CELL_NAME,这个cell是一个真实存在在你的std-cell库里的实际CG,并且这个lib_cell必须要有一个特殊的属性:

DC只有看到这个属性的时候,才会认为这是一个真实可信的CG。而后按照他后边属性说明来进行inferred CG insertion,后面的属性无外乎我们前面表格里边罗列的那些属性,具体名词如下:

当然,DC也支持一些组合逻辑的CG的创建,如果你使用如下命令,DC会插入相应的none-lath结构的CG

set_clock_gating_style -pos {buf nand inv}

在同步设计的架构下,不推荐使用这样的gating 结构,由于这是拿两三个苏合逻辑器件搭乘的,后期的timing closure是很难做的,推荐使用library里边latch-based的CG。

上边用了一定的篇幅讲述了一下CG的特点、原理和初步实现。但是这还没有结束,应为还有layout的实现要考虑

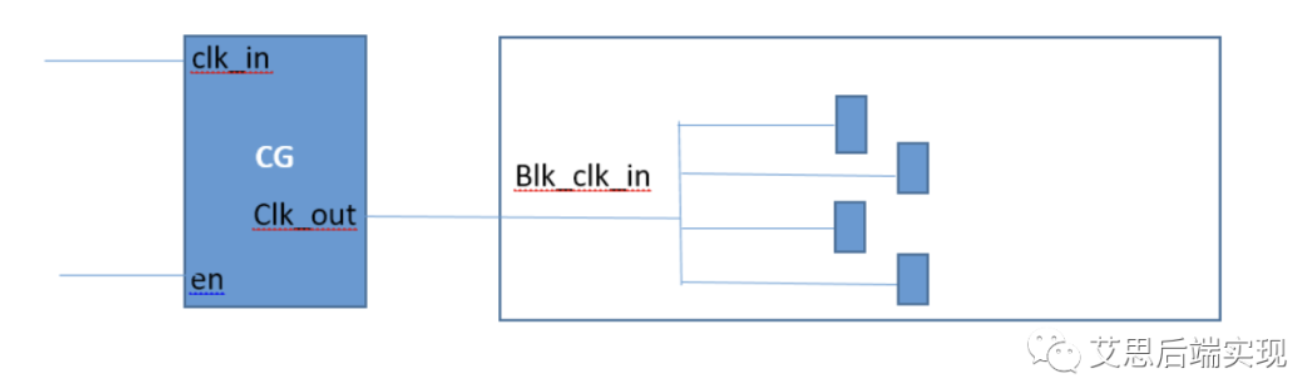

Clock_gating作为clock tree的一部分,在做layout的时候,有更多的因素需要考量

首先,所有的latch based CG都有一组setup/hold timing arc,就是clk –> EN的timing check

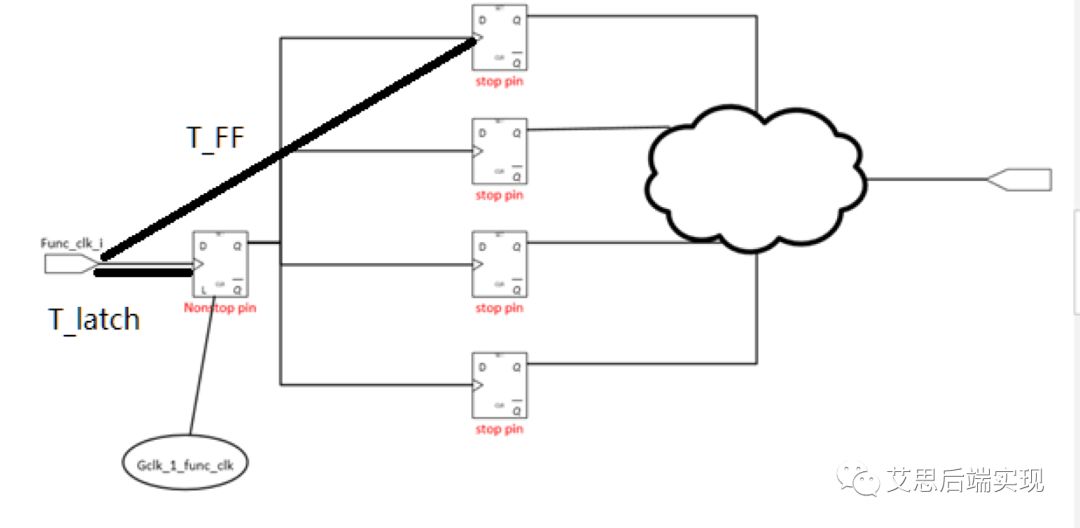

其次,在CTS的时候,clock-gating被当作了一个none-stop pin而非一个stop pin如下图示例:

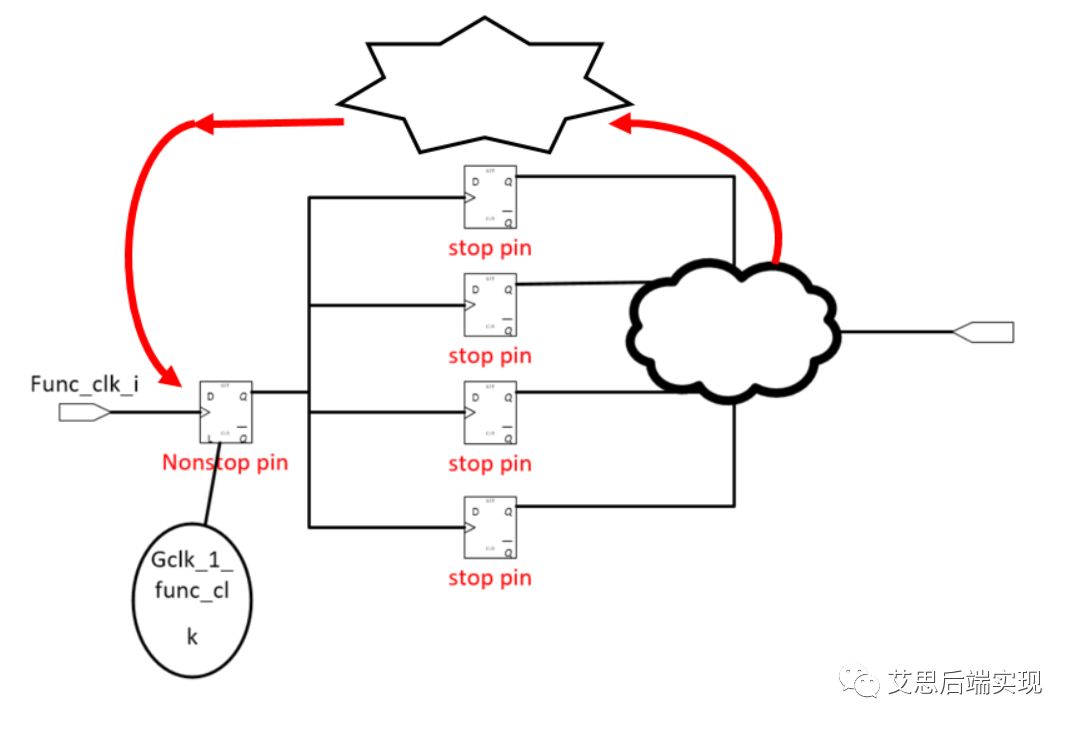

工具会balance 后面四个被gating 驱动的FF(stop pin)之间的skew,但是CG是它们的clock 的driver,不难想象,CG EN的latency(T_latch)一定小于CG fanout FF的clock latency(T_FF),这是一个永远不能改变的事实。在某些情况下会带来CG setup violaoiton,如下图:

如果有一条正面这样的data path存在,那么launch clk (FF) 一定是晚于capture clk (CG),在高频和复杂datapath的情况下,这样的timing是很难修复的

所以要在CTS之前解决或者简化这个问题,

解决这个问题的关键就是,让CG clock latency(T_latch)和fanout FF clk latency(T_FF) 尽可能的足够小。

要让前后两级的clock latency的差值足够小,其中有一个方法就是让他们的摆放足够近,在综合结束后,通过report_clock_gating的report可以看到所有CG和他的fanout的列表,这个时候,我们通过第一版的CTS结果,可以评估出那些FF-CG的timing是有困难的,这些FF以及他们的CG使用relative placement的方法,让工具在place 的阶段就把他们摆放的足够近,从而在物理距离上来解决这个CG 的setup 问题。

审核编辑:刘清

-

控制器

+关注

关注

112文章

16376浏览量

178188 -

寄存器

+关注

关注

31文章

5343浏览量

120419 -

RTL

+关注

关注

1文章

385浏览量

59813 -

UPF

+关注

关注

0文章

50浏览量

13523 -

dff

+关注

关注

0文章

26浏览量

3420

原文标题:Clock Gating之浅见

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

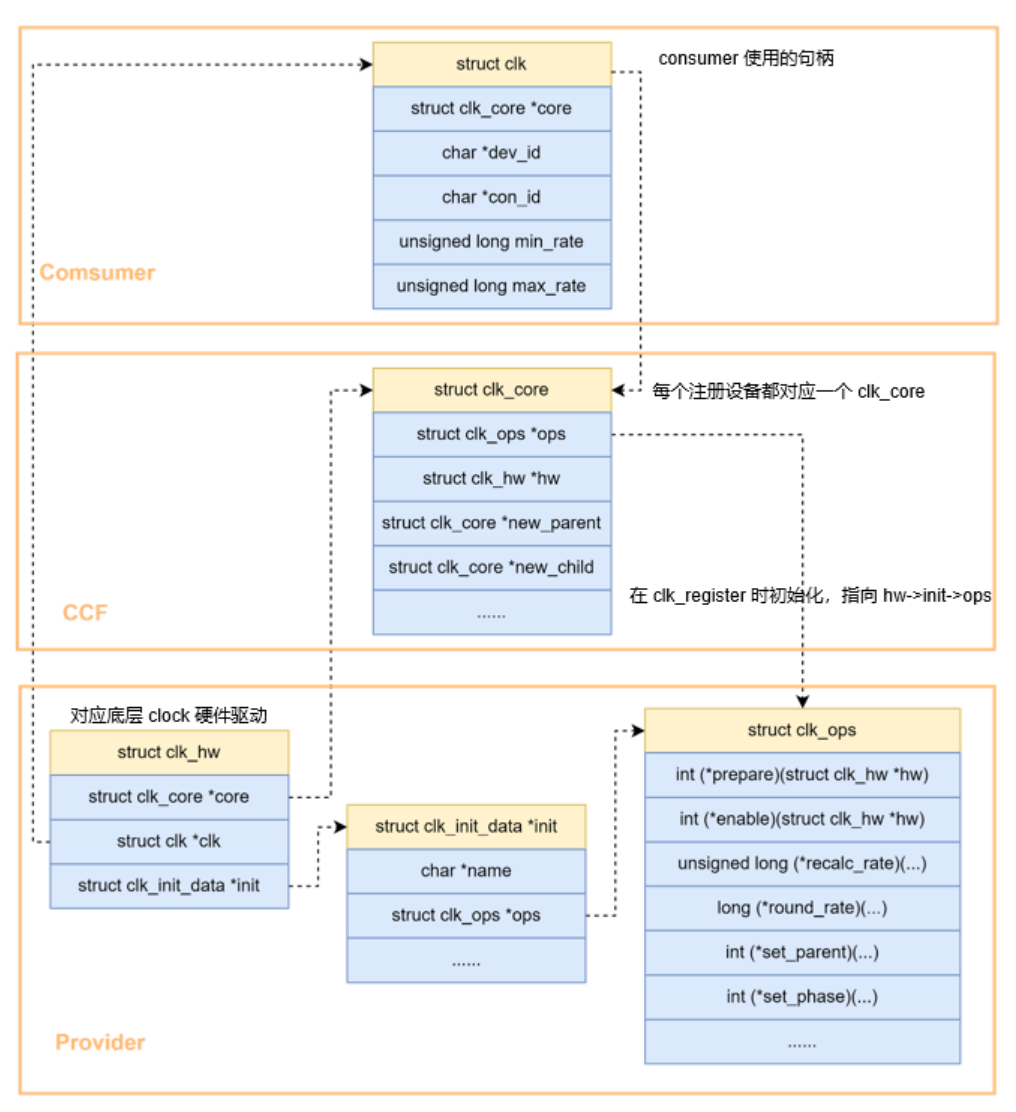

Linux clock子系统及驱动实例

in-cell panel_In-Cell触摸屏原理

分析clock tree的小工具——CCOPT Clock Tree Debugger(一)

低功耗设计之multi-bit cell技术简介

ASIC的clock gating在FPGA里面实现是什么结果呢?

RTL实例化的clock gating cell浅见

RTL实例化的clock gating cell浅见

评论