在你们的工作中都遇到过哪些bug呢?下面这些你见过没?

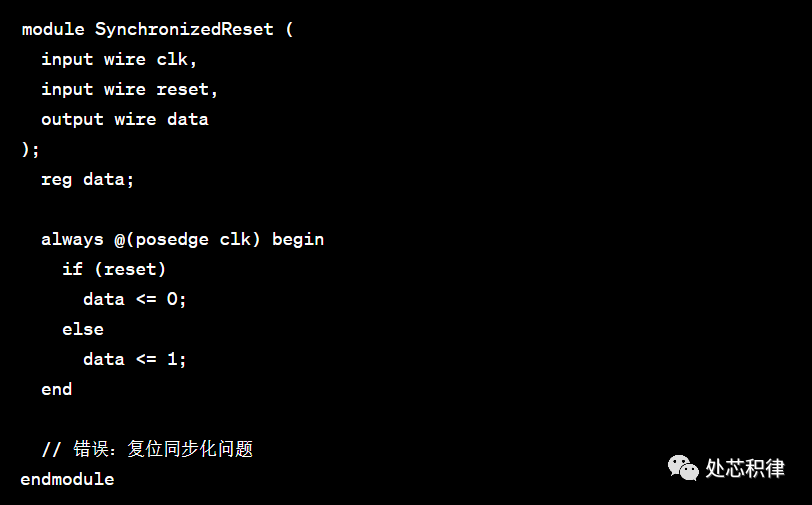

1.复位同步化问题

错误的地方:在时钟上升沿处处理复位信号,但未同步复位信号到时钟域,可能导致复位信号的抖动或同步问题。

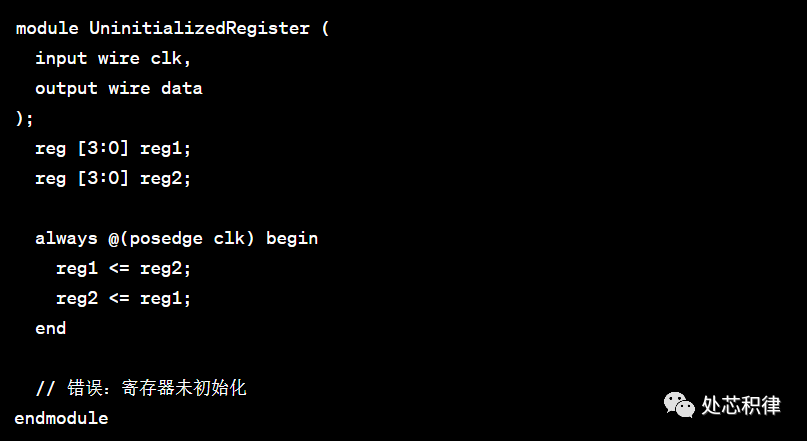

2.未初始化的寄存器的问题

错误的地方:未对寄存器 reg1 和 reg2 进行初始化,初始值未定义,可能导致未知的行为和仿真结果。

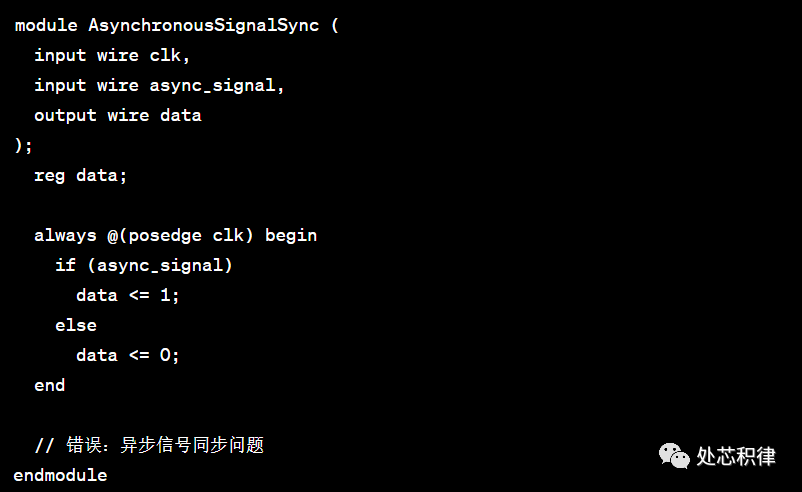

3. 异步信号同步问题

错误的地方:直接将异步信号 async_signal 用于时钟边沿触发的逻辑中,没有进行同步处理,可能导致元数据冲突和时序问题。

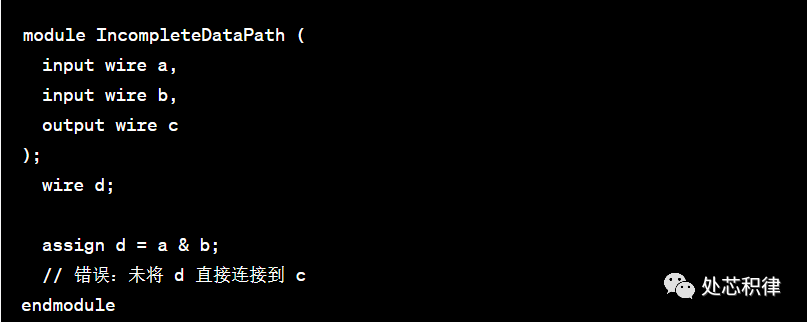

4. 不完整的数据路径

错误的地方:在数据路径中,信号 d 通过与门的连接计算得出,但未将 d 直接连接到输出 c。这可能导致输出 c 未能正确反映数据路径的结果,导致逻辑错误或意外行为。

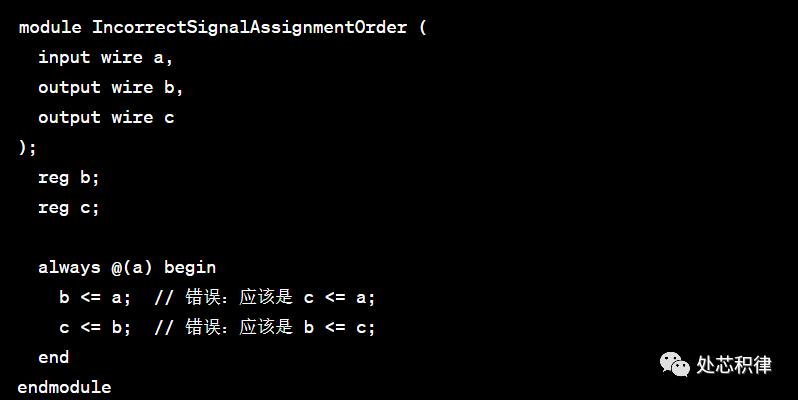

5. 不正确的信号赋值顺序

错误的地方:在信号赋值时,赋值顺序不正确,导致信号之间的依赖关系混乱,可能导致逻辑错误或不一致的行为。

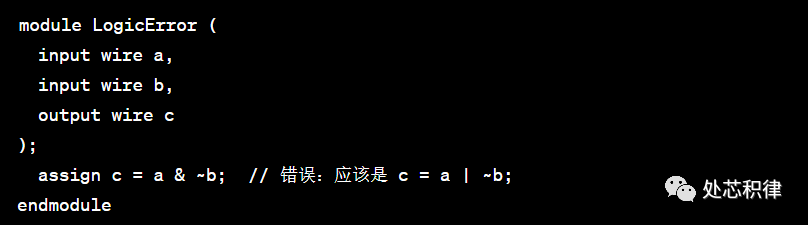

6.逻辑错误

错误的地方:在逻辑运算中,使用了错误的操作符,导致逻辑功能与预期不符。

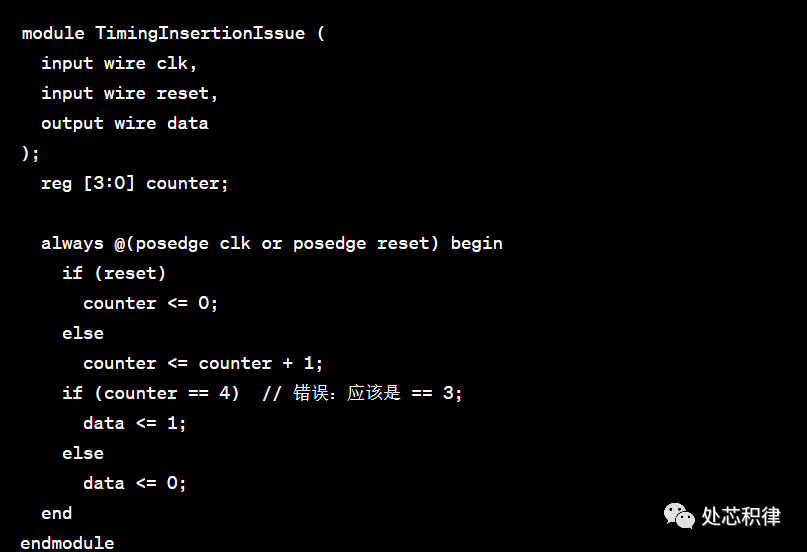

6. 时序插入问题

错误的地方:在时序逻辑中,对计数器值进行判断时,条件错误地设置为 counter == 4,而实际上应该是 counter == 3。这会导致时序行为出现问题。

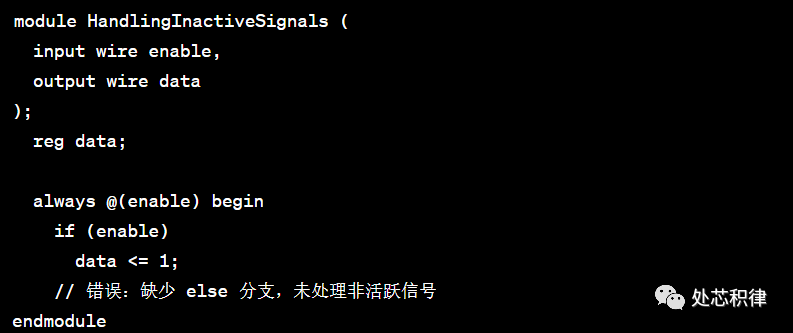

7.非活跃信号处理

错误的地方:在处理信号时,缺少 else 分支,未能正确处理信号非活跃的情况,可能导致逻辑错误。

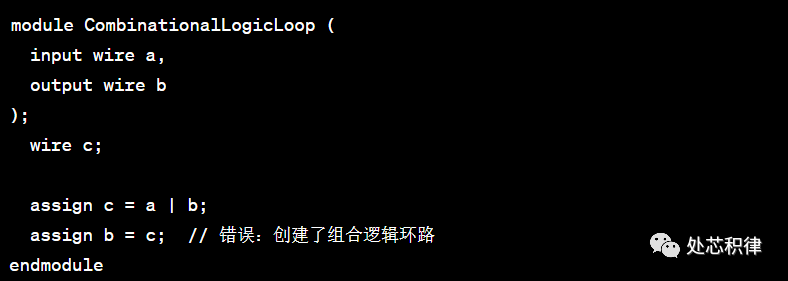

8.组合逻辑环路

错误的地方:在连续赋值语句中,创建了组合逻辑环路,其中信号 b 依赖于信号 c,而信号 c 又依赖于信号 b,这会导致综合和仿真时的不确定行为。

还有哪些RTL中常见的bug,欢迎大家留言讨论。

-

寄存器

+关注

关注

31文章

5363浏览量

121096 -

仿真

+关注

关注

50文章

4124浏览量

133950 -

时钟

+关注

关注

11文章

1746浏览量

131775 -

RTL

+关注

关注

1文章

385浏览量

59937 -

复位信号

+关注

关注

0文章

54浏览量

6365

原文标题:ICer,这5种bug你是不是经常遇到?

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

常见的PLC系统BUG有哪些?如何减少这些BUG的产生?

常见的PLC系统BUG有哪些?如何减少BUG的产生呢?

浅谈制糖企业能源计量中常见问题探讨

浅谈制糖企业能源计量中常见的问题探讨

浅谈RTL中常见的bug

浅谈RTL中常见的bug

评论