本内容由Lal_Han(http://chengone.cn)补充,辅助进行FPGA开发

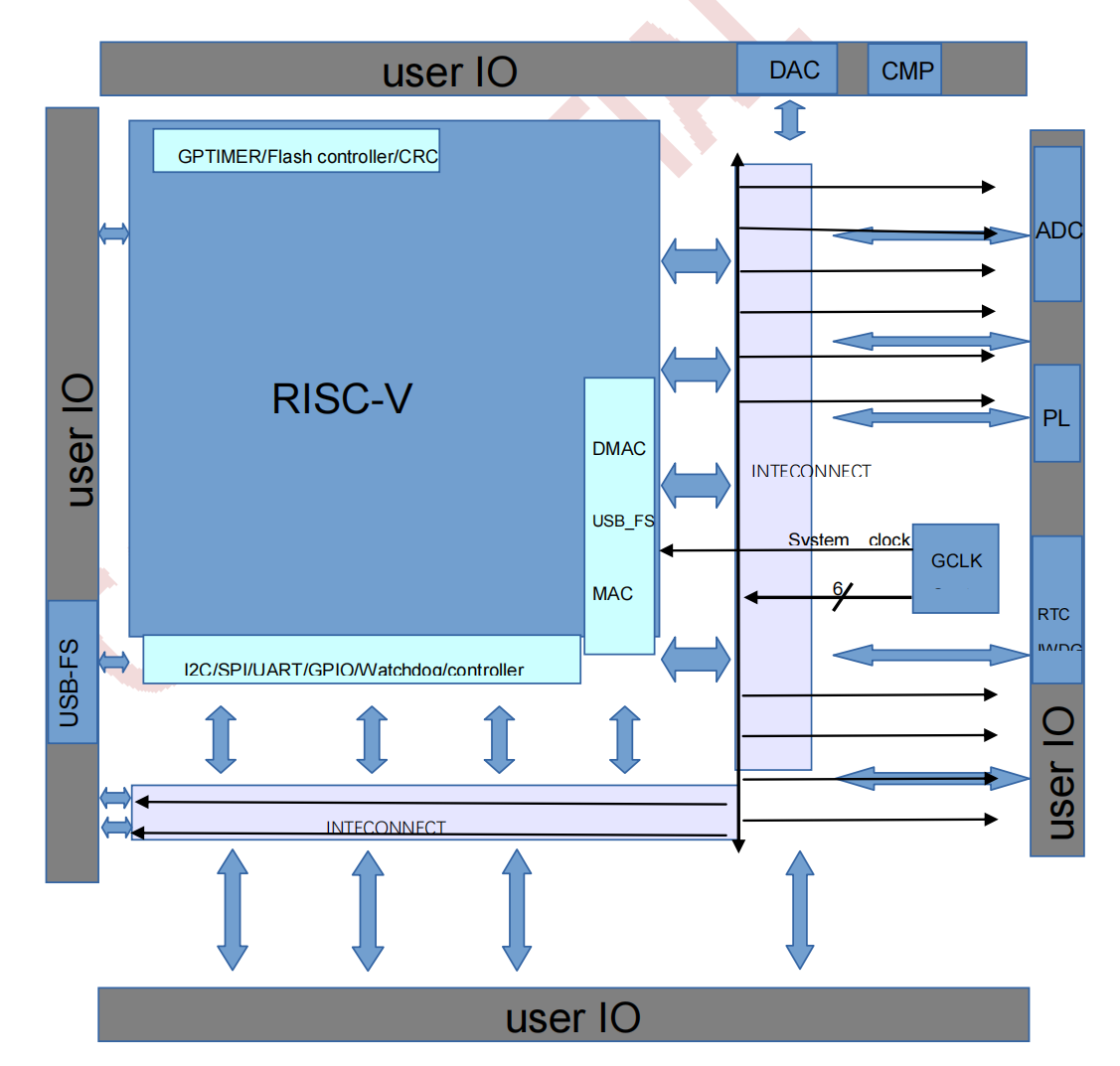

一、AG32VF407介绍

- 主频248MHz MCU+2K LEs(FPGA)[实测可以跑到384MHz]

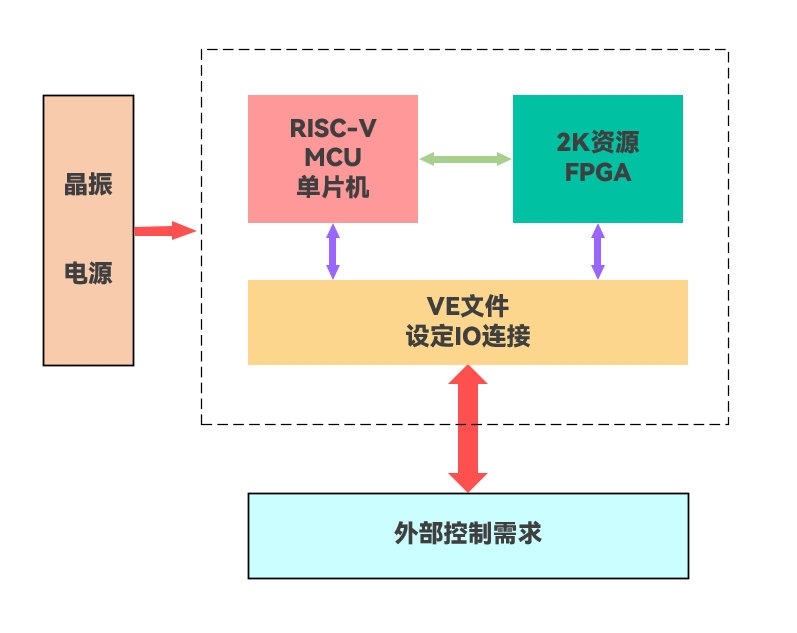

- 采用合封FPGA+RISC-V内核的方式

- FPGA和RISC-V引脚和单独指定

- 单片机所有引脚可随意指定

- 自带2K的FPGA

- MCU部分使用VScode搭建开发环境,FPGA使用Quartus开发

二、内核说明

核心优势(自认为):

单片机引脚自定义

内置FPGA

主频和内存比较高

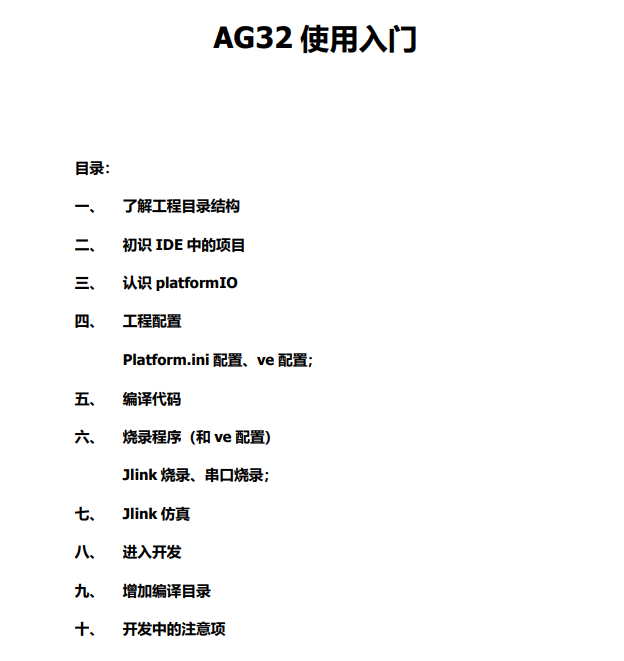

三、开发环境搭建

AGM32 软件链接: https://pan.baidu.com/s/17bp-zAnsYRuVMRTSSVHN5A 提取码: 12ej

(1)vscode

1687221901394686.pdf (eeworld.com.cn)

参考上面链接,注意事项:

一定要按流程!一定要按流程!一定要按流程!

先安装vscode,再安装pytyhon(一定是3.10以上)

(2)Quartus

这里引用了CSDN中的文章

四、MCU+FPGA开发过程

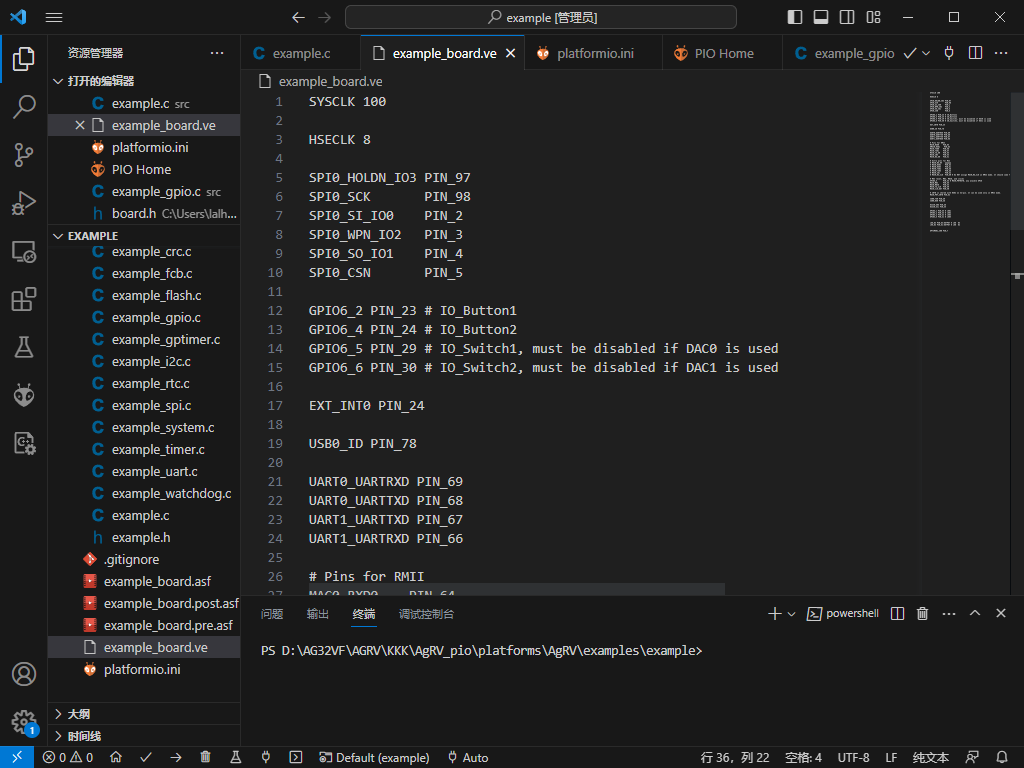

(1)编写VE文件

VE文件是必须要首先确定的,代表FPGA和MCU对外引脚连接,必须要进行绑定才可以进行交互(类比esp32的引脚任意定制和FPGA的分配引脚的步骤)

1、MCU的类型定义

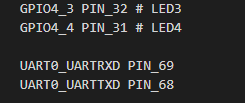

比如,定义gpio到外部引脚:GPIO4_3 PIN_32

比如,定义串口0到外部引脚:UART0_UARTRXD PIN_31

定义格式为:前边为mcu的FunctionName,后边是PIN脚ID。

2、FPGA与外部引脚

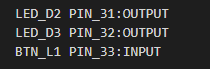

比如,定义led到外部引脚:LED_D3 PIN_32:OUTPUT

cpld信号名称,是自定义名称,随后在cpld中自行引用;

方向:有3种:OUTPUT、INPUT和INOUT(FPGA开发)

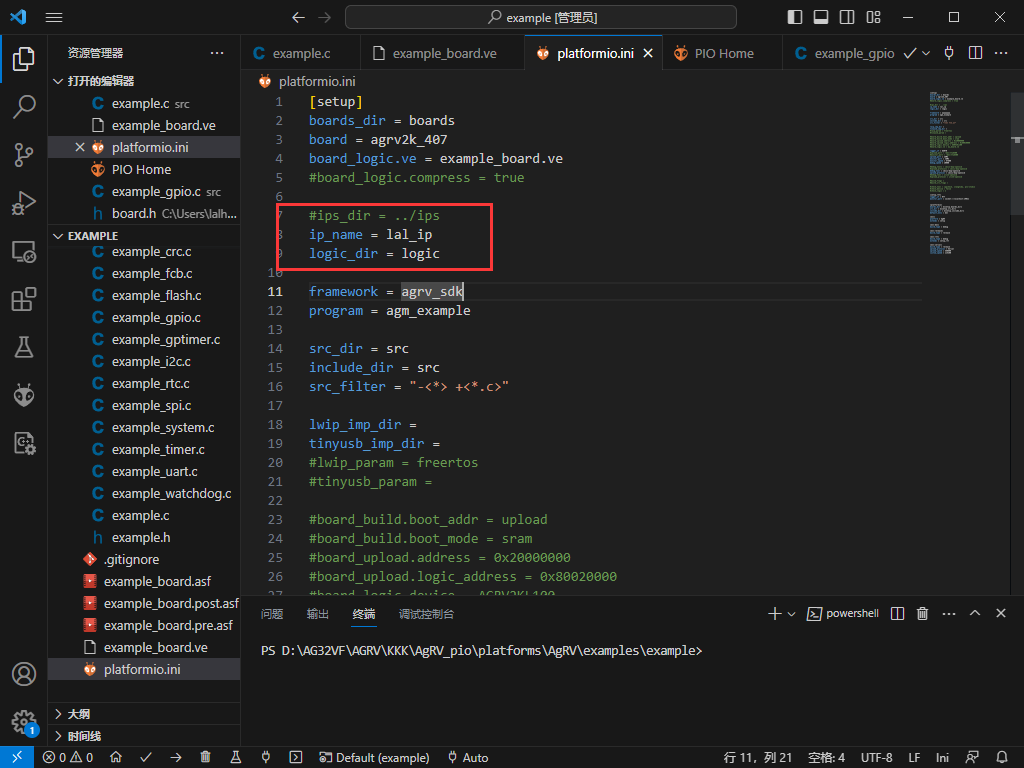

(2)修改INI文件,生成logic

这里取消注释。ip_name代表生成的V文件名称,而dir代表是目录名称,可改可不改

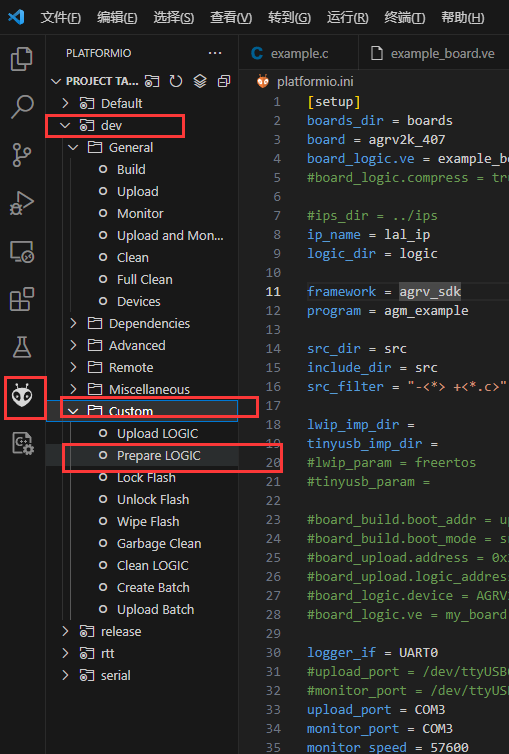

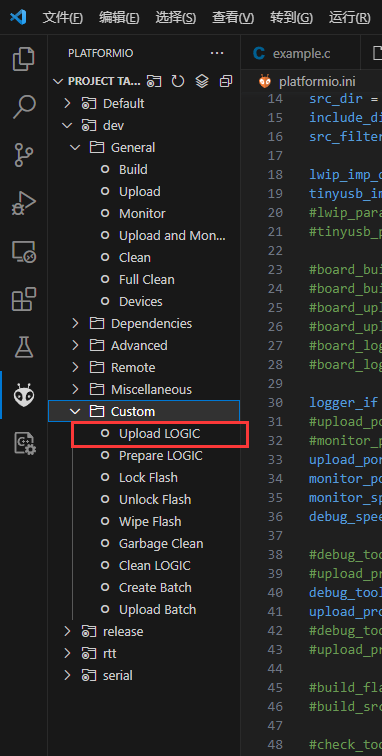

点击Platform

选择dev

选择custom

Prepare(生成logic文件即FPGA文件)

(3)修改、编译FPGA程序

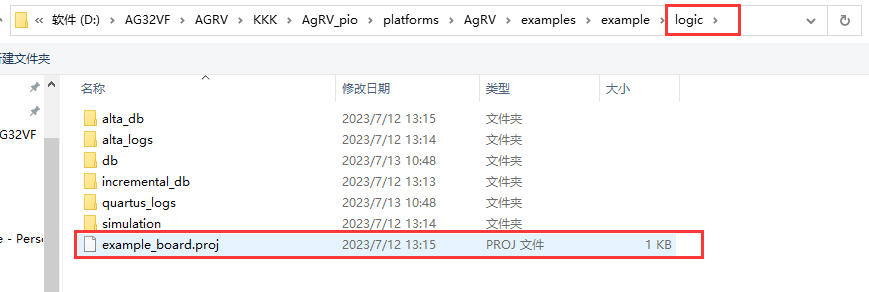

1、打开FPGA程序

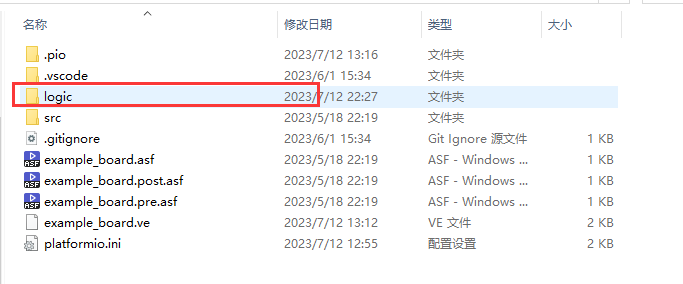

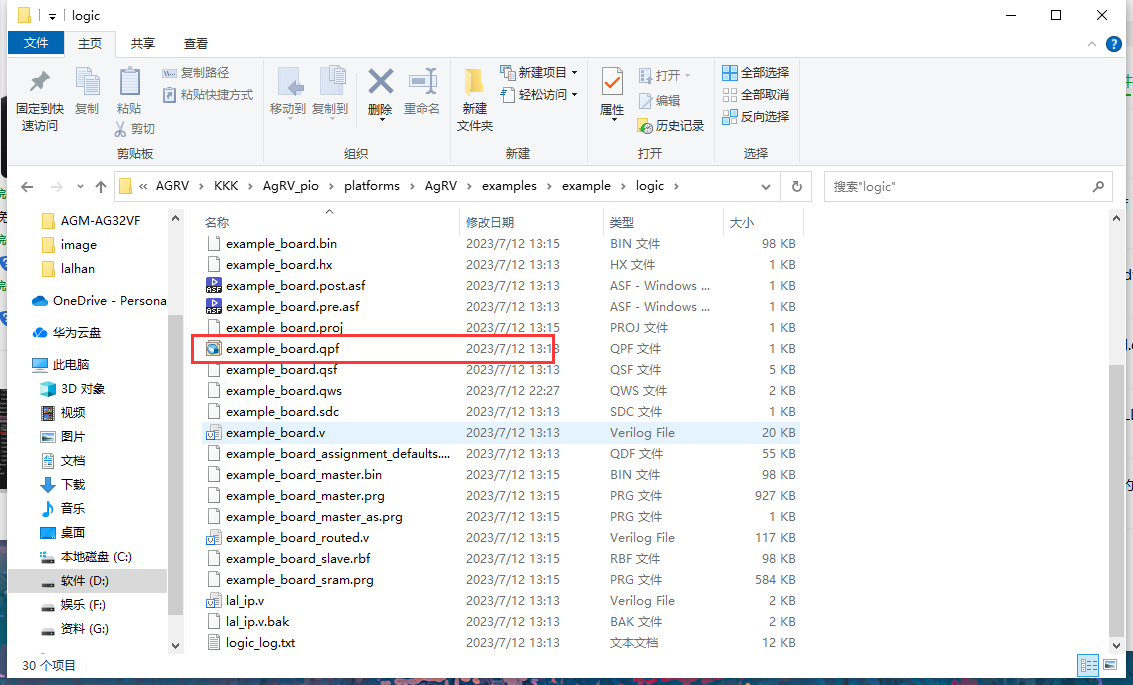

此时在当前目录下生成了logic目录

点击qpf文件进入FPGA环境

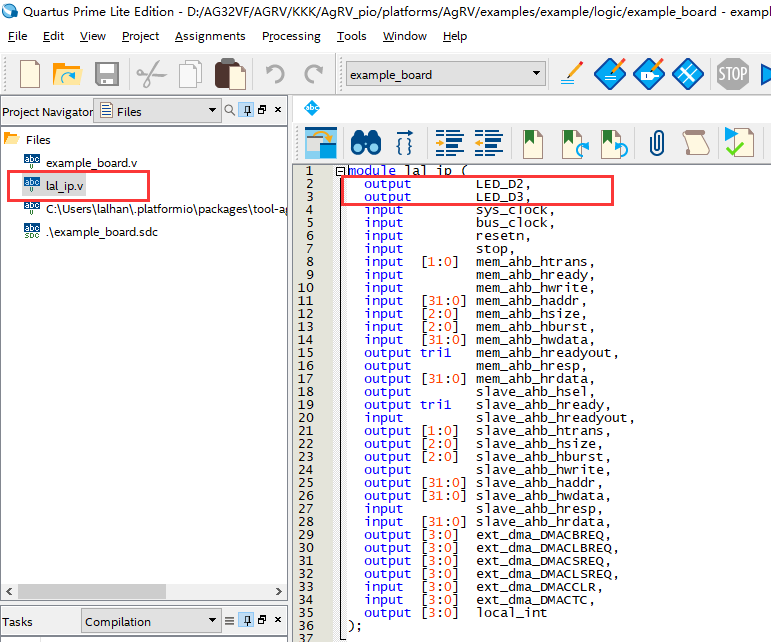

2、修改程序

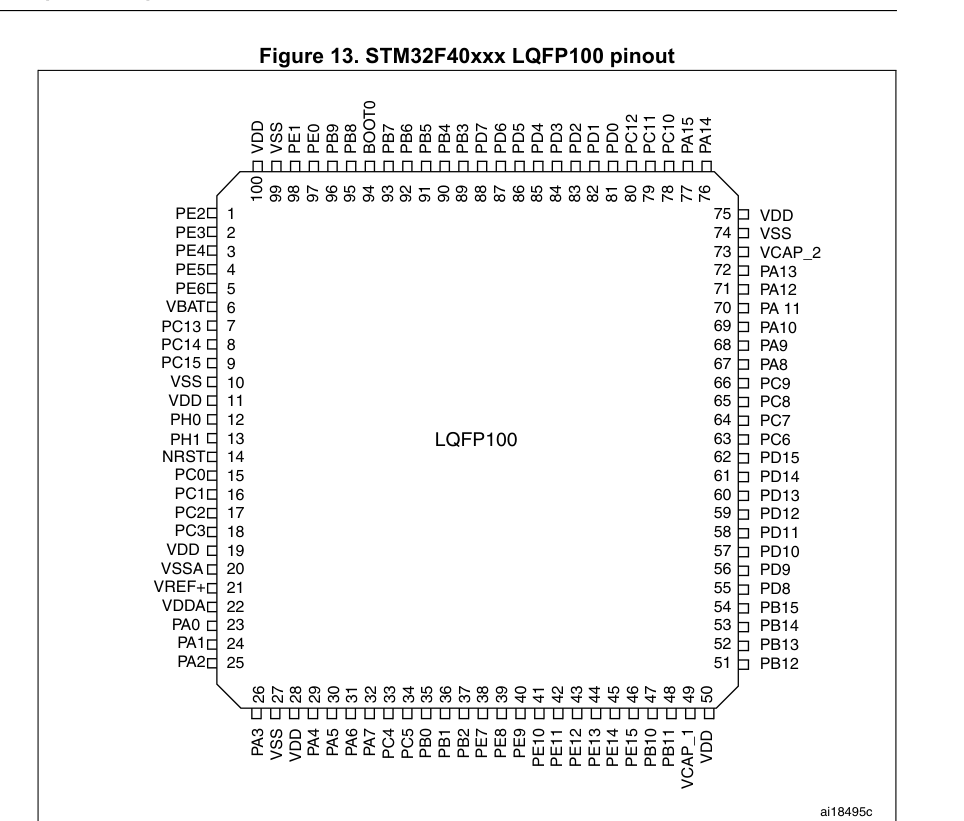

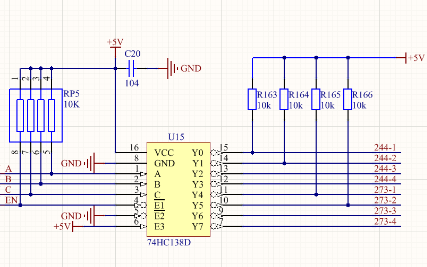

此时选择你自己的FPGA程序(其它的不建议修改,请不要修改),此时在VE文件中定义的LED_D2和LED_D3已经出现在top文件了,且方向为OUTPUT,该两个引脚为VE文件中设定的引脚,方便理解。我这里放置一个对照图,里面的数字就是PIN几,对应STM32F4的外部引脚

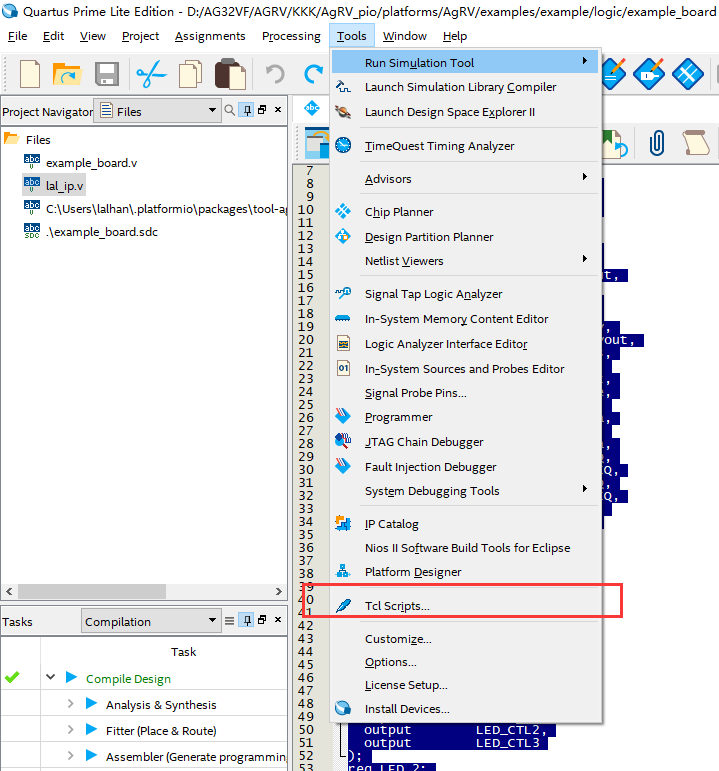

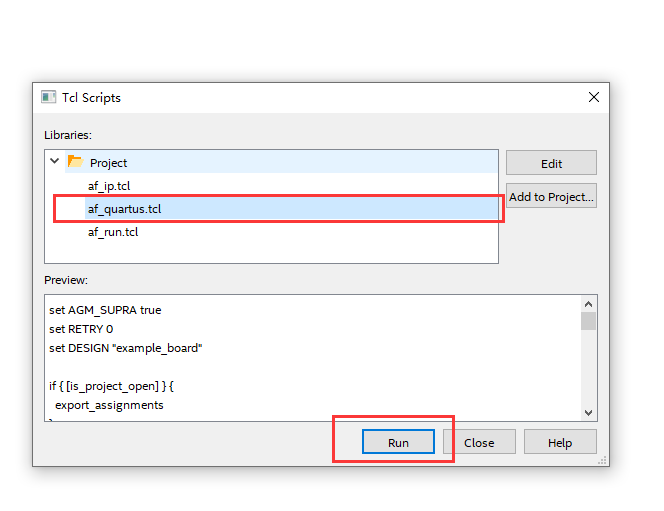

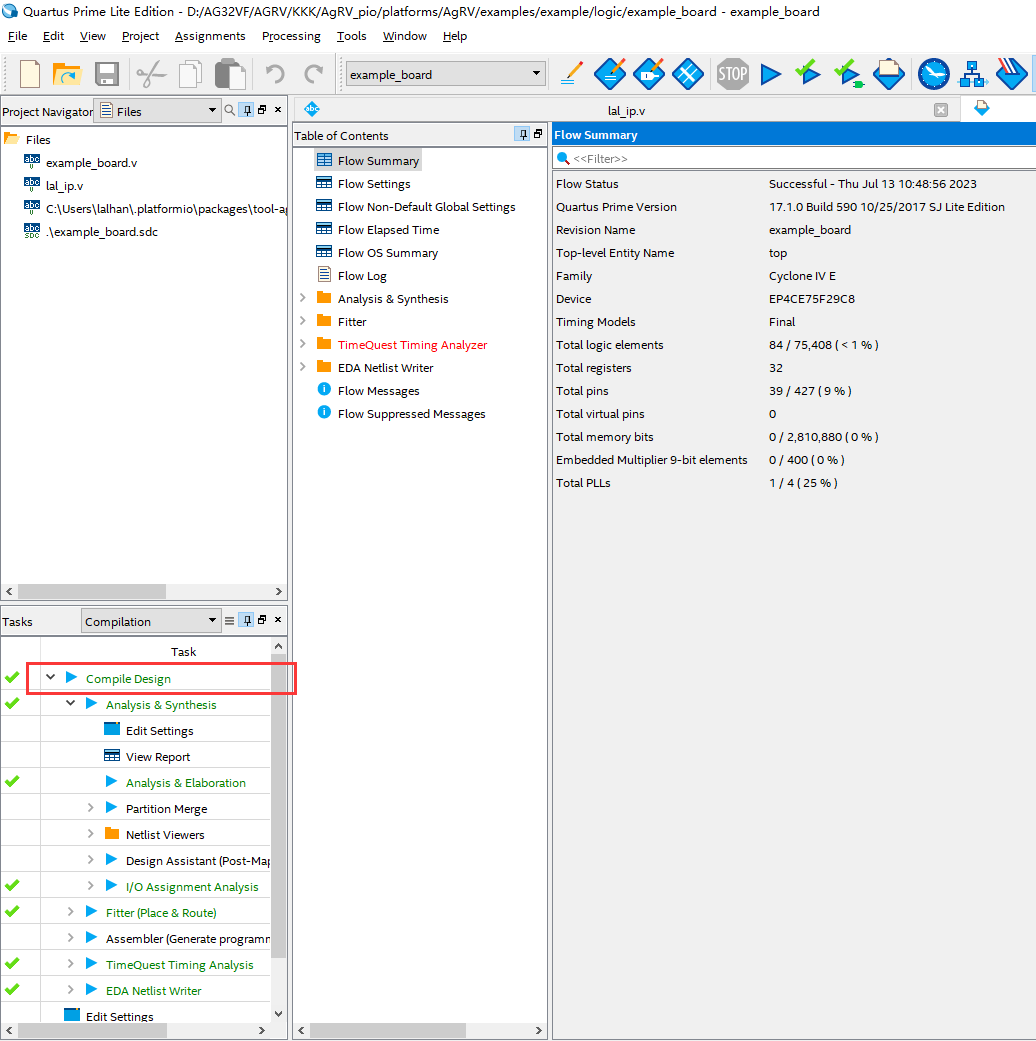

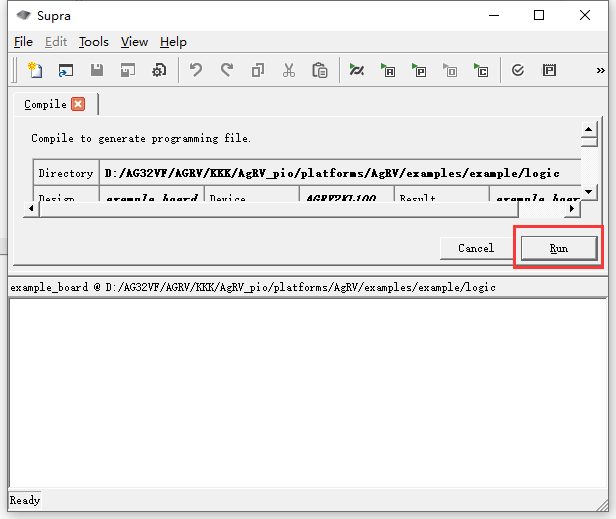

3、编译和导出

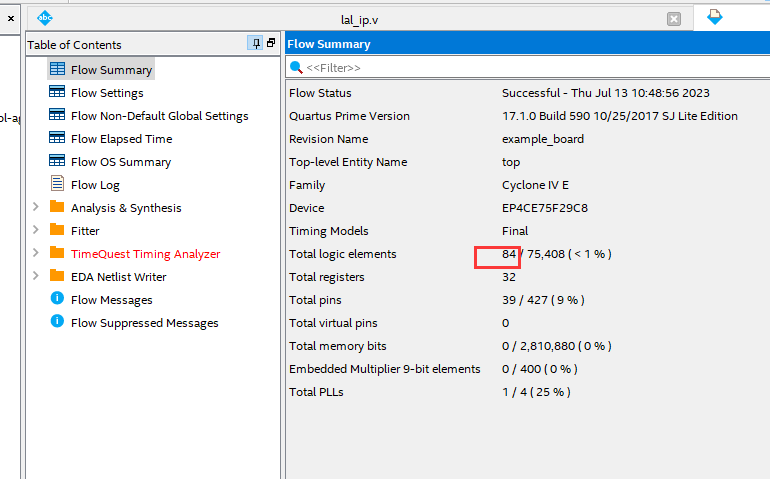

运行后得到使用的逻辑单元

这个地方不要超过2000

或者双击Compile Ddsign也可以,建议第一次选择TCL

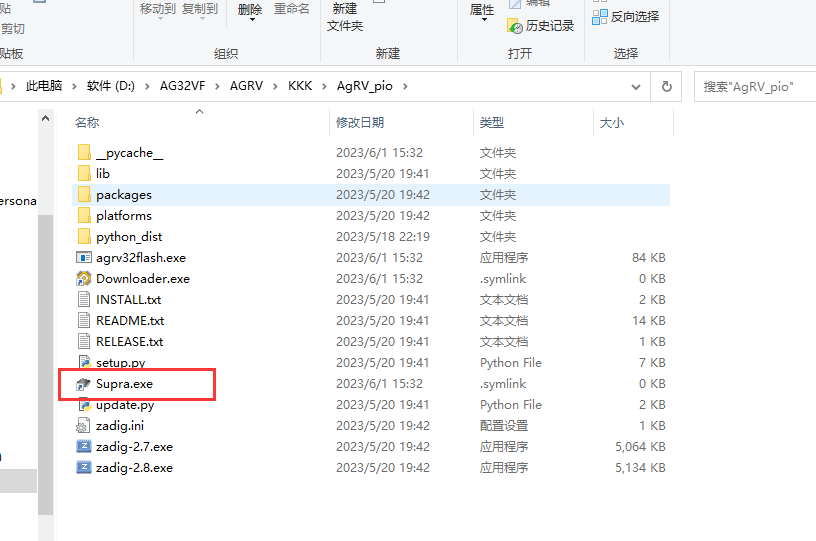

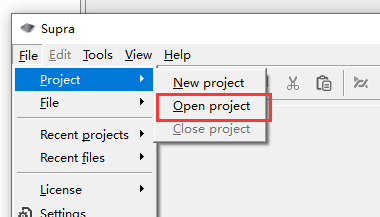

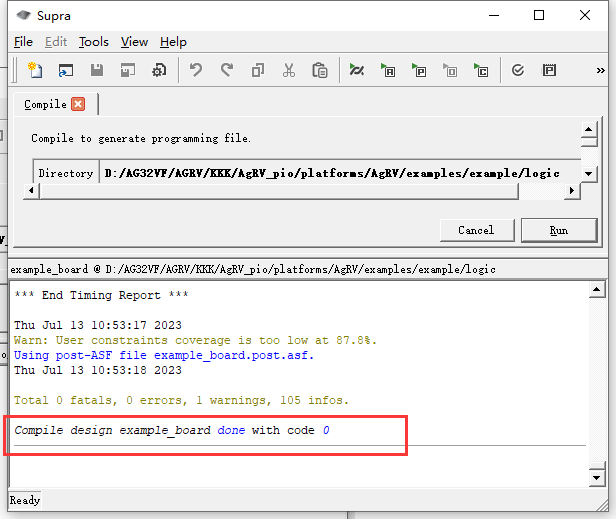

4、supra编译

该软件在安装的SDK根目录下

五、烧录程序

1、烧录VE

如果有改动需要烧录,没有改动不需要烧录

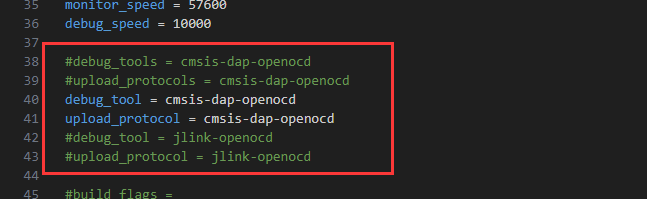

烧录器需要修改的话,在ini文件里修改,选择性取消注释即可,连接单片机的PA13/PA14引脚,即PIN72/PIN76

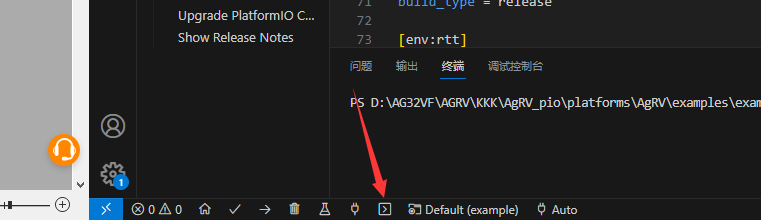

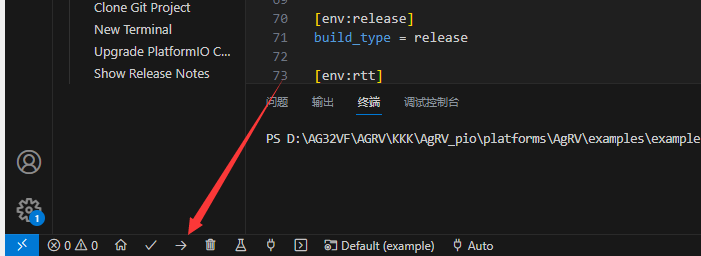

在vscode中选择打开命令行

输入指令:

pio run -e serial -t logic

2、烧录程序

审核编辑:汤梓红

-

FPGA

+关注

关注

1629文章

21742浏览量

603534 -

mcu

+关注

关注

146文章

17152浏览量

351258 -

RISC

+关注

关注

6文章

462浏览量

83737 -

环境搭建

+关注

关注

0文章

53浏览量

9057

发布评论请先 登录

相关推荐

【新品体验】AG32开发板免费试用

浅谈国产异构双核RISC-V+FPGA处理器AG32VF407的优势和应用场景

【AG32开发板体验连载】AG32VF407启动与探究

【AG32开发板体验连载】AG32VF407中开发流程学习

AG32开发板使用的几点心得体会

【AG32开发板体验连载】智能蒸烤箱--AG32VF407I2C总线测试

【AG32开发板体验连载】AG32VF407 UART串口通信测试

DEMO Android4.4.2环境搭建

AG32VF407RGT6 PINtoPIN STMcu、GDMcu,引脚亦可转换位置灵活重新定义

AG32VF407VGT6 PINtoPIN STMcu、GDMcu,引脚亦可转换位置灵活重新定义

AGM官方AG32 MCU开发板

AG32VF407环境搭建(FPGA+RISCV)

AG32VF407环境搭建(FPGA+RISCV)

评论