在过去的五年里,处理器已经从单个硅片变成了一组较小的小芯片,这些小芯片共同作用就像一个大芯片一样。这种方法意味着 CPU 的功能部件可以使用最适合每个部件的技术来构建。AMD的产品技术架构师Sam Naffziger是这种方法的早期支持者。Naffziger 最近回答了IEEE Spectrum就该主题提出的五个小芯片大小的问题。

问:您认为基于小芯片的处理器面临哪些主要挑战?

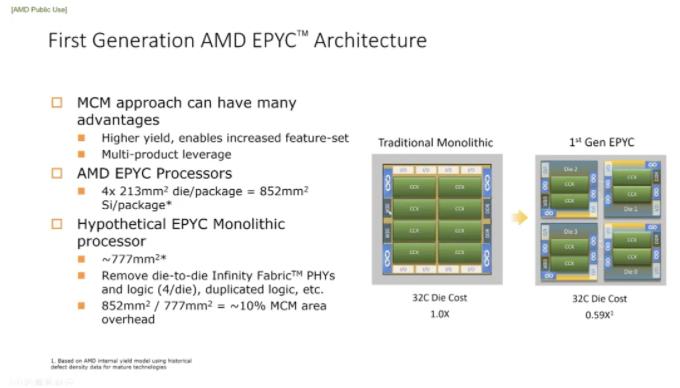

Sam Naffziger:我们五六年前开始推出EPYC和Ryzen CPU 系列。当时,我们撒了一张相当广泛的网来寻找最适合连接芯片(小硅块)的封装技术。这是一个由成本、性能、带宽密度、功耗以及制造能力组成的复杂方程式。提出出色的封装技术相对容易,但实际大批量、经济高效地制造它们却是完全不同的事情。所以我们在这方面投入了大量资金。

问:小芯片将如何改变半导体制造工艺?

Naffziger:这绝对是该行业正在努力解决的问题。这就是我们今天所处的位置,也是我们 5 到 10 年后可能达到的位置。我认为今天的技术基本上都是通用的。它们可以很好地与单片芯片对齐,也可以用于小芯片。有了小芯片,我们就拥有了更专业的知识产权。因此,未来人们可以设想专业化的工艺技术并获得性能优势、成本降低等。但这并不是当今行业的现状。

问:小芯片将如何影响软件?

Naffziger:我们架构的目标之一是让它对软件完全透明,因为软件很难改变。例如,我们的第二代 EPYC CPU 由被计算芯片包围的集中式 I/O [输入/输出] 小芯片组成。当我们采用集中式 I/O 芯片时,它减少了内存延迟,消除了第一代的软件挑战。

现在,借助 [ AMD Instinct] MI300(AMD 即将推出的高性能计算加速器),我们正在集成 CPU 和 GPU 计算芯片。这种集成的软件含义是它们可以共享一个内存地址空间。因为软件不必担心管理内存,所以编程更容易。

问:有多少架构可以分离到小芯片上?

Naffziger:我们正在寻找扩展逻辑的方法,但 SRAM 更具挑战性,而模拟的东西绝对无法扩展。我们已经采取了将模拟与中央 I/O 小芯片分离的步骤。借助3D V-Cache(一种与计算芯片 3D 集成的高密度缓存小芯片),我们分离出了 SRAM。我预计未来会有更多此类专业化。物理学将决定我们可以做到多细粒度,但我对此持乐观态度。

问:怎样才能将不同公司的小芯片混合并匹配到同一个封装中才能成为现实?

Naffziger:首先,我们需要一个关于接口的行业标准。UCIe是 2022 年推出的小芯片互连标准,是重要的第一步。我认为我们将看到这种模式的逐步发展,因为它对于提供更高水平的每瓦性能和每美元性能至关重要。然后,您将能够组装一个针对特定市场或客户的片上系统。

-

处理器

+关注

关注

68文章

19222浏览量

229520 -

amd

+关注

关注

25文章

5460浏览量

134031 -

chiplet

+关注

关注

6文章

426浏览量

12573

原文标题:关于Chiplet,AMD的5个经验分享

文章出处:【微信号:AI_Architect,微信公众号:智能计算芯世界】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

发现基于Zen 5架构的AMD Threadripper “Shimada Peak” 96核和16核CPU

Chiplet技术有哪些优势

2035年Chiplet市场规模将超4110亿美元

IMEC组建汽车Chiplet联盟

AMD Versal自适应SoC CPM5 QDMA的Tandem PCIe启动流程介绍

突破与解耦:Chiplet技术让AMD实现高性能计算与服务器领域复兴

西门子EDA创新解决方案确保Chiplet设计的成功应用

AMD采用Chiplet架构,每年减排数万吨温室气体

AMD Chiplet小芯片架构年减排数万吨温室气体

Chiplet是否也走上了集成竞赛的道路?

什么是Chiplet技术?

Chiplet技术对英特尔和台积电有哪些影响呢?

关于Chiplet,AMD的5个经验分享

关于Chiplet,AMD的5个经验分享

评论