前言

JTGA这个东西IC和嵌入式靓仔们肯定是有用过的,但是对于JTAG内部的东西,以及实现如果不了解的,可以看看这篇文章。

之前和coresight有了解过的靓仔,了解了对于ARM内部的调试,知道了对于调试的入口在于那个JTAG Port,但是对于外部的JTGA Port你真的又了解多少,是否真的就是那么简单的一个port?

不知道coresight的可以看看【来跟着前辈看看coresight】这篇文章。

为什么要了解这个东西,是因为最近在调试这个JTAG,还要用到一些脚本,对于这些指令很是好奇,于是就来看看这些指令是怎么在JTAG内部工作,下面废话不多说开始吧。

[PS:感谢文末前辈们的优秀博客作为参考,以及优秀的开源文档]

1-JTAG的概述

1-什么是JTAG

•JTAG:Joint Test Action Group“(联合测试工作组) 的英文缩写

•边界扫描要求符合IEEE1149.1 (JTAG) 标准

•BSDL(Boundary- ScanDescriptionLanguage)边界扫描描述语言

•边界扫描测试 (Boundary-Scan-TEST):对符合IEEE1149.1标准的器件,通过BSDL文件生成测试向量, 测试器件开路短路的一种测试方法

边界扫描(Boundary Scan)测试发展于上个世纪90年代,随着大规模集成电路的出现,印制电路板制造工艺向小,微,薄发展,传统的ICT 测试已经没有办法满足这类产品的测试要求。由于芯片的引脚多,元器件体积小,板的密度特别大,根本没有办法进行下探针测试。一种新的测试技术产生了,联合测试行为组织(Joint Test Action Group)简称JTAG 定义这种新的测试方法即边界扫描测试。

随着表面贴装技术的使用,印制电路板(PCB)的密度越来越高,已不易采用传统的针床测试技术。而增加电路测试点、对复杂电路增加附加的测试电路来进行单独测试等方法只是对传统方法的改进,对提高电路可测性十分有限且通用性较差。

为提高电路和系统的可测试性,1985年菲利浦电子公司首先倡议并联合欧洲、北美和亚洲其他电子设备制造公司组建了联合测试行动组(Jo int TestA ction Group,JTAG)。1990年2月JTAG与TEEE标准化委员会合作提出了“标准测试访问通道与边界扫描结构”的IEEE114911 1990标准。该标准要求在集成电路中加入边界扫描电路。

在板级测试时,可以在模式选择的控制下,构成一条就集成电路边界绕行的移位寄存器链,对板内集成电路的所有引脚进行扫描,通过将测试数据串行输入到该寄存器链的方法,检查发现印刷电路板上的器件焊接故障和板内连接故障,极大地方便了系统电路的调试。IEEE114911标准的推广应用引起测试设备和测试系统的重大变革,边界扫描测试技术正日益成为超大规模集成电路的主流测试技术。

2-使用JTAG的好处

•缩短产品面世时间

•降低测试成本

•提高产品质量和可靠性

•降低PCB成本

小结

边界扫描测试有2大优点:

•一个是方便芯片的故障定位,迅速准确地测试两个芯片管脚的连接是否可靠,提高测试检验效率;

•另一个是,具有JTAG接口的芯片,内置一些预先定义好的功能模式,通过边界扫描通道使芯片处于某个特定的功能模式,以提高系统控制的灵活性和方便系统设计。

2-边界扫描器件的结构

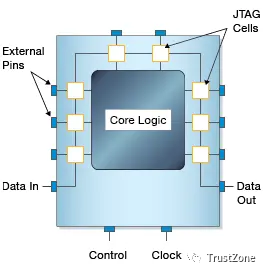

在这里插入图片描述

JTAG旨在解决使用传统的ICT方法测试电路的困难。

现代封装技术(如BGA和芯片级封装)限制了并在某些情况下消除了对引脚的物理访问。

JTAG通过在器件的外部连接和内部逻辑之间放置单元(边界扫描单元)来克服这个问题,如上图。通过将单元配置为移位寄存器,JTAG可用于监视/控制这些引脚(以及连接到它们的网络)的值,而无需直接物理访问。极大减少了对板卡的物理访问。

在器件的正常工作期间,还可以选择对芯片和引脚之间传递时的数据值进行采样,实时观察芯片引脚的状态。

这个寄存器中的每个单元都位于设备的边界上,位于它的核心逻辑和与板卡相连的针脚之间——所以JTAG测试也被称为边界扫描。

对于要符合JTAG标准的设备,其制造商必须提供BSDL文件(边界扫描描述语言),该文件描述了设备的JTAG方面如何工作。

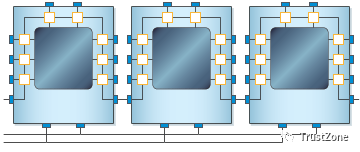

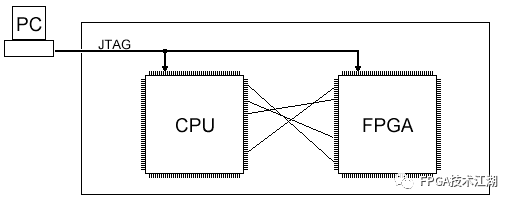

如果电路包含多个JTAG兼容器件,则可以将这些器件链接在一起以形成JTAG链。

在JTAG链中,来自第一器件的数据输出成为第二器件的数据输入。

控制和时钟信号对于链中的所有设备都是通用的。以保证链中的设备在测试期间保持相同的状态。

在这里插入图片描述

如果此时你还不理解这个链路,没事继续看下午,非后续阻塞点。

0-边界扫描

在JTAG调试当中,边界扫描(Boundary-Scan)是一个很重要的概念。

边界扫描技术的基本思想是在靠近芯片的输入输出管脚上增加一个移位寄存器单元。因为这些移位寄存器单元都分布在芯片的边界上(周围),所以被称为边界扫描寄存器(Boundary-Scan Register Cell)。

当芯片处于调试状态的时候,这些边界扫描寄存器可以将芯片和外围的输入输出隔离开来。通过这些边界扫描寄存器单元,可以实现对芯片输入输出信号的观察和控制。

•对于芯片的输入管脚,可以通过与之相连的边界扫描寄存器单元把信号(数据)加载到该管脚中去;

•对于芯片的输出管脚,也可以通过与之相连的边界扫描寄存器“捕获”(CAPTURE)该管脚上的输出信号。

在正常的运行状态下,这些边界扫描寄存器对芯片来说是透明的,所以正常的运行不会受到任何影响。这样,边界扫描寄存器提供了一个便捷的方式用以观测和控制所需要调试的芯片。

另外,芯片输入输出管脚上的边界扫描(移位)寄存器单元可以相互连接起来,在芯片的周围形成一个边界扫描链(Boundary-Scan Chain)。一般的芯片都会提供几条独立的边界扫描链,用来实现完整的测试功能。边界扫描链可以串行的输入和输出,通过相应的时钟信号和控制信号,就可以方便的观察和控制处在调试状态下的芯片。

利用边界扫描链可以实现对芯片的输入输出进行观察和控制。

下一个问题是:如何来管理和使用这些边界扫描链?

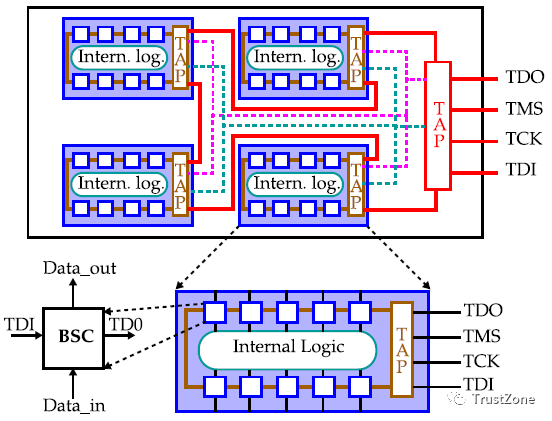

对边界扫描链的控制主要是通过TAP(Test Access Port) Controller来完成的。

在这里插入图片描述

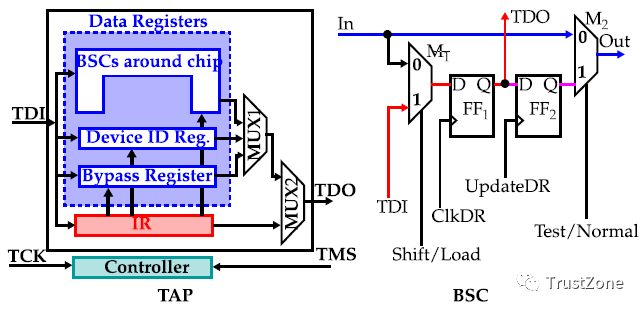

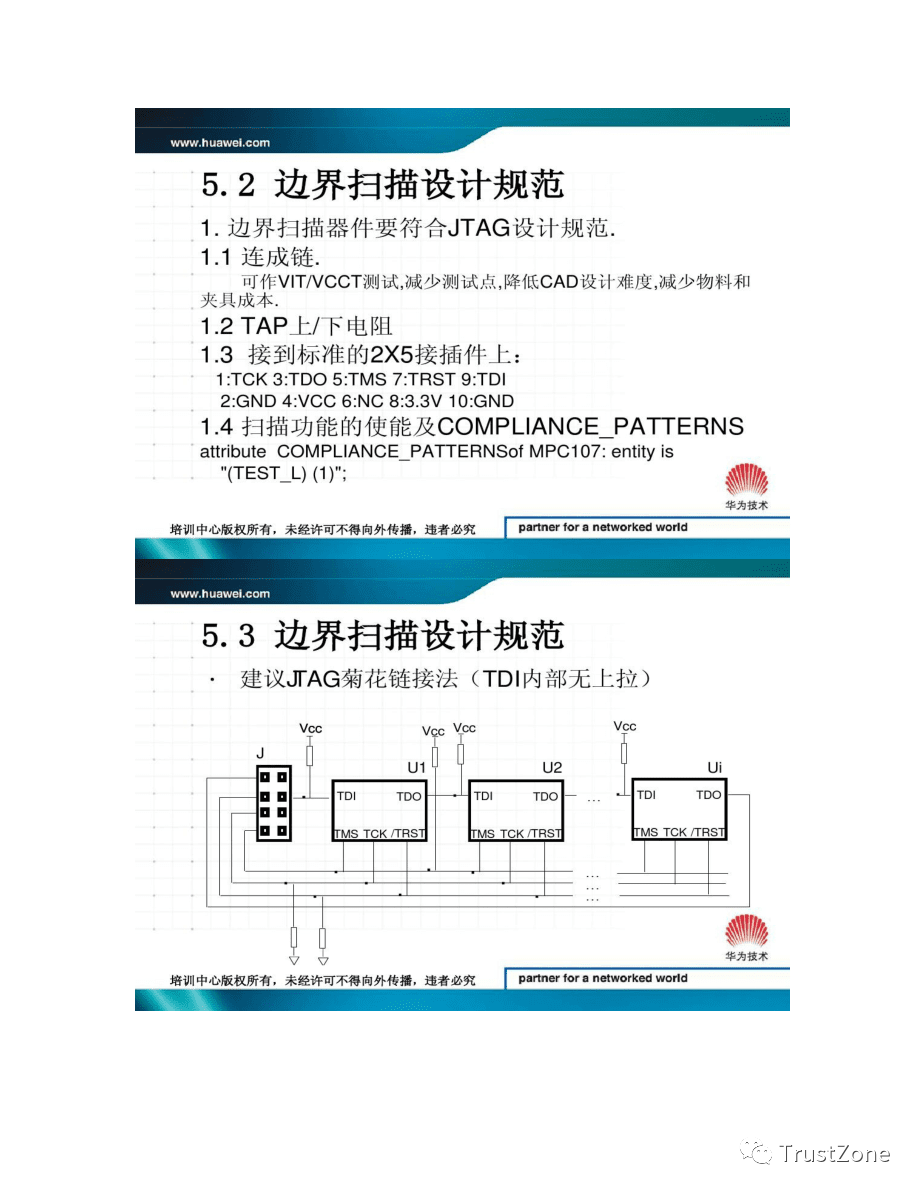

1-边界扫描的硬件结构

BST的核心思想是在芯片管脚和芯片内部逻辑之间,即紧挨元件的每个输入、输出引脚处增加移位寄存器组,在PCB的测试模式下,寄存器单元在相应的指令作用下,控制输出引脚的状态,读入输入引脚的状态,从而允许用户对PCB上的互连进行测试。

在这里插入图片描述

BST电路主要包括

•指令寄存器(IR)、

•旁路寄存器(BR)、

•边界扫描寄存器(BSR)

•测试访问端口(TAP)控制器。

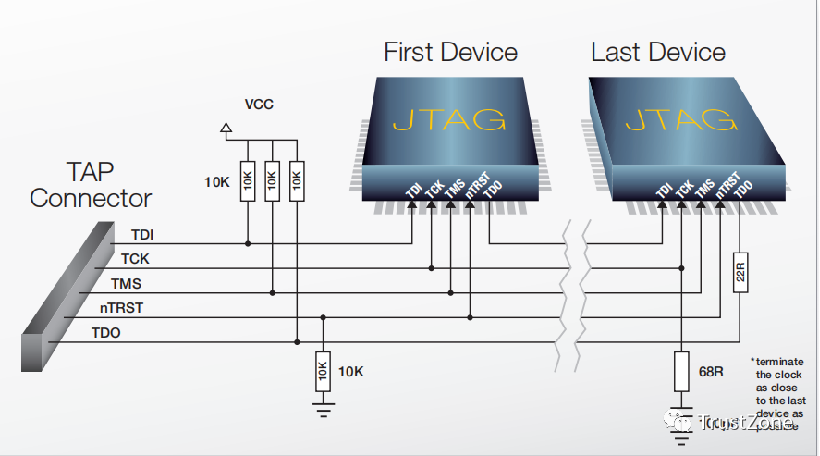

BST电路一般采用4线测试总线接口,如图1所示,如果测试信号中有复位信号(nTRST),则采用5线测试总线接口。

5个信号分别为:

•测试数据输入总线(TDI),测试数据输入至移位寄存器(SR);

•测试数据输出总线(TDO),测试数据从SR移出;

•测试时钟总线(TCK);

•测试模式选择总线(TMS),控制各个测试过程,如选择寄存器、加载数据、形成测试、移出结果等;

•复位信号总线(TRST),低电平有效。

IEEEStd114911测试总线使用TCK的2个时钟沿,

•TMS和TDI在TCK的上升沿被采样,

• TDO在TCK的下降沿变化。

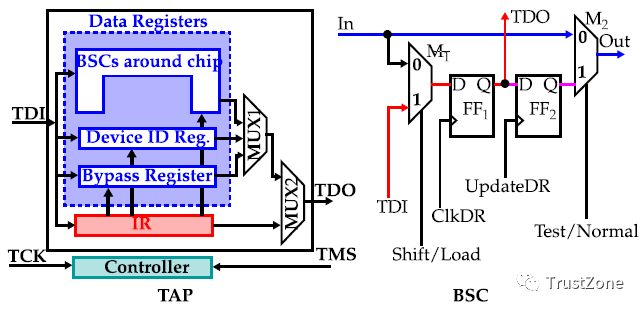

2-TAP(Test Access Port)

在上一节,我们已经简单介绍了边界扫描链,而且也了解了一般的芯片都会提供几条边界扫描链,用来实现完整的测试功能。下面,我将逐步介绍如何实现扫描链的控制和访问。

在IEEE 1149.1标准里面,寄存器被分为两大类:

•数据寄存器(DR-Data Register)

•指令寄存器(IR-Instruction Register)

边界扫描链属于数据寄存器中很重要的一种。

•边界扫描链用来实现对芯片的输入输出的观察和控制。

•而指令寄存器用来实现对数据寄存器的控制,

例如:在芯片提供的所有边界扫描链中,选择一条指定的边界扫描链作为当前的目标扫描链,并作为访问对象。下面,让我们从TAP(Test Access Port)开始。

2.1 接口信号定义

TAP是一个通用的端口,通过TAP可以访问芯片提供的所有数据寄存器(DR)和指令寄存器(IR)。对整个TAP的控制是通过TAP Controller来完成的。TAP总共包括5个信号接口TCK、TMS、TDI、TDO和TRST :其中4个是输入信号接口和另外1个是输出信号接口。

一般,我们见到的开发板上都有一个JTAG接口,该JTAG接口的主要信号接口就是这5个。下面,先分别介绍这个5个接口信号及其作用。

• Test Clock Input (TCK) TCK为TAP的操作提供了一个独立的、基本的时钟信号,TAP的所有操作都是通过这个时钟信号来驱动的。TCK在IEEE 1149.1标准里是强制要求的。

• Test Mode Selection Input (TMS) TMS信号用来控制TAP状态机的转换。通过TMS信号,可以控制TAP在不同的状态间相互转换。TMS信号在TCK的上升沿有效。TMS在IEEE 1149.1标准里是强制要求的。

• Test Data Input (TDI) TDI是数据输入的接口。所有要输入到特定寄存器的数据都是通过TDI接口一位一位串行输入的(由TCK驱动)。TDI在IEEE 1149.1标准里是强制要求的。

• Test Data Output (TDO) TDO是数据输出的接口。所有要从特定的寄存器中输出的数据都是通过TDO接口一位一位串行输出的(由TCK驱动)。TDO在IEEE 1149.1标准里是强制要求的。

• Test Reset Input (TRST) TRST可以用来对TAP Controller进行复位(初始化)。不过这个信号接口在IEEE 1149.1标准里是可选的,并不是强制要求的。因为通过TMS也可以对TAP Controller进行复位(初始化)。

2.2 指令寄存器、公共指令以及数据寄存器

在IEEE 1149.1标准当中,规定了一些指令寄存器、公共指令和相关的一些数据寄存器。对于特定的芯片而言,芯片厂商都一般都会在IEEE 1149.1标准的基础上,扩充一些私有的指令和数据寄存器,以帮助在开发过程中进行进行方便的测试和调试。在这一部分,我将简单介绍IEEE 1149.1规定的一些常用的指令及其相关的寄存器。

1-指令寄存器:

指令寄存器允许特定的指令被装载到指令寄存器当中,用来选择需要执行的测试,或者选择需要访问的测试数据寄存器。每个支持JTAG调试的芯片必须包含一个指令寄存器。(IR)

2-BYPASS指令和Bypass寄存器:

Bypass寄存器是一个一位的移位寄存器,通过BYPASS指令,可以将bypass寄存器连接到TDI和TDO之间。在不需要进行任何测试的时候,将bypass寄存器连接在TDI和TDO之间,在TDI和TDO之间提供一条长度最短的串行路径。这样允许测试数据可以快速的通过当前的芯片送到开发板上别的芯片上去。

3-IDCODE指令和Device Identification 寄存器:

Device identification寄存器中可以包括生产厂商的信息,部件号码,和器件的版本信息等。使用IDCODE指令,就可以通过TAP来确定器件的这些相关信息。例如,ARM MULTI-ICE可以自动识别当前调试的是什么片子,其实就是通过IDCODE指令访问Device Identification寄存器来获取的。

4-INTEST指令和Boundary-Scan 寄存器:

Boundary-Scan寄存器就是我们前面例子中说到的边界扫描链,一般一个芯片内部有多个边界扫描链。通过边界扫描链,可以进行部件间的连通性测试。当然,更重要的是可以对测试器件的输入输出进行观测和控制,以达到测试器件的内部逻辑的目的。

INTEST指令是在IEEE 1149.1标准里面定义的一条很重要的指令:结合边界扫描链,该指令允许对开发板上器件的系统逻辑进行内部测试。在ARM JTAG调试当中,这是一条频繁使用的测试指令。

我们前面说过,寄存器分为两大类:指令寄存器和数据寄存器。在上面提到的Bypass寄存器、Device Identification寄存器和Boundary-scan寄存器(边界扫描链),都属于数据寄存器。在调试当中,边界扫描寄存器(边界扫描链)最重要,使用的也最为频繁。

事实上,通过TAP接口,对数据寄存器(DR)进行访问的一般过程是:

•通过指令寄存器(IR),选定一个需要访问的数据寄存器(bypass,ID,Boundary-scan);

•把选定的数据寄存器连接到TDI和TDO之间;

•由TCK驱动,通过TDI,把需要的数据输入到选定的数据寄存器当中去;同时把选定的数据寄存器中的数据通过TDO读出来。

SIR->TDI->TDO

在这里插入图片描述

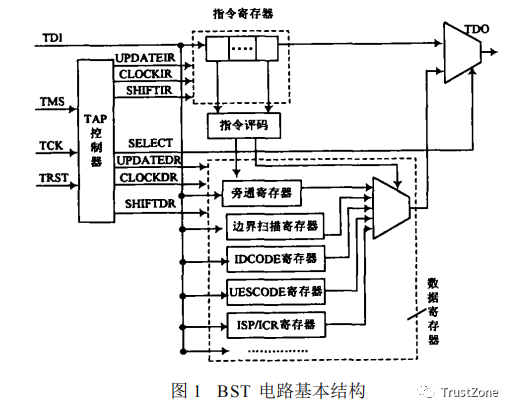

3-TAP 控制器

JTAG接口在每个设备上增加了四个额外的引脚:

TAP 接口必须包括: TCK, TMS, TDI, TDO

• TCK (Test ClockInput):测试时钟输入线

• TMS (Test Mode Selecton) :测试方式选择输入线

• TDI ( Test Data Input ) :测试数据输入线

• TDO ( Test Data Output ) :测试数据输出线

• TRST ( Test Reset Input ) :测试复位输入线,(可选)

在这里插入图片描述

TAP控制器是边界扫描测试的核心控制器。

在TCK和TMS的控制下,可以选择使用指令寄存器扫描或数据寄存器扫描,以及控制边界扫描测试的各个状态。

TMS和TDI是在TCK的上升沿被采样,TDO是在TCK的下降沿变化。

•TAP控制器是16-states的有限状态机

•TAP控制器的状态在TCK的上升沿变化

•TAP控制器在上电时进入逻辑复位状态

•Shift-IR state扫描IR,TDO输出有效

•Shift-DR state扫描DR,TDO输出有效

•其它状态下TDO输出无效

1-TAP控制器口线功能和关系1

•TCK为低时Test logic的存储单元保持不变,TCK在上升沿采样TMS和TDI输入值, 在TCK下降沿TDO输出变化

•测试指令(test instruction)和测试数据(test data)从TDI输入线输入到指令寄存器 ( instruction register ) 和 各种数据寄存器 ( various test data registers )

2-TAP控制器口线功能和关系2

•只有在移位时 ( Shift-DR or shift-IR ) TDO输出才有效

•测试操作受TMS输入的序列“1”和 0” 控制

•TRST可以异步复位

•当TMS在连续五个TCK时钟周期内保持高时,TAP控制器 ( TAP controllen)也会自动进入测试逻辑复位状态 ( Test-Logic-Reset)

4-TAP状态机

TAP控制器的状态机如图2所示。右边是指令寄存器分支,左边是数据寄存器分支。

在这里插入图片描述

其中,TAP控制器的状态机只有6个稳定状态:

•测试逻辑复位(Test Logical Reset)、

•测试运行等待(RunTest Idle)、

•数据寄存器移位(Shift DR)、

•数据寄存器移位暂停(Pause DR)、

•指令寄存器移位(Shift IR)、

•指令寄存器暂停(Pause IR)

其他状态都不是稳态,而只是暂态。

•在上电或IC正常运行时,必须使TMS最少持续5个TCK保持为高电平,则TAP进入测试逻辑复位态。这时,TAP发出复位信号使所有的测试逻辑不影响元件的正常运行。

•若需要进行边界扫描测试。可以在TMS与TCK的配合控制下,退出复位,进入边界扫描测试需要的各个状态。

•需要测试时,在TMS和TCK的控制下,TAP控制器跳出TLR状态(测试逻辑复位),从选择数据寄存器扫描(Shift DRScan)或选择指令寄存器扫描(Shift IR Scan)进入图2所示的各个状态。Shift DR Scan和Shift IR Scan两个模块的功能类似。

•进入每个模块的第一步是捕捉数据(Capture),

•对于数据寄存器,在Capture DR状态把数据并行加载到相应的串行数据通道中,

•对于指令寄存器,则是在Capture IR状态把指令信息捕捉到指令寄存器中。

• TAP控制器从捕捉状态进入移位(Shift)或跳出1(Exit1)状态。通常,Shift状态紧跟Capture状态,数据在寄存器中移位。

•在Shift状态之后,TAP控制器通过Exit1状态进入更新(Update)状态或者暂停(Pause)状态。

•在Pause状态,数据移位暂时终止,可以对数据寄存器或指令寄存器重新加载测试向量。

•从Pause状态出来通过跳出2(Exit2)状态可以再次进入Shift状态或者经过Update状态回到Run Test Idle状态。在Update状态,移入扫描通道的数据被输出。

这个状态机看似很复杂,其实理解以后会发现这个状态机其实很直接、很简单。观察上图,我们可以发现,除了Test-Logic Reset和Test-Run/Idle状态外,其他的状态有些类似。例如Select-DR-Scan和Select-IR-Scan对应,Capture-DR和Capture-IR对应,Shift-DR和Shift-IR对应,等等。在这些对应的状态中,DR表示Data Register,IR表示Instruction Register。记得我们前面说过吗,寄存器分为两大类,数据寄存器和指令寄存器。其实标识有DR的这些状态是用来访问数据寄存器的,而标识有IR的这些状态是用来访问指令寄存器的。

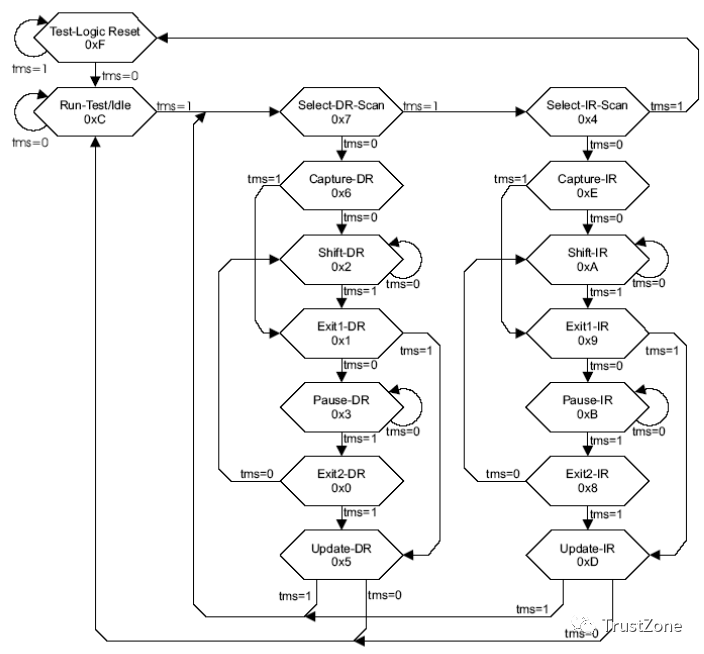

让我们来看一个更直观的例子。现在假设,TAP Controller 现在处在 Run-Test/Idle 状态,指令寄存器当中已经成功的写入了一条新的指令,该指令选定的是一条长度为6的边界扫描链。

下面让我们来看看实际如何来访问这条边界扫描链。下图所示的是测试芯片及其被当前指令选定的长度为6的边界扫描链。由下图可以看出,当前选择的边界扫描链由6个边界扫描移位寄存器单元组成,并且被连接在TDI和TDO之间。

在这里插入图片描述

TCK 时钟信号与每个边界扫描移位寄存器单元相连。每个时钟周期可以驱动边界扫描链的数据由TDI到TDO的方向移动一位,这样,新的数据可以通过 TDI 输入一位,边界扫描链的数据可以通过 TDO 输出一位。经过6个时钟周期,就可以完全更新边界扫描链里的数据,而且可以将边界扫描链里捕获的6位数据通过TDO全部移出来。

•图(1)表示了芯片和边界扫描链的初始化状态,在测试状态下,芯片的外部输入和输出被隔离开了,芯片的输入和输出可以通过相应的边界扫描链来观察和控制。

•在图(1)中,扫描链里的每个移位寄存器单元的数据是不确定的,所以在图中用X表示,整个扫描链里的数据序列是XXXXXX。

•要从TDI输入到测试芯片上的数据序列是:101010. 同时要从TDO得到芯片相应管脚上的状态。

•现在TAP Controller从Run-Test/Idle状态经过Select-DR-Scan状态进入到Capture-DR状态,在 Capture-DR 状态当中,在一个TCK时钟的驱动下,芯片管脚上的信号状态全部被捕获到相应的边界扫描移位寄存器单元当中去,如图(2)所示。

•从图(2)中我们可以看出,在进入 Capture-DR 状态后,经过一个 TCK 时钟周期,现在扫描链中的数据序列变成了:111000.

•在数据捕获完成以后,从Capture-DR状态进入到Shift-DR状态。

•在Shift-DR状态中,我们将通过6个TCK时钟周期来把新的数据序列(101010)通过 TDI 输入到边界扫描链当中去;

•同时,将边界扫描链中捕获的数据序列(111000)通过 TDO 输出来。

•在进入到 Shift-DR 状态后,每经过一个 TCK 时钟驱动,边界扫描链从 TDO 输出一位数据;同时,从 TDI 接收一位新的数据。

•图(3)所示的是在 Shift-DR状态下,1 个 TCK 时钟周期后的扫描链的变化。图(4)所示的是在Shift-DR状态下,2个TCK时钟周期后的扫描链的变化。此时,扫描链已经从TDI串行得到了两位新数据,从TDO也串行输出了两位数据。在TCK时钟的驱动下,这个过程一直继续下去。图(5)所示的是在经过6 个 TCK 时钟周期以后扫描链的情况。

•从图(5)中我们可以看到:边界扫描链当中已经包含了新的数据序列:101010. 在TDO端,经过6个TCK时钟驱动以后,也接收到了在Capture-DR状态下捕获到的数据序列:111000.

•到目前为止,虽然扫描链当中包含了新的数据序列:101010,但测试芯片的管脚上的状态还是保持为:111000.下一步,需要更新测试芯片相应管脚上的信号状态。要实现更新,

•TAP Controller 从 Shift-DR 状态,经过 Exit1-DR 状态,进入到 Update-DR 状态。在 Update-DR 状态中,经过一个周期的 TCK 时钟驱动,边界扫描链中的新数据序列将被加载到测试芯片的相应管脚上去,如图(6)所示。

•从图(6)可以看出,测试芯片的状态已经被更新,相应管脚上的状态序列已经从111000变为101010.最后从 Update-DR状态回到 Run-Test/Idle 状态,完成对选定的边界扫描链的访问。

关于Pause-DR/Pause-IR状态

这两个状态是暂停状态,比如说我们要通过32bit的总线从一个48长度的扫描链中读出相应管脚的状态,我们需要读两次才能将48bit的扫描链状态读出来,先经过32个TCK时钟读出高32bit的状态,然后转到Pause-DR状态等待总线读响应,响应完成后再进入Shift-DR经过16个TCK时钟读出低16bit数据。

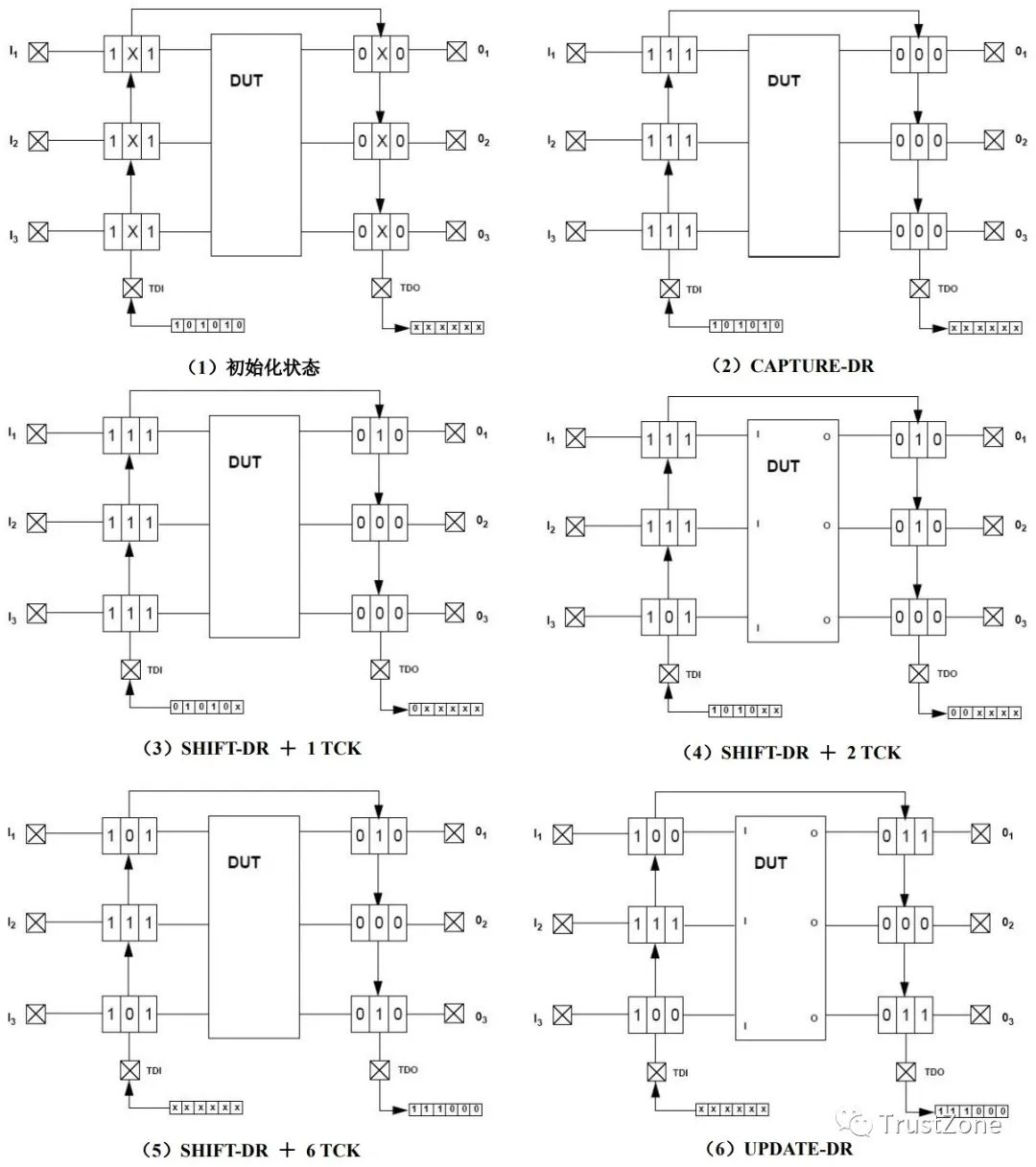

5-BST寄存器单元

边界扫描数据寄存器至少应该包括3种:边界扫描寄存器、器件标识寄存器和旁路寄存器。

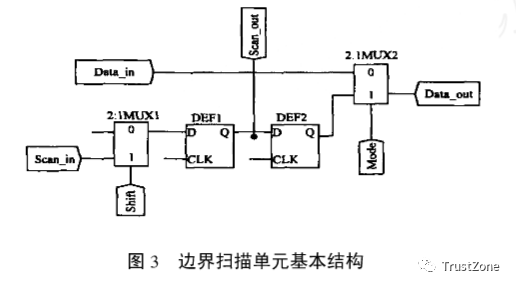

1-边界扫描寄存器

(1)边界扫描寄存器构成边界扫描路径,他的每一个单元由存储器、发送/接收器和缓冲器组成。边界扫描单元置于集成电路的输入/输出端附近,并首尾相连构成一个移位寄存器链,首端接TDI,末端接TDO。在测试时钟TCK的作用下,从TDI加入的数据可以在移位寄存器链中移动进行扫描。

在这里插入图片描述

边界扫描单元(BSC)基本结构如上图所示。其主要作用是加载测试向量和捕捉测试响应。

D类型触发器,它是在时钟信号作用下,输出结果根据D的状态而改变。DFF是边沿触发,DFF,即数据触发型触发器(Data Flip-Flop),是一种基于存储单比特的数据的触发器,常用于数字电路、计算机硬件和嵌入式系统等领域。(D触发器)

MUX2由Mode信号控制,

•Mode信号为0时,可以使单元的数据输出与数据输入相连;

•为1时,数据输出端的数据是DFF2的输出信号,与数据输入端的信号无关。

Shift信号控制MUX1,

•为0时,DFF1采样数据输入端的信号;

•为1时,进行移位。

BSC的工作按照以下4个步骤进行:

•MUX1在Shift DR模式,移入新的测试向量;

•MUX2在Update DR模式,加载测试向量到单元的数据输出端;

•MUX1在Capture DR模式,捕捉单元并行输入端的响应;

• MUX1在Shift DR模式,移出响应。

在这里插入图片描述

2- 器件识别寄存器(ID)

器件识别寄存器(ID)有32位,

•其中31~28位是版本号,

•27~12位是器件序列号,

•11~1位是厂家标识,

•第0位为1。

借助他可以辨别板上元器件的生产商,还可以通过他来测试是否将正确的器件安装在PCB板的正确位置。器件标识寄存器和边界扫描寄存器可以使用相同的边界扫描单元。

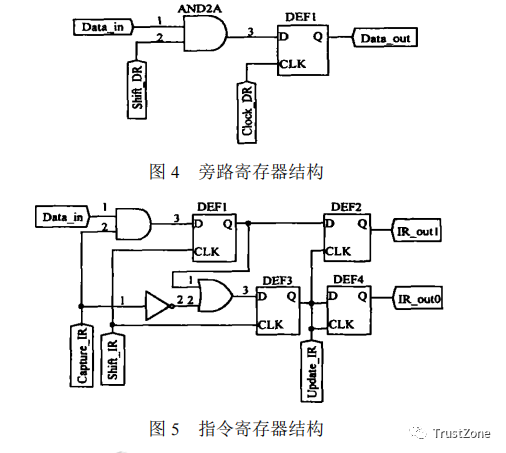

3-旁路寄存器(BR)

旁路寄存器(BR)只有1位,他提供了一条从TDI到TDO之间的最短通道,用来将不参加串行扫描的数据寄存器的数据旁路掉,以减少不必要的扫描时间。旁路寄存器的结构如下图4所示。在Shift DR模式下,数据直接从Data in到Data out,而不经过任何边界扫描寄存器。

在这里插入图片描述

6-指令寄存器

指令寄存器由串移位级和并行锁存级组成,进行指令的译码,两位指令的指令寄存器的结构如上图图图5所示。

其位数由所选指令数决定,常用指令很多。DFF1和DFF2在Capture IR和Shift IR的控制下,进行两位指令译码,在Update IR模式下指令数据加载到指令输出端,高位在IR out1,低位在IR out2。

IEEE114911标准中定义了大量指令,有必须的,有可选的,而且也允许定义更多特定设计的指令来扩展测试逻辑的功能。(这里可能就是我们的SIR 6/SDR 6这种)

此外,除了上述数据寄存器以外,还可以包括用户定义的数据寄存器。

7-JTAG指令

1-JTAG指令

必须提供的Public Instructions

•BYPASS, SAMPLE/PRELOAD,EXTEST

•如果有Device Identification Register 必须提供IDCODE ;如果是可编程IC,还要提供USERCODE。可选的Public Instructions

• INTEST,RUNBIST IC厂商可以自定义Public or Private Instructions,Public Instructions的资料必须公开。

2-JTAG电路指令码

• BYPASS::全1 IC厂商可以再分配几个其它的binary code

• EXTEST:全0 , IC厂商可以再分配几个其它的binary code

SAMPLE/PRELOAD,INTEST,RUNTEST,IDCODE,USERCODE: IC厂商自行分配binary code。

未分配的binary code表示BYPASS,

3-BSDL简单介绍

FPGA器件EP1C12F256的BSDL文件指令:

•"BYPASS (1111111111), "&

•"EXTEST (0000000000), "&

•"SAMPLE (0000000101), "&

•"IDCODE (0000000110), "&

•"USERCODE (0000000111), "&

•"CLAMP (0000001010), "&

•"HIGHZ (0000001011);

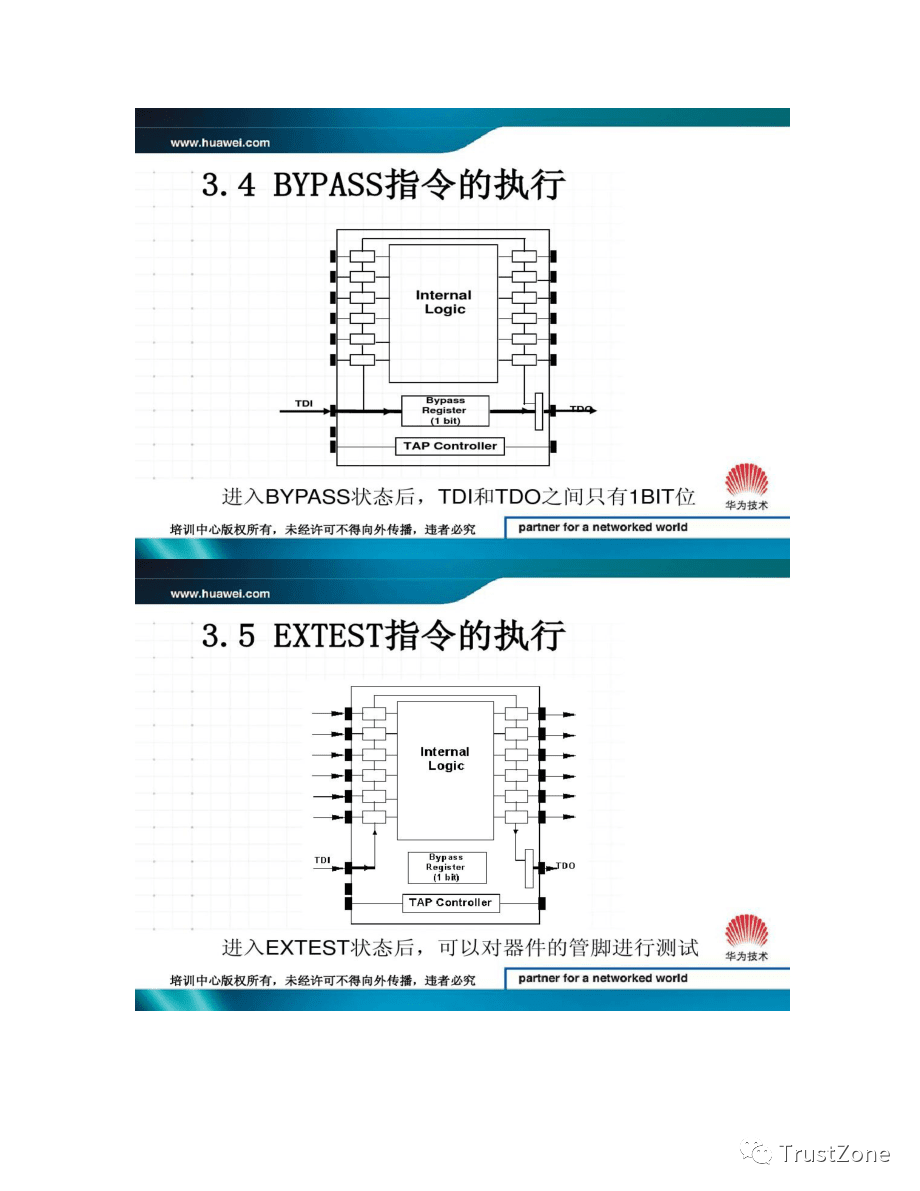

4-BYPASS指令的执行

在这里插入图片描述

5-EXTEST指令的执行

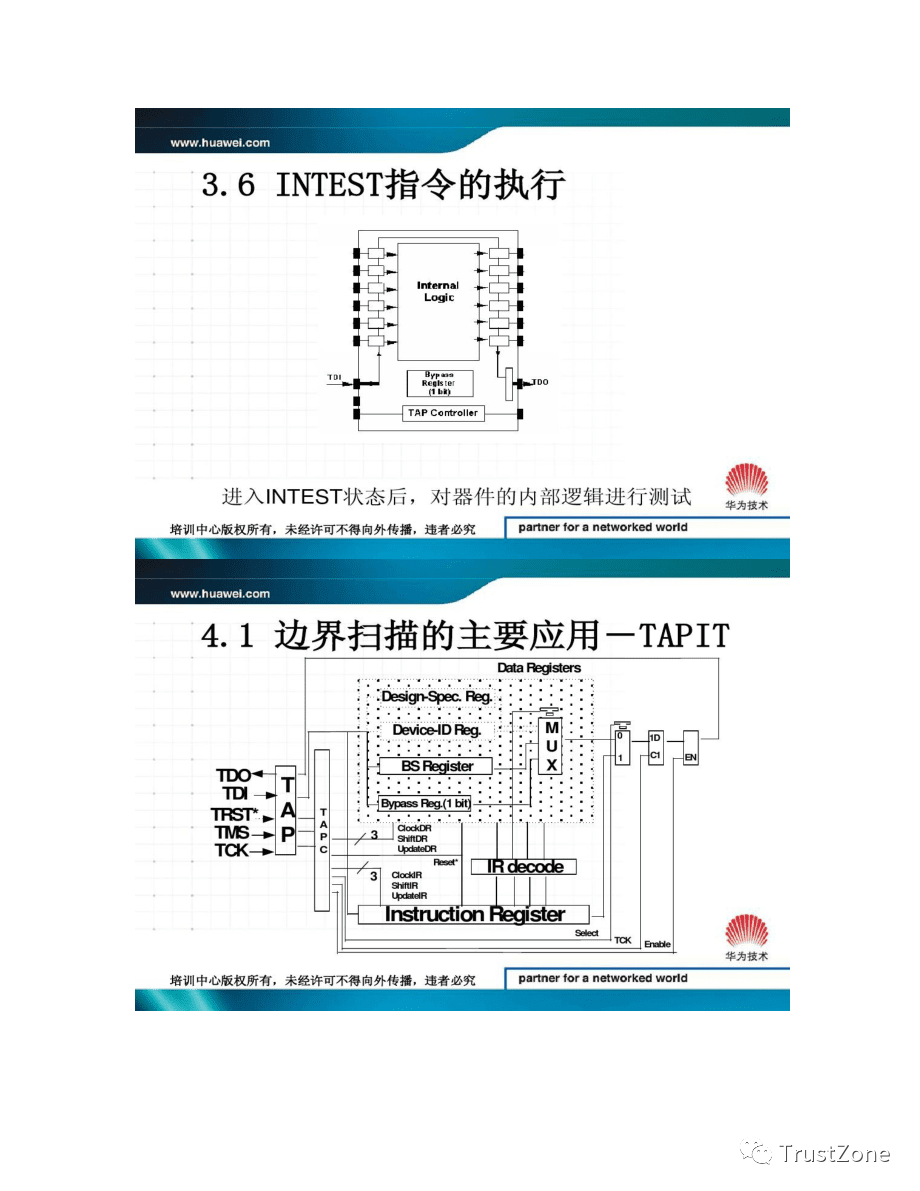

6-INTEST指令的执行

在这里插入图片描述

3-Serial Vector Format File

为测试可编程逻辑器件(PLD)设计而创建的文件;

包含一个或多个测试用例的说明,如组合逻辑检查;

用于调试印刷电路板(PCB)、集成电路(IC)和嵌入式系统。

.SVF 格式符合联合测试操作(JTAG)标准,该标准也称为标准测试访问端口和边界扫描架构。.

SVF 文件以ASCII文本格式存储,可以使用文本编辑器进行编辑。

.SVF自动测试设备(ATE)通常使用文件,这些设备连接到PLD(可编程逻辑器件)中的调试端口来执行测试。没有调试端口的pld通常提供其他机制来逐步进行逻辑测试。

注:串行矢量格式文件也可以二进制格式存储在.XSVF 文件中。

4-边界扫描测试方式

利用边界扫描技术,可以对集成电路芯片的内部故障、电路板的互连以及相互间影响有比较全面的了解,并通过加载相应指令到指令寄存器来选择工作方式。不同的测试在不同的工作方式下进行。

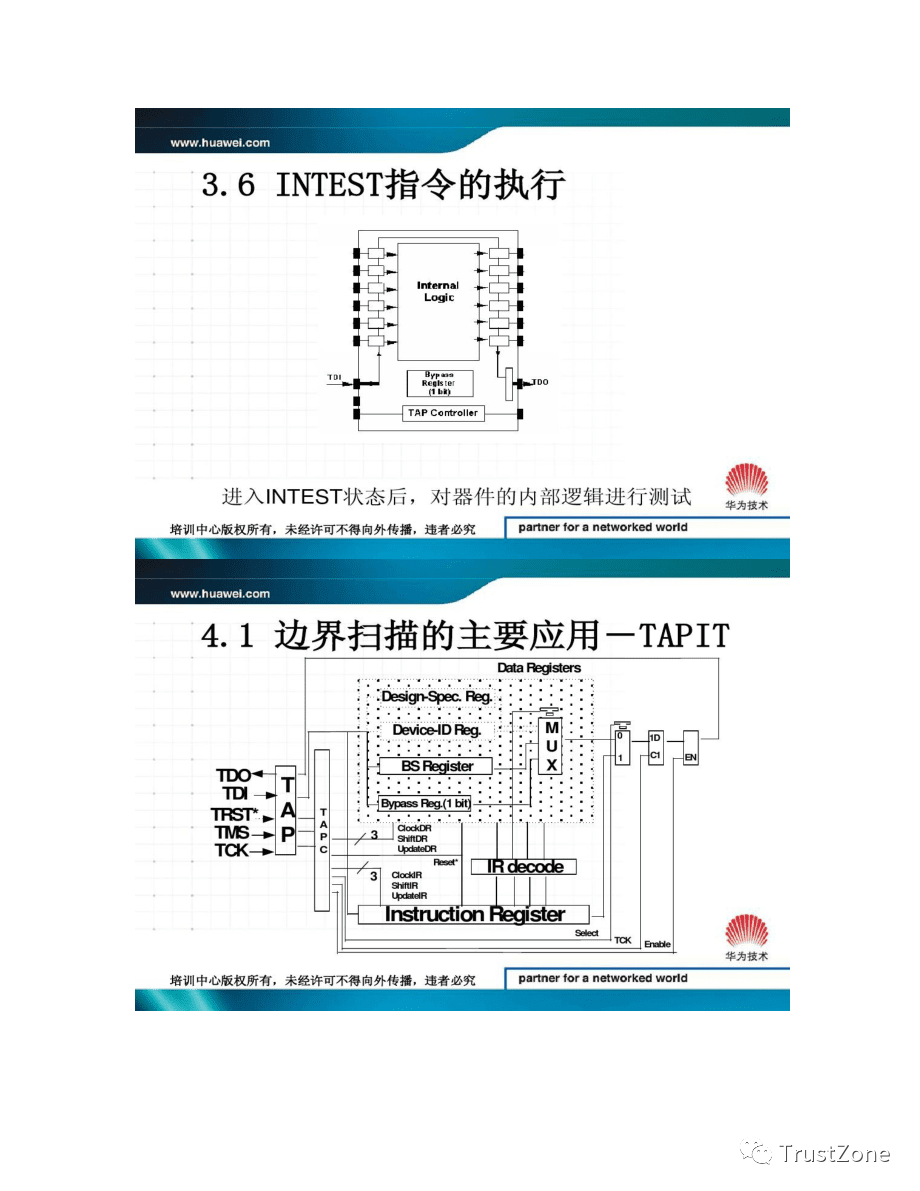

1-外测试(EXTEST)

外测试测试IC与电路板上其他器件的连接关系。

此时边界扫描寄存器把IC的内部逻辑与被测板上其他元件隔离开来。

在EXTEST指令下,给每个IO端赋一个已知的值用于测试电路板上各集成电路芯片间连线以及板级互连的故障,包括断路故障和短路故障。

图6中的3块芯片受相同的TCK和TMS总线控制,各芯片TDO的输出端连接到下一器件TDI的输入端,构成了一条移位寄存器链。测试向量从IC1的TDI输入,通过边界扫描路径加到每个芯片的输出引脚寄存器,而输入引脚寄存器则接收响应向量。

图中IC2的B脚接收IC1的A脚寄存器的信号,正常情况下,B脚的值应该为1。但如果AB和CD线间出现了短路,则B脚寄存器接收到的值变成了0。IC3的F引脚寄存器接收IC1的E脚寄存器信号,正常情况下,F脚的值应该为1,但如果引线EF间出现了断路,则从F脚得到的值不是1,而是0。

在电路板的测试中出现最频繁的是断路和短路故障,传统的逐点检查的方法既麻烦又费时,而通过边界扫描技术的外部测试方式,把从TDO端输出的边界扫描寄存器的串行信号与正确的信号相比较,就可以方便有效地诊断出电路板引线及芯片引脚间的断路和短路故障。这是边界扫描技术一个非常显著的优点。

在这里插入图片描述

2-内测试 ( IN TEST )

内测试测试IC本身的逻辑功能,即测试电路板上集成电路芯片的内部故障。

测试向量通过TDI输入,并通过边界扫描通道将测试向量加到每个芯片的输入引脚寄存器中,从输出端TDO可以串行读出存于输出引脚寄存器中各芯片的响应结果。根据输入向量和输出响应,就可以对电路板上各芯片的内部工作状态做出测试分析。(输出应该是有个预期值,或者预期的结果和现象)

3-采样测试方式 (SAMPLE/PRELOAD )

采样测试方式常用于对一个正在运行的系统进行实时监控。取样/预置(SAMPLE/PRELOAD),

•在捕捉阶段从输入端取样,

•在更新阶段预置BSC,为外测试做准备;

•移出器件标识(ID Code):选择旁路寄存器,使数据在ASIC间快速移位。

4-边界扫描连的主要应用

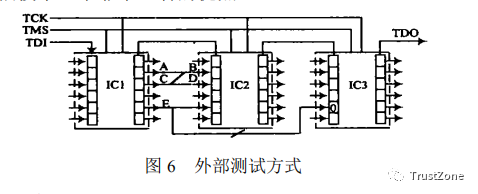

1-TAPIT

在这里插入图片描述

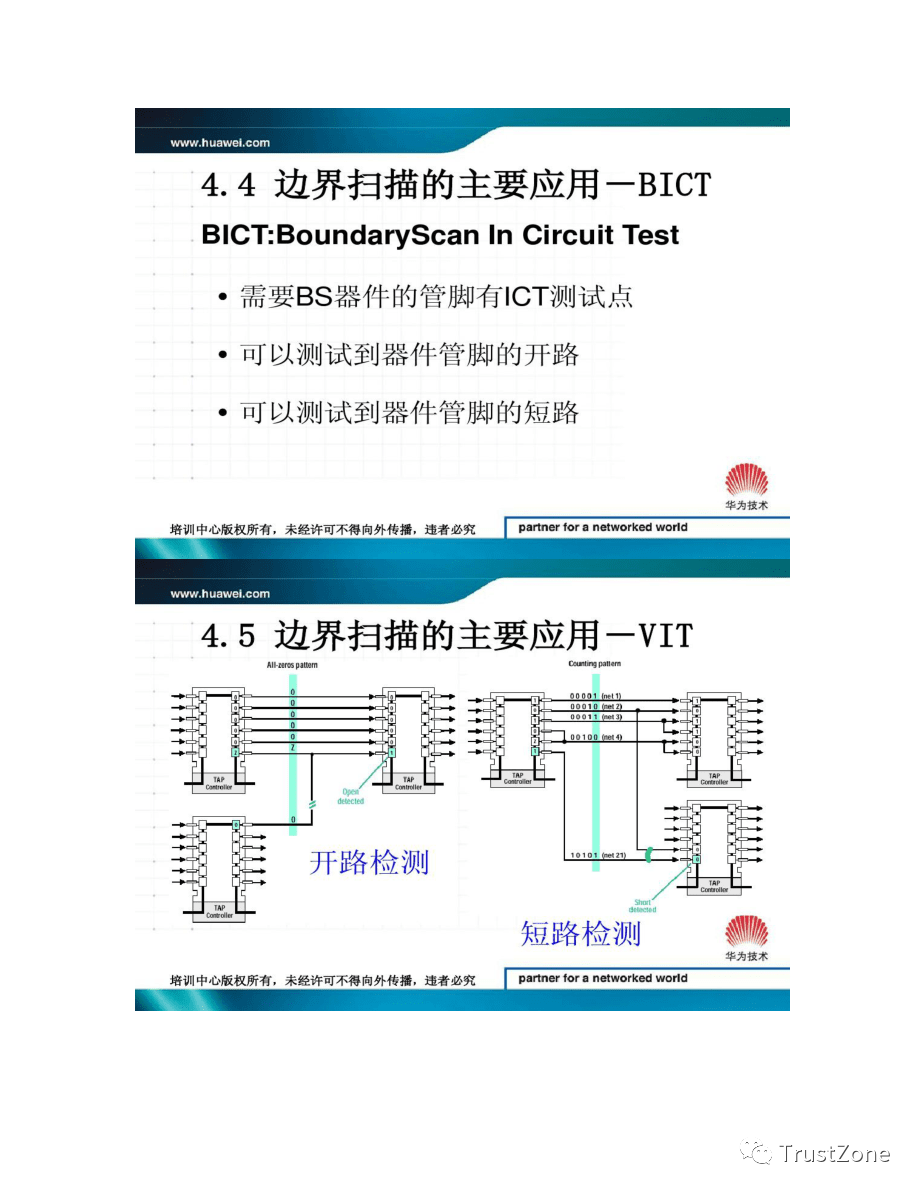

2-BICT

3-VIT

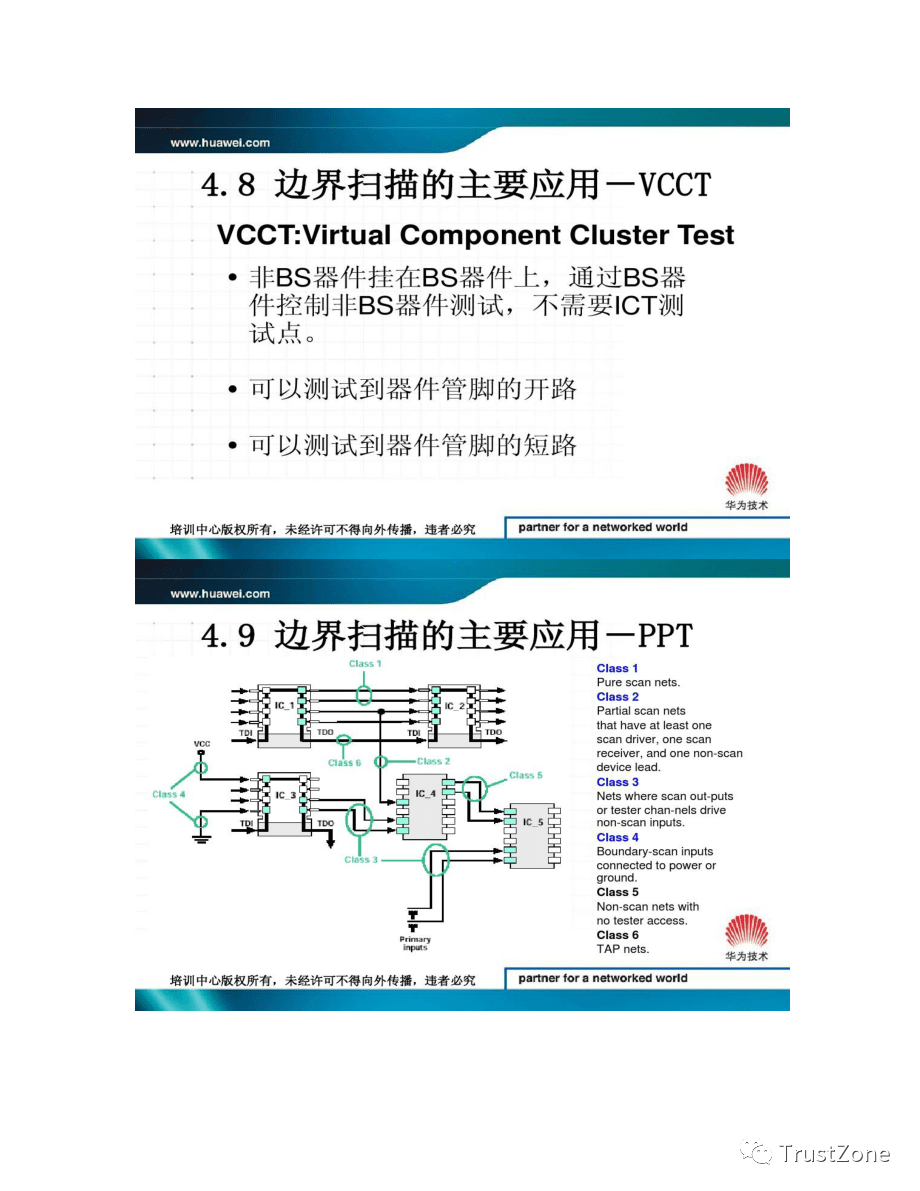

4-VCCT

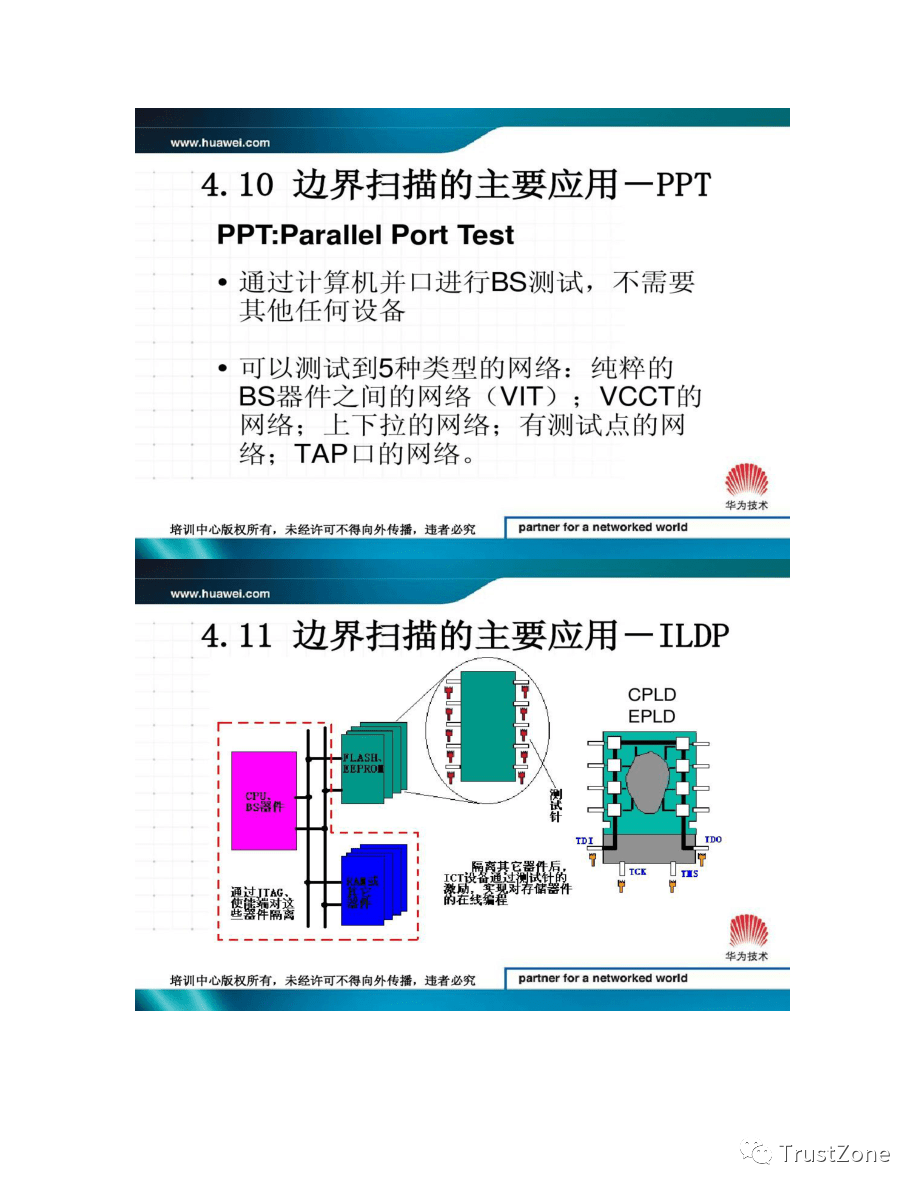

5-PPT

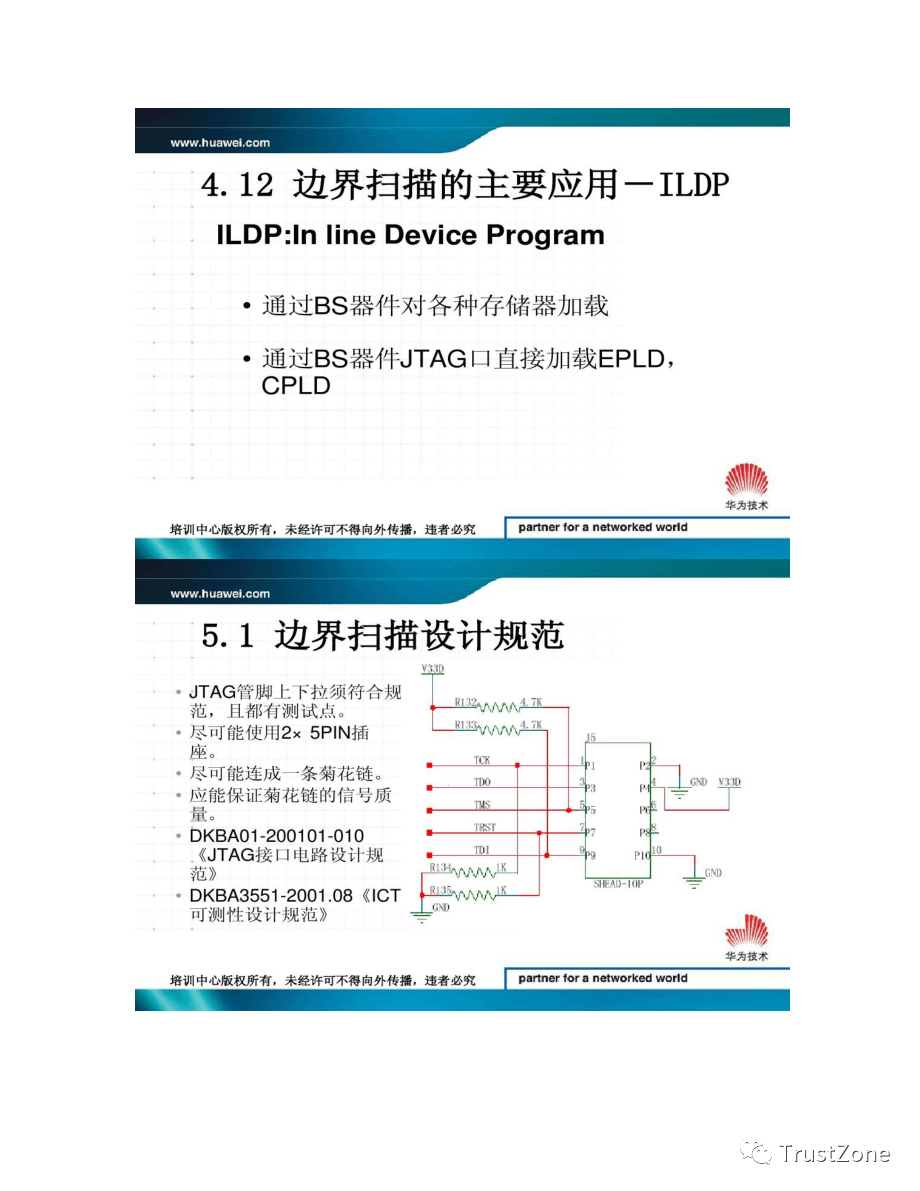

6-ILDP

在这里插入图片描述

在这里插入图片描述

在这里插入图片描述

在这里插入图片描述

在这里插入图片描述

5-JTAG硬件设计

在这里插入图片描述

在这里插入图片描述

6-小结

此外还有多种测试指令,他们的存在和不断扩充,使边界扫描技术的应用得以拓展和延伸,进行更有效的集成电路测试。

边界扫描技术是一种新的测试技术,虽然他能够测试集成电路芯片的输入/输出管脚的状态,也能测试芯片内部工作情况以及引线级的断路和短路故障,但是边界扫描技术还处于不断发展之中。

他的应用是建立在具有边界扫描电路设计的集成电路芯片基础上的。对于电路板上安装的不带边界扫描电路的器件的测试,边界扫描是无能为力的。今后也不可能将所有的数字集成电路芯片设计上边界扫描电路,因此他也不可能完全代替其他的测试方法。这种方法的突出优点是具有测试性,可以只通过运行计算机程序就能检查出电路或连线的故障,这在可靠性要求高、排除故障要求时间短的场合非常适用。特别是在武器装备的系统内置测试和维护测试中具有很好的应用前景。

审核编辑:汤梓红

-

集成电路

+关注

关注

5391文章

11605浏览量

362751 -

pcb

+关注

关注

4324文章

23155浏览量

399148 -

嵌入式

+关注

关注

5089文章

19170浏览量

306802 -

IC

+关注

关注

36文章

5976浏览量

175977 -

指令

+关注

关注

1文章

611浏览量

35792

原文标题:4-边界扫描测试方式

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

一文详细了解JTAG接口

十大常用电子元器件背后的那些门门道道

一文带你了解步进电机的相关知识

一文搞懂UPS主要内容

一文搞懂开关电源波纹的产生

一文带你搞懂PID

一文带你搞懂磁芯

一文带你搞懂电容!

一文搞懂元宇宙底层硬件(附报告下载)

一文带你搞懂JTAG的门门道道

一文带你搞懂JTAG的门门道道

评论