前言

随着移动通信技术的发展,系统越趋复杂,同时产品集成度要求也越来越高,系统级封装(SiP)成为了最具潜力的候选方案之一,其将不同制程工艺节点的裸芯片Die集成在一个封装里,在满足器件高性能需求的同时,也减少了芯片设计公司的研发成本和时间。

SiP有多种封装形式,如引线键合、倒装芯片、芯片堆叠、晶圆级封装等。其中,QFN封装由于其底部中央的一大块裸露焊盘被焊接到PCB的散热焊盘上,使得芯片具有极佳的电热性能,使其能广泛应用在射频领域上。

一般芯片厂家主要从事片上设计,对于封装部分交由封装厂去进行设计,芯片设计公司为了保证射频链路的阻抗连续性,需要对封装键合线进行仿真,从而与片上版图结合完成整链路的性能评估。

封装厂一般只会给芯片设计公司提供DXF格式的设计文件,DXF是2D文档,若根据封装厂提供的三维参数进行手动建模,会相当繁琐。为此,芯和半导体的Hermes平台提供了Lead Frame流程解决方案,可实现QFN/QFP的DXF文件转3D模型的快速建模,最后结合Hermes 高精度FEM三维全波电磁场求解算法可快速得到求解结果,指导设计优化。

Hermes的Lead Frame建模仿真流程

1.导入DXF设计文件

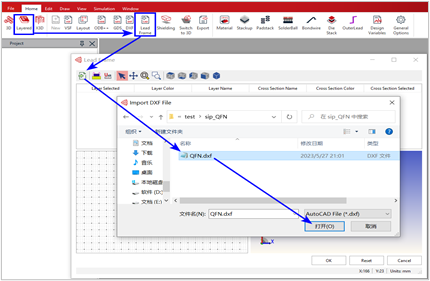

运行Hermes后,在左上角菜单栏中选择Home的layered流程,再选择Lead Frame流程。在弹出窗口中,选择导入所需的DXF文件。

图 1

Lead Frame中导入DXF文件

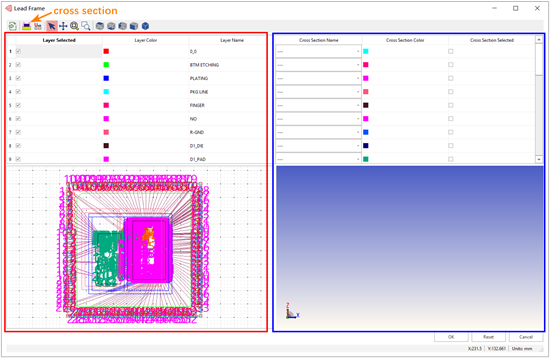

DXF文件导入后,如下图所示。

红色框:上方为DXF文件对应不同图层,用户可选择打开不同的图层显示,下方为上方对应图层的实时2D图显示结果。

蓝色框:上方的cross section name为cross section(橙色箭头)中配置不同图层的选择层,每确定选择一个层后,下方会依据DXF中对应的图形进行3D建模,用户可实时查看模型的建模情况。

图2

Lead Frame窗口说明

2. Cross Section的配置及说明

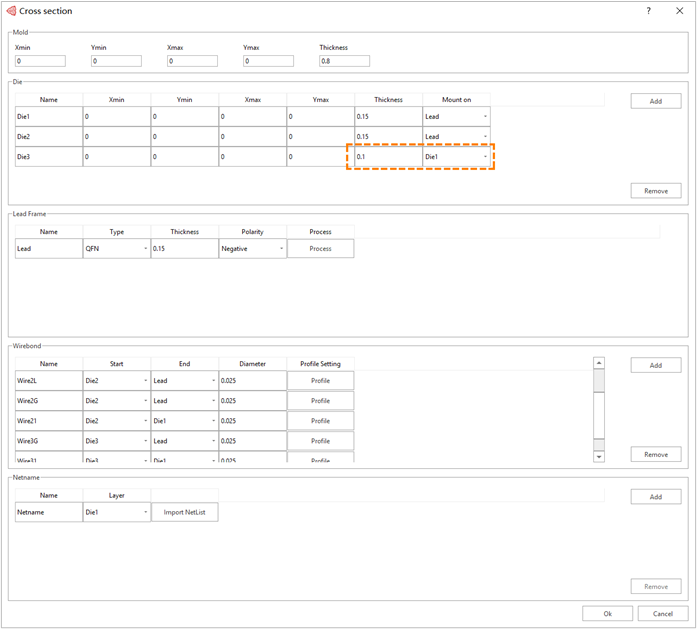

Mold:芯片的整体塑封外壳,此处设置高度为0.8mm。

Lead Frame:Lead层的厚度,这里设置为0.15mm。

Die:芯片中Die的几何信息,XY坐标可无需手动输入,软件可自动捕捉,用户可根据实际需求,按add键进行Die的添加,只需要输入每个Die的装配高度即可。此案例中,一共有3个Die,Die1和Die2平行靠近lead放置,距离lead的高度为0.15mm,而Die3放置在Die1上,Die3的配置如下橙色框所示,参考Die1的装配高度为0.1mm。

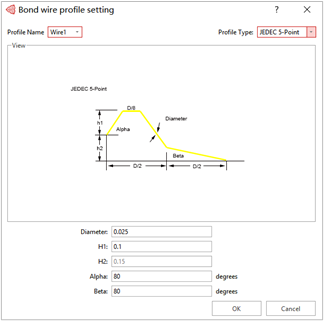

Wire bond:键合线层,用户可在profile中定义键合线的JEDC4/5标准的相关几何信息、线材,线宽等。Start和End分别为键合线打线时的起始和终止位置。此案例中,由于DXF中的wire bond图层共有7个,所以需要设置7种wire bond组合,起始位置分别是Die1->Lead Pad、Die2->Lead Pad、Die1->E Pad、Die2->E Pad、Die3-> E Pad、Die2-> Die1、Die3-> Die1。

NetName:网络名层,封装厂会提供每个die上对应pad的坐标及对应网络名的excel文件,用户导入后,软件可自动为对应的整个网络赋予Excel中对应的网络名。如果没有Excel表格,此处可不填任何信息。

图 3

Cross section配置设置

图4

wire bond 的profile配置窗口

3. DXF模型的编辑及其Cross section映射配置

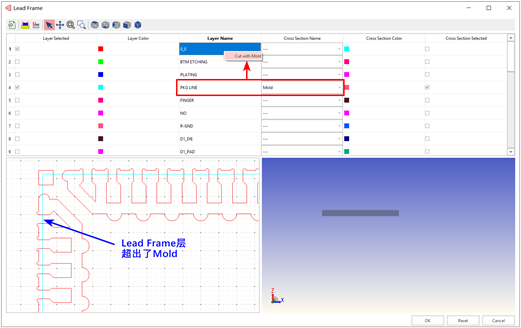

为了方便用户使用,Hermes Lead frame流程提供了一定的编辑功能,能对导入的DXF进行有限的编辑。由于提供的DXF的Lead层超出了Mold层,需要对多出来的部分进行切割。首先把DXF的Mold层(PKG LINE)定义出来(红色框),然后使用右键对DXF的Lead层(0_0)进行切割——Cut with Mold。

图 5

Lead层编辑

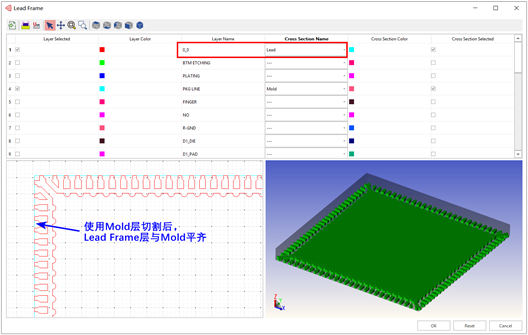

完成切割后,Lead层与Mold平齐,并定义DXF的0_0层为Lead层。

图表 6

Lead层切割后

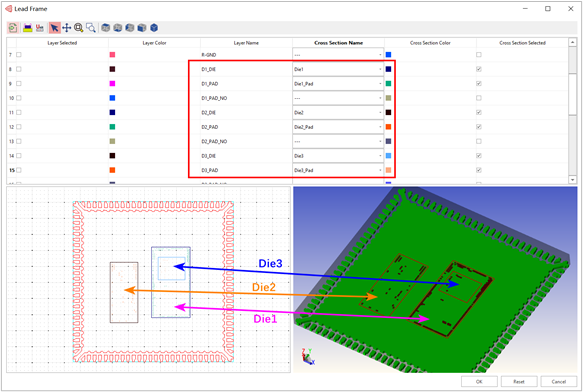

接着在cross section name中,为DXF对应图层配置Die及Die Pad(下图红色框)。

图 7

Die信息配置

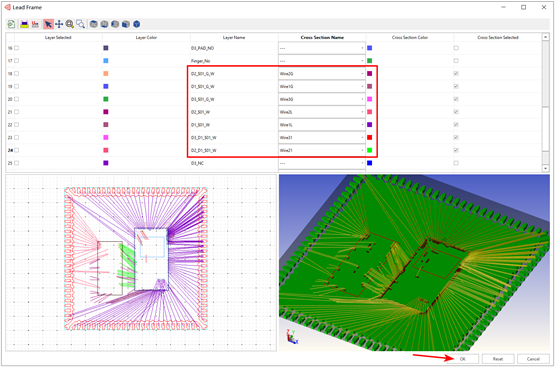

最后完成键合线配置(下图红色框),此时,可在3D窗口中完整的查看整个QFN模型模型了。点击OK,模型即可回导到Hermes平台的工作界面上。

图8

wire bond信息配置

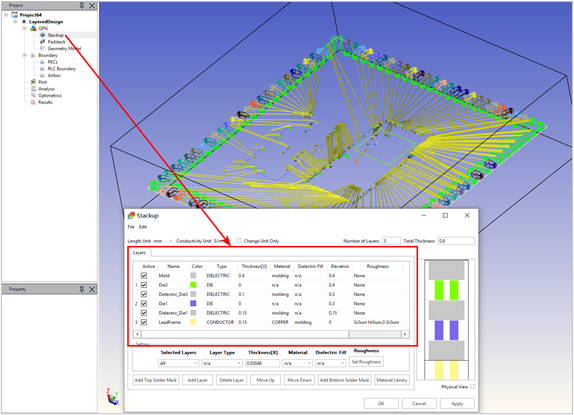

4.叠层属性配置

模型导入到Hermes工作区后,双击Stackup,即可进行叠层及材料属性等配置。

图表 9

叠层设置

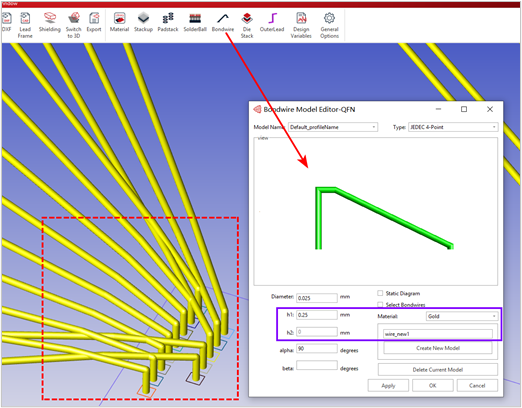

5.键合线的修改

如下图红色框所示,由于这部分的wire bond在DXF中都是同一个图层,所以出线高度难免是一致的,造成短路问题。所以需要对Die内侧的wire bond走线的起始高度进行抬高——新建一个wire bond模型,对高度及材质类型进行设置。

图表 10

新建wire bond模型

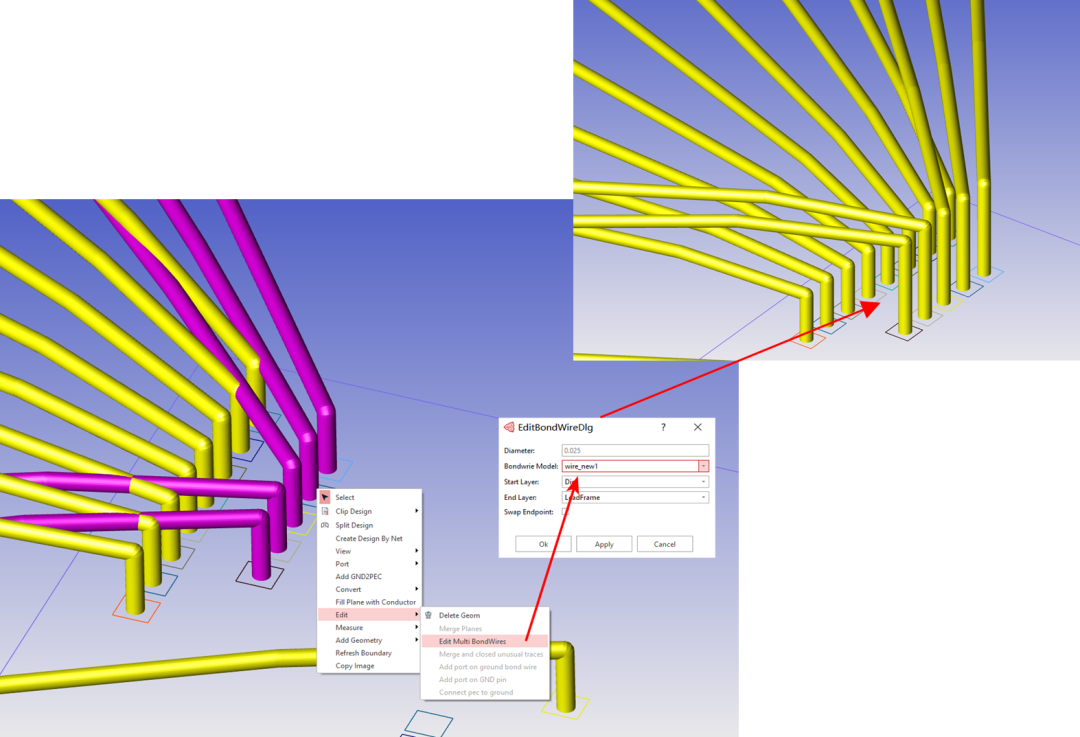

选中需要加高的wire bond模型,右键编辑属性,将其定义为上述新建的wire bond模型,至此,完成了wire bond的修改。

图表11

对异常的wire bond进行重新定义修改

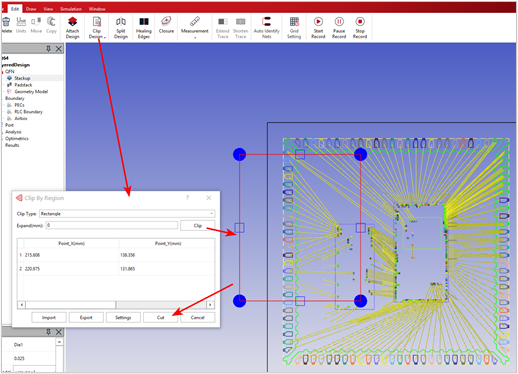

6.模型裁切

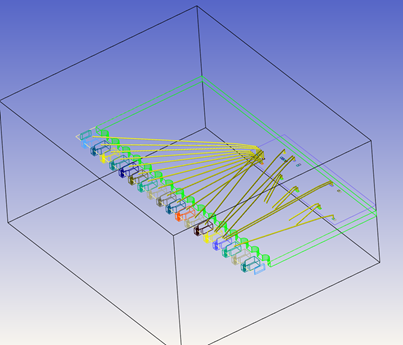

对QFN模型所需的仿真的部分进行切割。

图表 12

矩形切割

图表 13

切割后的模型

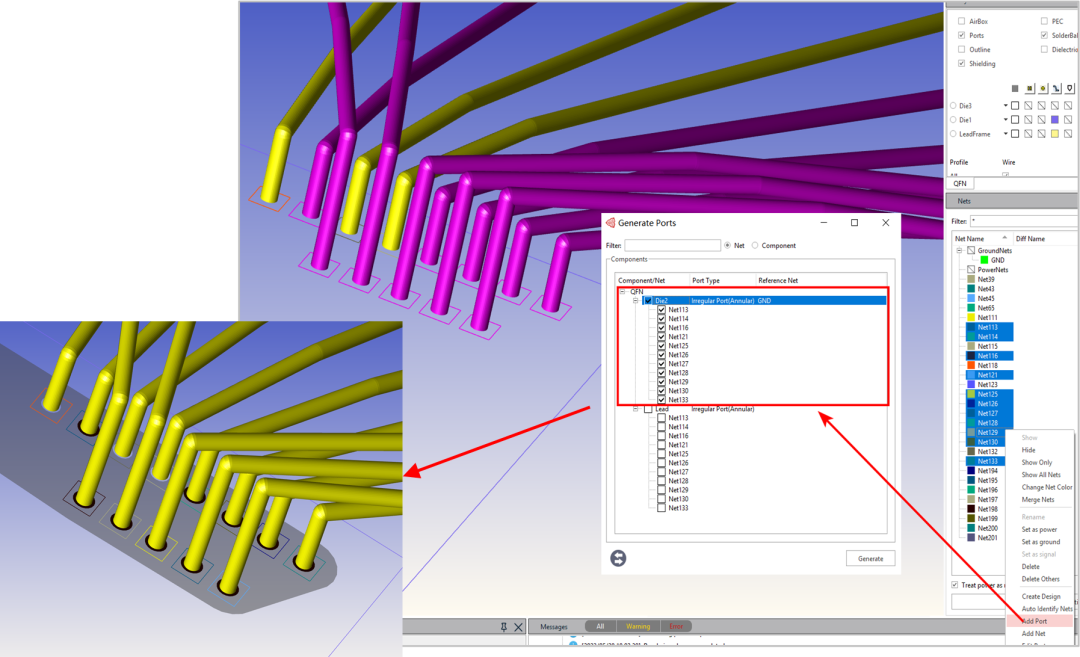

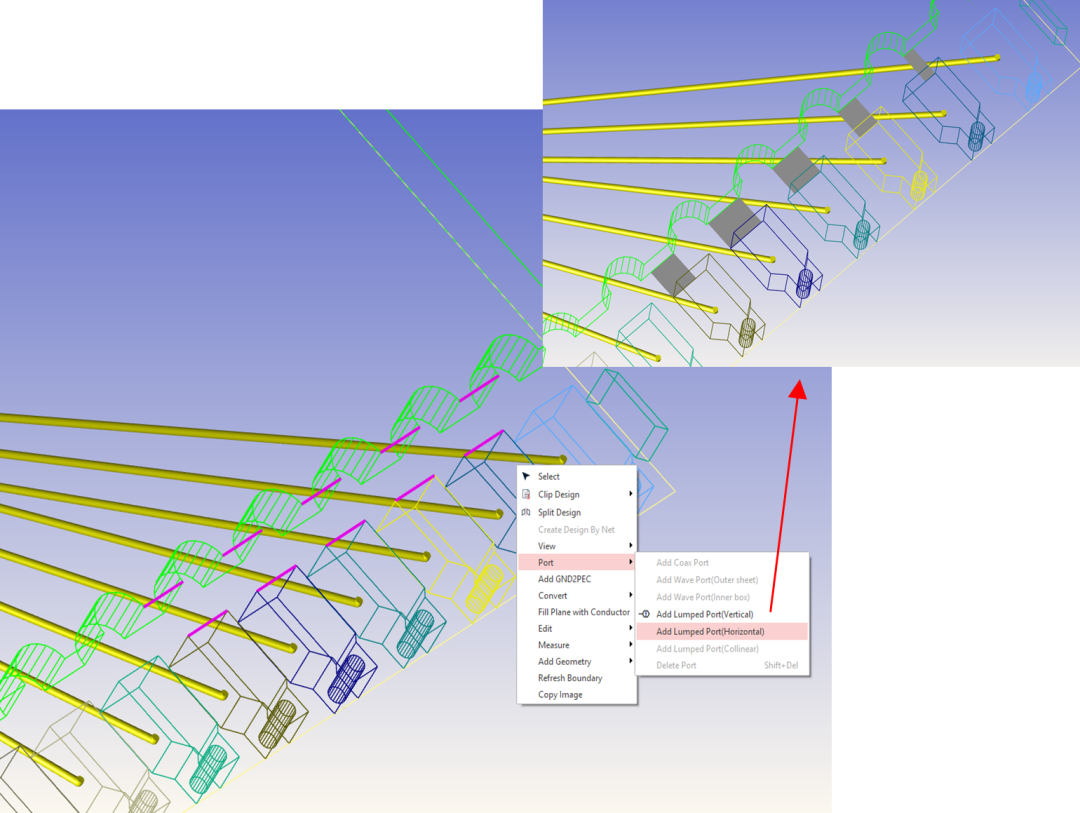

7.Port添加

图表 14

Die上环形端口添加

对于Lead层上pad的端口添加,可以选中pad与E pad的边沿,然后右键添加水平lumped port。

图表 15

Lead pad上lumped port添加

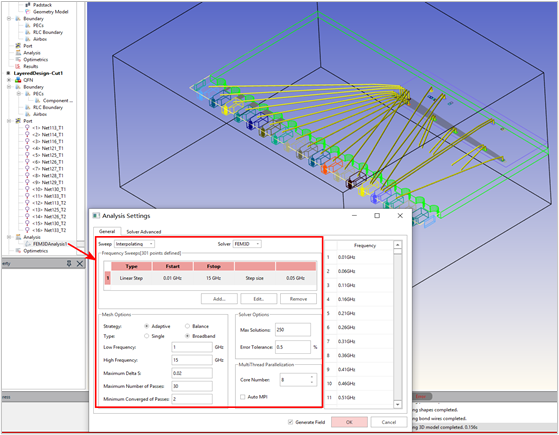

8.仿真配置

在Analysis选项中右键添加一个FEM3D_Analysis配置,通过solver option配置求解频率、收敛条件、MPI以及求解Core数量等,完成后右键点击Analysis开始仿真。

图表 16

仿真配置

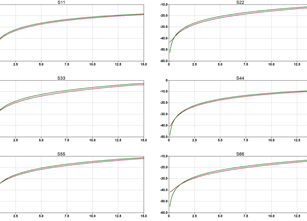

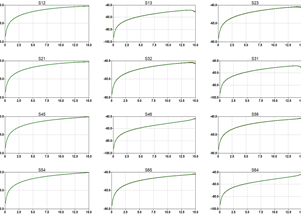

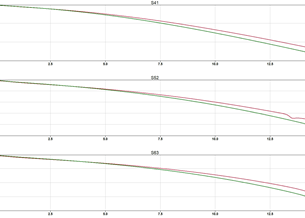

9.仿真结果查看

仿真求解完毕后,可方便地使用芯和半导体的SnpExpert工具进行S参数的批量查看及对比,下图红色曲线为Hermes求解结果,绿色曲线为业界知名的某FEM求解软件结果。从左到右依次为回波损耗、插损及隔离度,其中插损相差不超过0.08dB。

--Hermes

--REF

图表 17

仿真结果对比

(点击各图可查看原图)

总结

本文介绍了采用芯和半导体的Hermes平台实现了多DIE下的QFN模型创建。Hermes内置了便捷易用的Lead Frame流程,实现了DXF 二维版图到3D QFN模型的转换,最后通过灵活的切割、端口创建功能快速完成模型的建模和仿真,可满足芯片、封装用户对DXF设计文件进行快速建模仿真的应用场景需求。

关于芯和半导体EDA

芯和半导体提供“半导体全产业链仿真EDA解决方案”,是新一代智能电子产品中设计高频/高速电子组件的重要工具,拥有领先的2.5D/3D Chiplet先进封装设计分析全流程的EDA平台。产品涵盖三大领域::

芯片设计:匹配主流晶圆厂工艺节点,支持定制化PDK构建需求,内嵌丰富的片上器件模型,帮助用户快速精准地实现建模与寄生参数提取。

封装设计:集成多类封装库,提供通孔、走线和叠层的全栈电磁场仿真工具,为2.5D/3DIC先进封装打造领先的统一仿真平台,提高产品开发和优化效率。

系统设计:基于完全自主产权的EDA仿真平台,打通整机系统建模-设计-仿真-验证-测试的全流程,助力用户一站式解决高速高频系统中的信号完整性、电源完整性、热和应力等设计问题。

关于芯和半导体

芯和半导体是一家从事电子设计自动化(EDA)软件工具研发的高新技术企业,以仿真驱动设计,提供覆盖IC、封装到系统的具备完全自主知识产权的全产业链 EDA 解决方案,支持先进工艺与先进封装,致力于赋能和加速新一代高速高频智能电子产品的设计,已在5G、智能手机、物联网、人工智能和数据中心等领域得到广泛应用。

芯和半导体自主创新的下一代集成无源器件IPD平台,以高集成、高性能、小型化为特色,为移动终端、IoT、HPC、汽车电子等客户提供系列集成无源芯片,累计出货量超20亿颗,并被 Yole 评选为全球IPD 滤波器的主要供应商之一。

芯和半导体创建于2010年,运营及研发总部位于上海张江,在苏州、武汉、西安设有研发分中心,在美国硅谷、北京、深圳、成都、西安设有销售和技术支持部门。

审核编辑:汤梓红

-

SiP

+关注

关注

6文章

543浏览量

107990 -

封装

+关注

关注

128文章

9317浏览量

149021 -

仿真

+关注

关注

55文章

4532浏览量

138647 -

qfn

+关注

关注

3文章

216浏览量

58454 -

芯和半导体

+关注

关注

0文章

126浏览量

32253

原文标题:【应用案例】如何实现“多DIE的QFN建模仿真”

文章出处:【微信号:Xpeedic,微信公众号:Xpeedic】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

基于Cordic的正弦信号发生器建模仿真

DAC电流源失配建模仿真怎么做?

资料下载:基于MATLAB的风电场建模仿真研究牛步柯

为什么要进行建模仿真?

Simulink建模仿真实例快速入门

建模仿真软件MATLAB安装教程资料免费下载

芯和的先进封装建模仿真平台Metis

虹科干货|对于802.1CB协议,不同建模时的保护能力建模仿真分析

Maple—多领域系统级建模仿真和科学计算软件

如何实现多DIE的QFN建模仿真

如何实现多DIE的QFN建模仿真

评论