真正的瓶颈-CoWoS 《下一个风口?》

尽管Nvidia试图大幅增加产量,最高端的Nvidia GPU H100将一直售罄到明年第一季度。

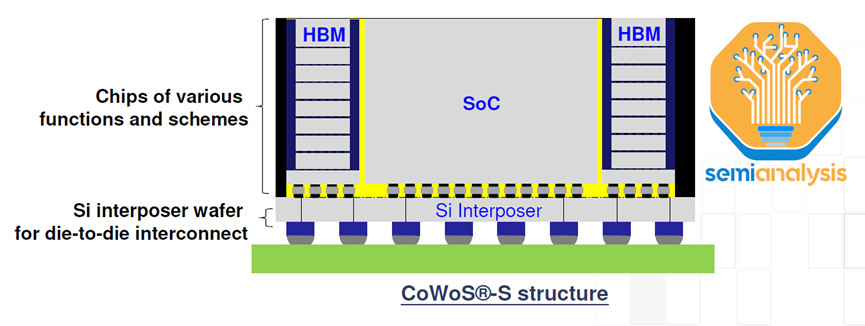

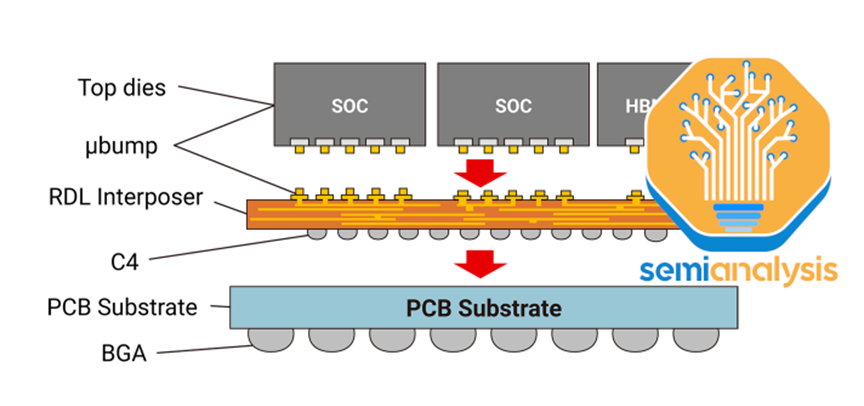

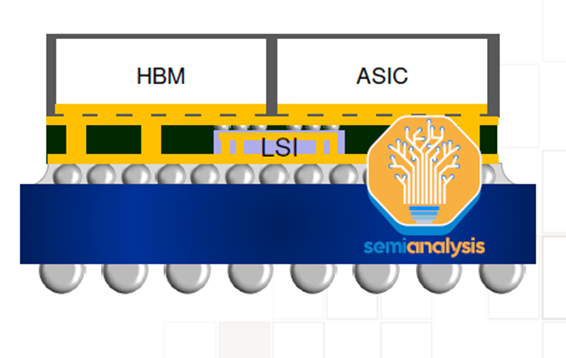

真正的瓶颈是CoWoS容量。CoWoS是台积电的一种“2.5D”封装技术,其中多个有源硅芯片(通常的配置是逻辑和HBM堆栈)集成在无源硅中介层上。中介层充当顶部有源芯片的通信层。然后将内插器和有源硅连接到包含要放置在系统PCB上的I/O的封装基板。

HBM和CoWoS是相辅相成的。HBM的高焊盘数和短迹线长度要求需要2.5D先进封装技术,如CoWoS,以实现这种密集的短连接,这在PCB甚至封装基板上是无法实现的。CoWoS是主流封装技术,以合理的成本提供最高的互连密度和最大的封装尺寸。由于目前几乎所有的HBM系统都封装在Co Wos上,所有先进的人工智能加速器都使用HBM,因此几乎所有领先的数据中心GPU都是台积电封装在Co Wos上的。

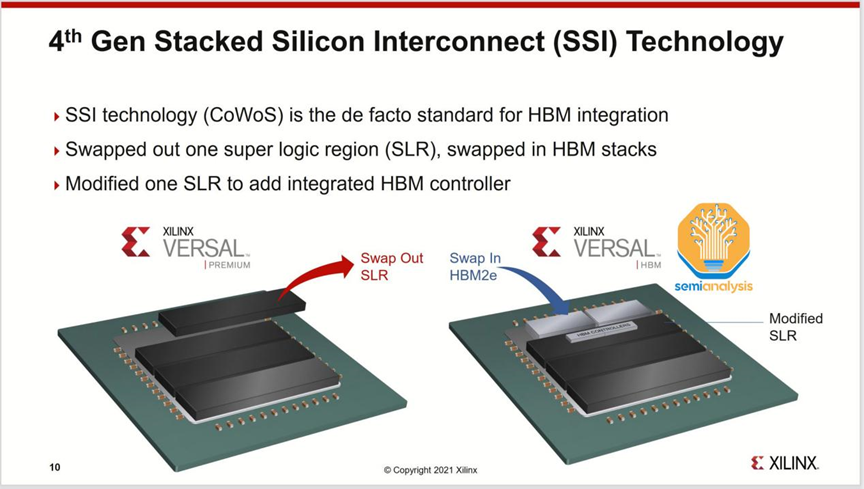

虽然3D封装技术,如台积电的SoIC可以直接在逻辑上堆叠芯片,但由于热量和成本,它对HBM没有意义。SoIC在互连密度方面处于不同的数量级,更适合用芯片堆叠来扩展片内缓存,这一点可以从AMD的3D V-Cache解决方案中看出。AMD的Xilinx也是多年前将多个FPGA芯片组合在一起的第一批CoWoS用户。

虽然还有一些其他应用程序使用CoWoS,例如网络(其中一些用于网络GPU集群,如Broadcom的Jericho3-AI)、超级计算和FPGA,但绝大多数CoWoS需求来自人工智能。与半导体供应链的其他部分不同,其他主要终端市场的疲软意味着有足够的闲置空间来吸收GPU需求的巨大增长,CoWoS和HBM已经是大多数面向人工智能的技术,因此所有闲置空间已在第一季度被吸收。随着GPU需求的爆炸式增长,供应链中的这些部分无法跟上并成为GPU供应的瓶颈。

台积电首席执行官魏哲家表示:“就在最近这两天,我接到一个客户的电话,要求大幅增加后端容量,特别是在CoWoS中。我们仍在评估这一点。”

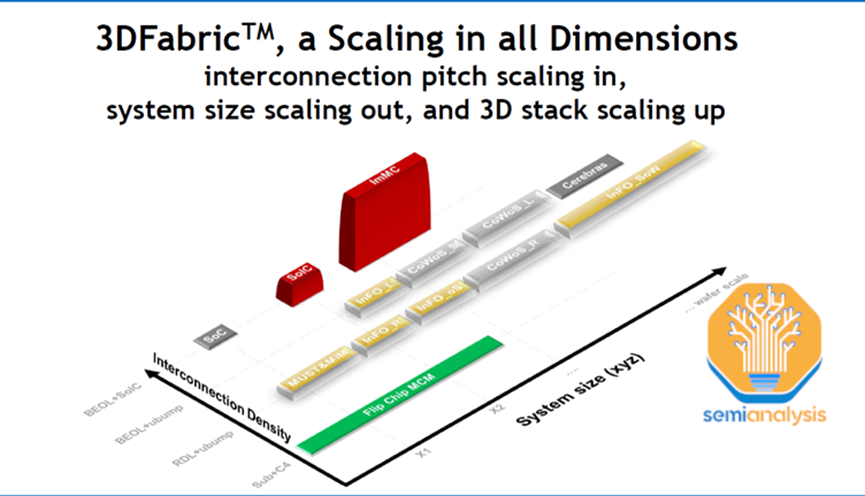

台积电一直在为更多的封装需求做好准备,但可能没想到这一波生成式人工智能需求来得如此之快。6月,台积电宣布在竹南开设先进后端晶圆厂6。该晶圆厂占地14.3公顷足以容纳每年100万片晶圆的3DFabric产能。这不仅包括CoWoS,还包括SoIC和InFO技术。

有趣的是,该工厂比台积电其他封装工厂的总和还要大。虽然这只是洁净室空间,远未配备齐全的工具来实际提供如此大的容量,但很明显,台积电正在做好准备,预计对其先进封装解决方案的需求会增加。

确实有点帮助的是,在Wafer级别的扇出封装能力(主要用于智能手机SoC)方面存在不足,其中一些可以在CoWoS过程中重新使用。特别是有一些重叠的过程,如沉积,电镀,反磨,成型,放置,和RDL形成。我们将通过CoWoS流程和所有的公司谁看到了积极的需求,因为它在一个后续部分。设备供应链中存在着有意义的转变。

还有来自英特尔、三星和OSAT的其他2.5D封装技术(如ASE的FOEB),CoWoS是唯一在大容量中使用的技术,因为TSMC是人工智能加速器的最主要的晶圆厂。甚至英特尔哈巴纳的加速器都是由台积电制造和封装的。

CoWoS变体

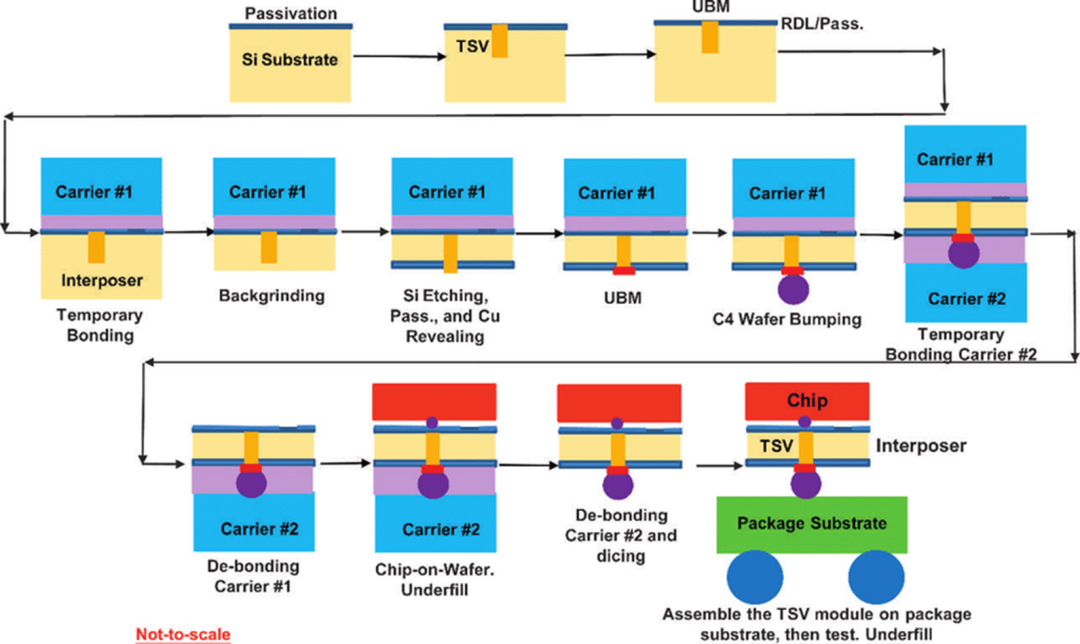

CoWoS有几种变体,但原始CoWoS-S仍然是大批量生产中的唯一配置。这是如上所述的经典配置:逻辑芯片+HBM芯片通过带有TSV的硅基中介层连接。然后将中介层放置在有机封装基板上。

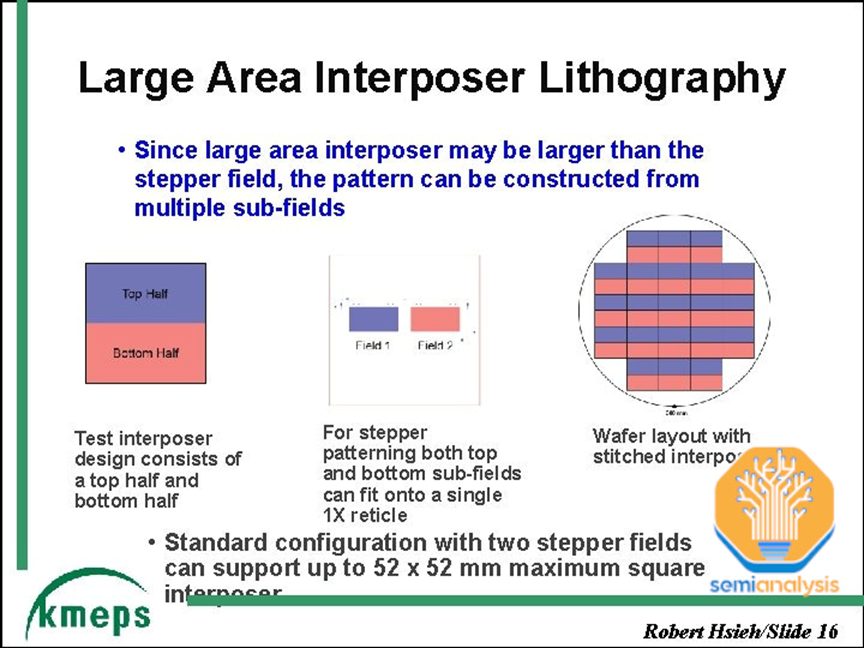

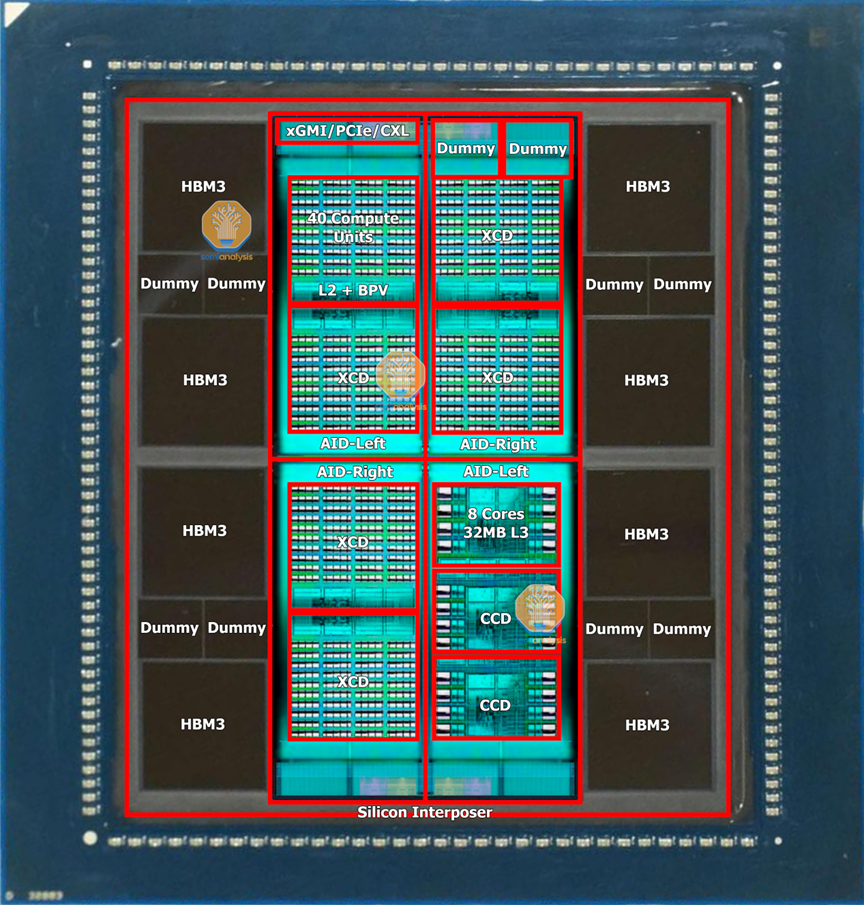

硅中介层的一项支持技术是一种称为“掩模版缝合”的技术。由于光刻工具狭缝/扫描最大尺寸,芯片的最大尺寸通常为26mmx33mm。随着GPU芯片本身接近这一极限,并且还需要在其周围安装HBM,中介层需要很大,并且将远远超出这一标线极限。台积电解决了这与网线拼接,这使他们的模式插入式多次的刻线限制(目前最高3.5倍与AMD MI 300)。

CoWOS-R使用在具有再分布层(RDL)的有机衬底上,而不是硅中间层。这是一个成本较低的变体,牺牲的I/O密度,由于使用有机RDL,而不是基于硅的插入物。正如我们已经详细介绍的,AMD的MI300最初是在CoWoS-R上设计的,但我们认为,由于翘曲和热稳定性问题,AMD不得不使用CoWoS-S。

CoWoS-L预计将在今年晚些时候推出,它采用RDL内插器,但包含有源和/或无源硅桥,用于嵌入内插器中的管芯到管芯互连。这是台积电的相当于英特尔的EMIB封装技术。这将允许更大的封装尺寸,因为硅插入物越来越难以扩展。MI300 Co WO S-S可能是一个单一的硅插入器的限制附近。

这将是更经济的更大的设计去与CoWoS-L台积电正在研究一个CoWoS-L的超级载波内插器在6倍分划板的大小。对于CoWOS-S,他们没有提到 4x reticle 之外的任何内容。这是因为硅插入物的脆弱性。这种硅中间层只有100微米厚,在工艺流程中,随着中间层尺寸的增大,存在分层或开裂的风险。

据 DigiTimes 报道,台积电正在加快与后端设备供应商的合作,因为它开始了晶圆基板上芯片(CoWoS)封装产能的扩张计划。英伟达在人工智能和高性能计算领域占据主导地位的计算GPU短缺,主要归因于台积电有限的CoWoS封装生产能力。

有报道称,台积电计划到 2023 年底将其目前的 CoWoS 产能从每月 8,000 片晶圆增加到每月 11,000 片晶圆,然后到 2024 年底增加到每月 14,500 至 16,600 片晶圆左右。此前有传言称英伟达将提高 CoWoS 产能到 2024 年底,每月生产 20,000 片晶圆。请记住,这些信息来自非官方来源,可能不准确。

Nvidia、亚马逊、博通、思科和赛灵思等主要科技巨头都增加了对台积电先进 CoWoS 封装的需求,并消耗了他们能获得的每一片晶圆。据 DigiTimes 报道,台积电因此被迫重新订购必要的设备和材料。人工智能服务器的产量显着增加,刺激了对这些先进封装服务本已强烈的需求。

Nvidia 已经预订了台积电明年可用 CoWoS 产能的 40%。然而,报告称,由于严重短缺,Nvidia 已开始探索与其二级供应商的选择,向 Amkor Technology 和联华电子 (UMC) 下订单,尽管这些订单相对较小。

台积电还开始实施战略变革,例如将其部分 InFO 产能从台湾北部龙潭工厂重新分配到台湾南部科学园区 (STSP)。它还在快速推进龙潭基地的扩建。此外,台积电正在增加其内部 CoWoS 产量,同时将部分 OS 制造外包给其他封装和测试 (OSAT) 公司。例如,Siliconware Precision Industries (SPIL) 就是这一外包计划的受益者之一。

台积电前段时间开设了先进后端 Fab 6 工厂。它将扩大其前端 3D 堆叠 SoIC(CoW、WoW)技术和后端 3D 封装方法(InFO、CoWoS)的先进封装产能。目前,该晶圆厂已为 SoIC 做好准备。先进后端 Fab 6 每年可处理约 100 万片 300 毫米晶圆,每年进行超过 1000 万小时的测试,其洁净室空间大于台积电所有其他先进封装设施的洁净室空间总和。

Advanced Backend Fab 6 最令人印象深刻的功能之一是广泛的五合一智能自动化物料搬运系统。该系统控制生产流程并立即检测缺陷,从而提高良率。这对于 AMD MI300 等复杂的多小芯片组件至关重要,因为封装缺陷会立即导致所有小芯片无法使用,从而导致重大损失。该工厂的数据处理能力比平均速度快 500 倍,可以维护全面的生产记录并跟踪其处理的每个芯片。

Nvidia 将 CoWoS 用于其非常成功的 A100、A30、A800、H100 和 H800 计算 GPU。AMD 的 Instinct MI100、Instinct MI200/MI200/MI250X 以及即将推出的 Instinct MI300 也使用 CoWoS。

审核编辑:刘清

-

加速器

+关注

关注

2文章

799浏览量

37844 -

人工智能

+关注

关注

1791文章

47208浏览量

238295 -

FPGA芯片

+关注

关注

3文章

246浏览量

39795 -

硅芯片

+关注

关注

0文章

90浏览量

16966 -

CoWoS

+关注

关注

0文章

138浏览量

10485

原文标题:CoWoS是什么?

文章出处:【微信号:光刻人的世界,微信公众号:光刻人的世界】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

CoWoS先进封装技术介绍

明年全球CoWoS产能需求将增长113%

润欣科技与奇异摩尔签署CoWoS-S封装服务协议

CoWoS工艺流程说明

CoWoS是什么?CoWoS有几种变体?

CoWoS是什么?CoWoS有几种变体?

评论