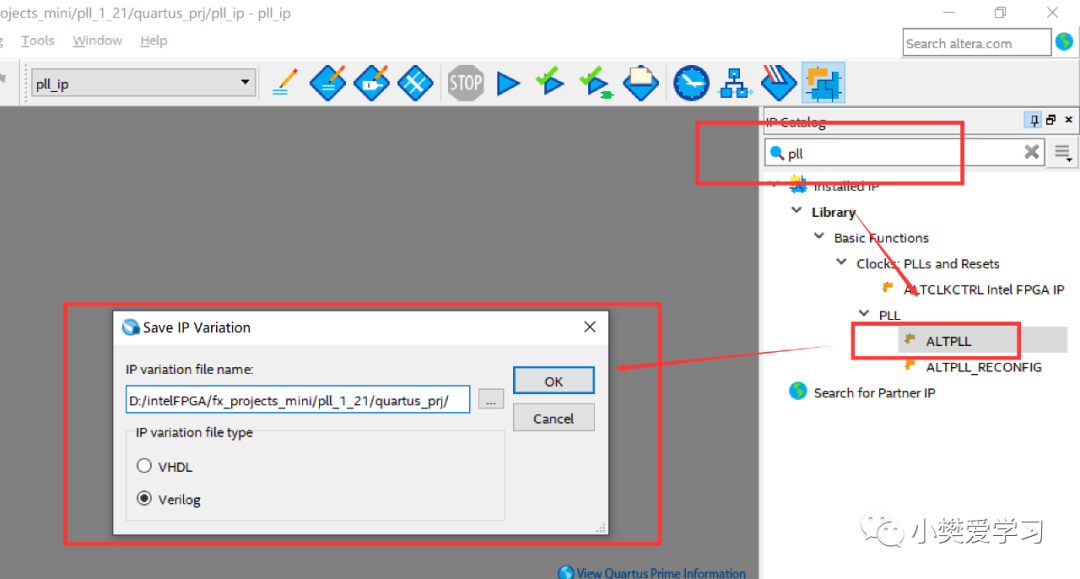

1.在ip目录里搜索pll,选择ALTPLL,点击打开后设置名称并自动保存在目录中。

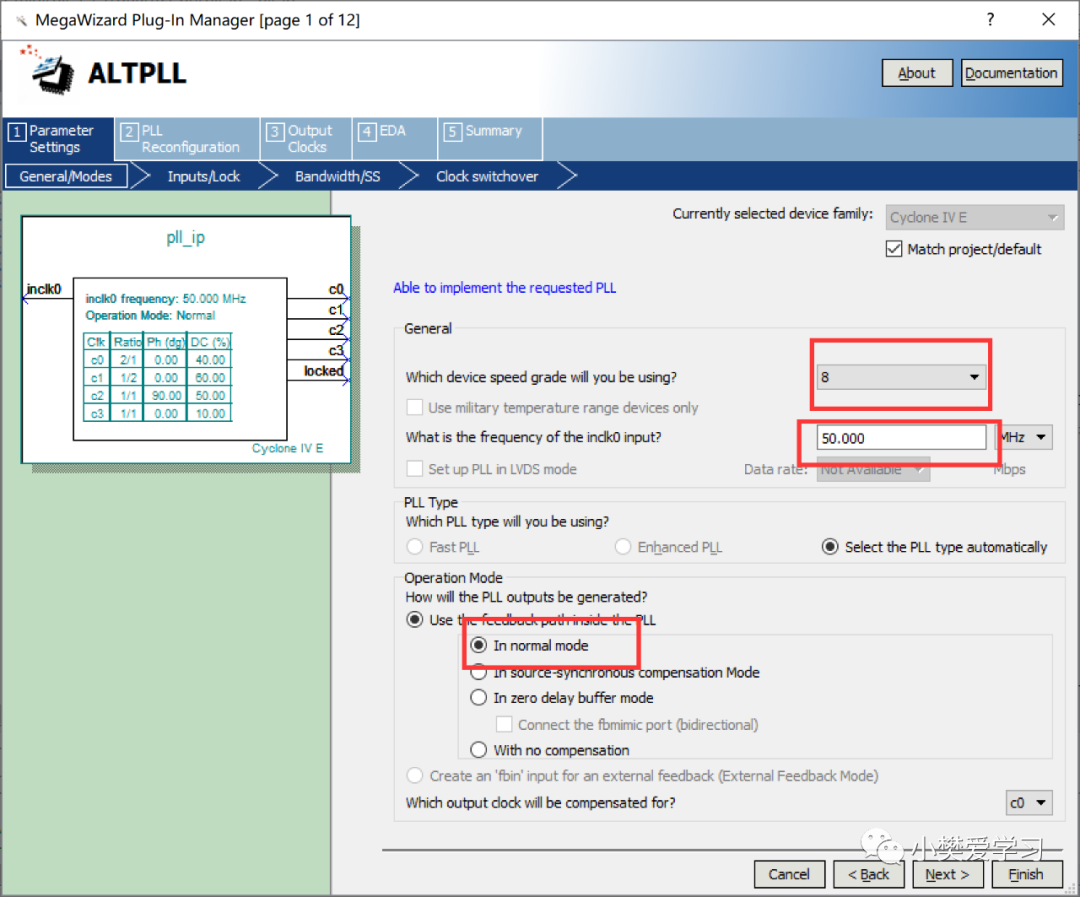

2.在打开弹窗内设定如下三个位置的内容,其中50Mhz是板载的外部时钟的频率,下方选择的模式是默认。

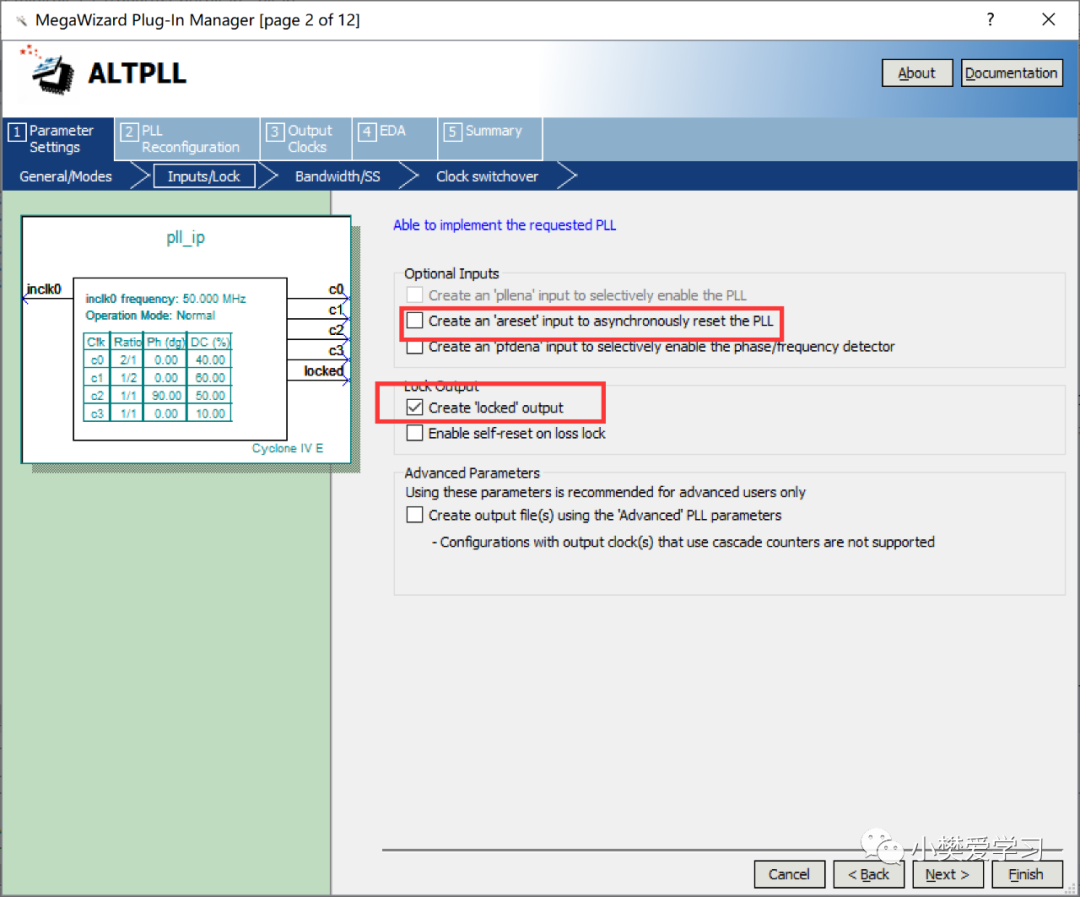

3.选择第二个小选项卡,取消勾选areset,这个一般用不到,而且使用了容易出错。勾选locked,这个输出信号的输出为高电平时,说明输出的时钟有效,否则无效,方便查看。

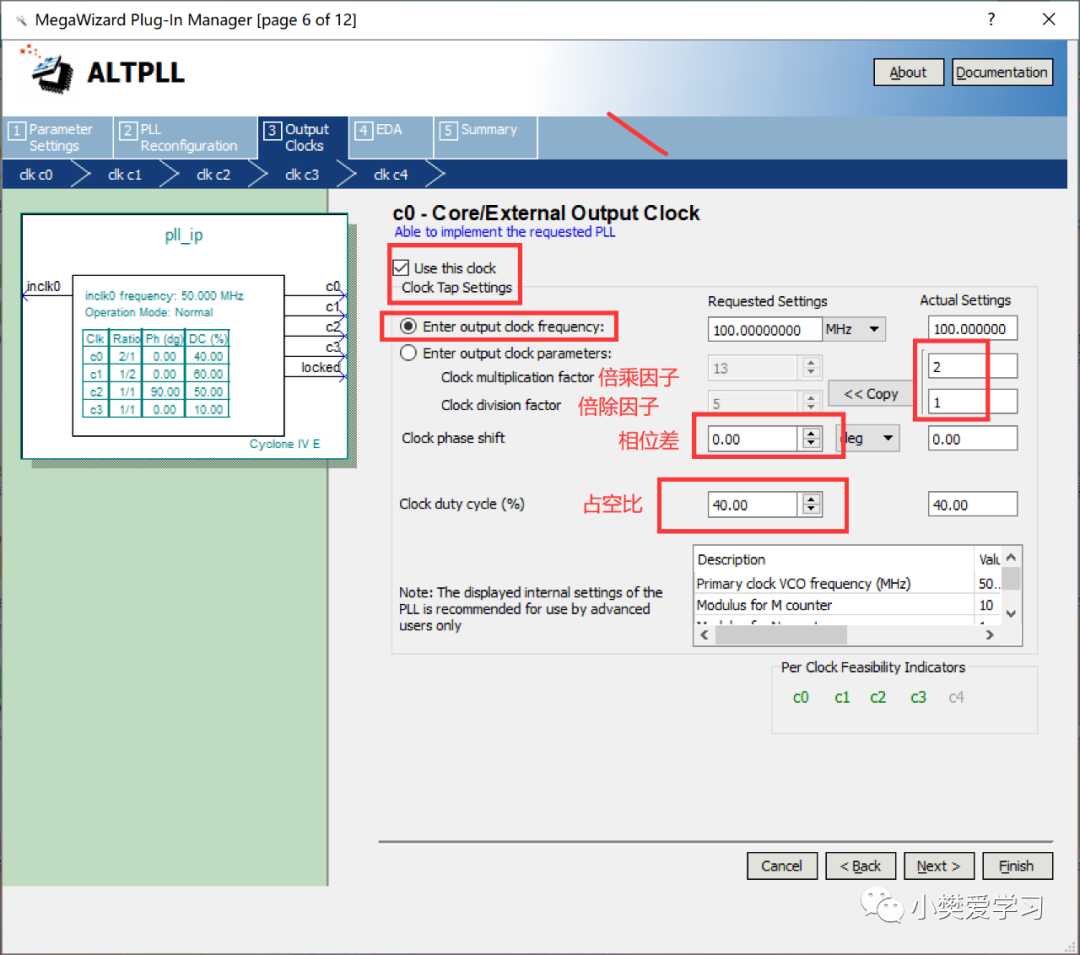

4.选择输出时钟地选项卡,下方有clk0~4,最多可以有五个输出,勾选上第一个红框就是使用该输出时钟。接着勾选上第二个红框,就可以在右方输入需要输出的时钟,这里选择100Mhz,此时右方会自动显示倍乘因子和倍除因子的值,输入的50Mhz÷1×2=100Mhz。也可以勾选第二个红框下方的选项,自行根据所需要的输出时钟的频率修改倍乘因子和倍除因子的值,下方剩下两个红框中对应相位差和占空比的调节。这里我用了四个输出,具体参数可以看左方的框图内显示。

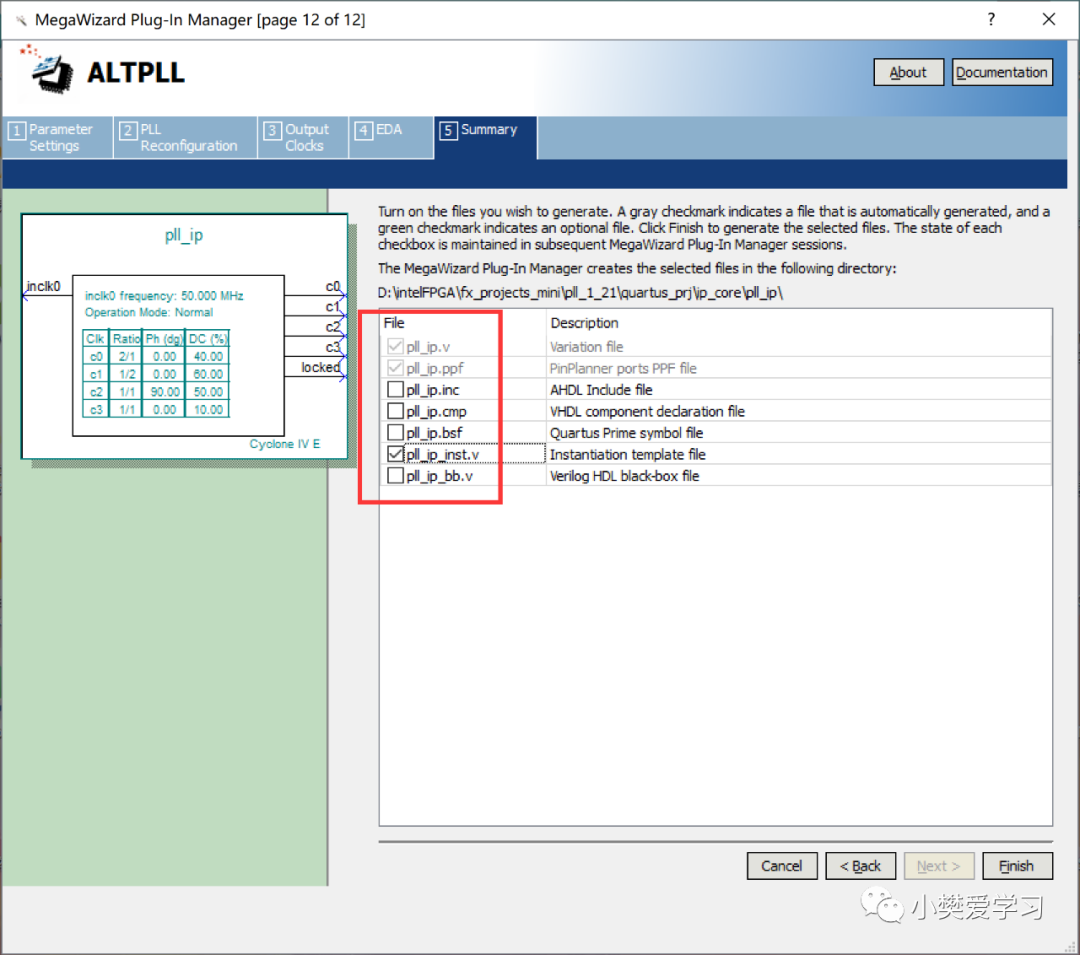

5.在最后一个选项卡中勾选如下图的设置,这些文件的区别我也不懂,记就完事了。其它的选项卡都是高级设置,暂时用不到,全部默认即可,点击生成。

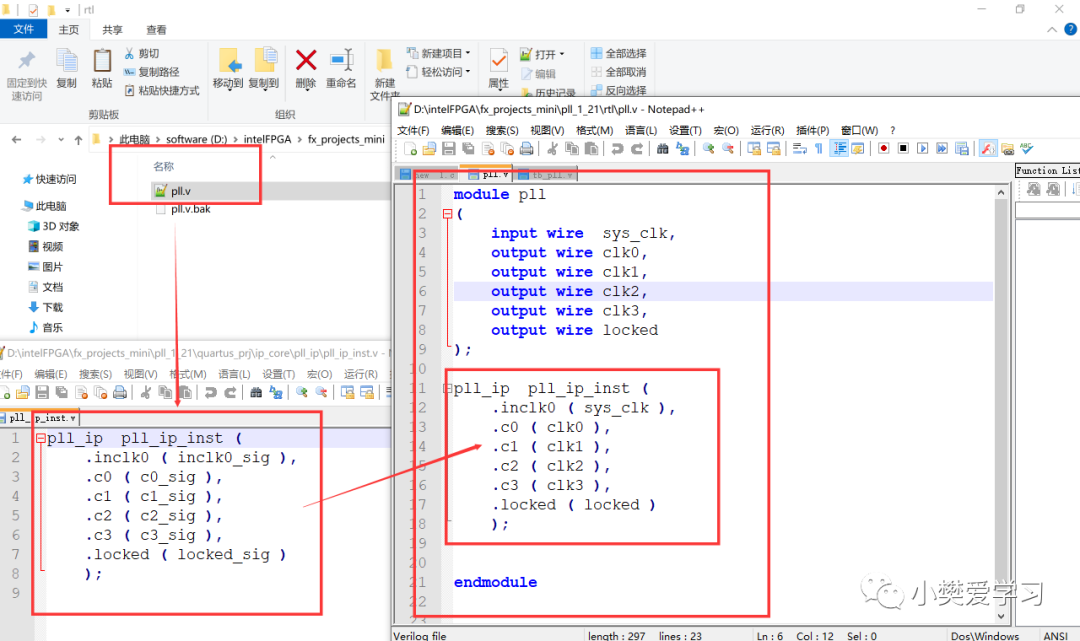

6.在rtl文件夹(用户代码文件夹)里新建一个顶层文件(pll.v文件),将pll_ip实例化,即在顶层文件中调用,再打开quartus软件,添加顶层文件,全编译。

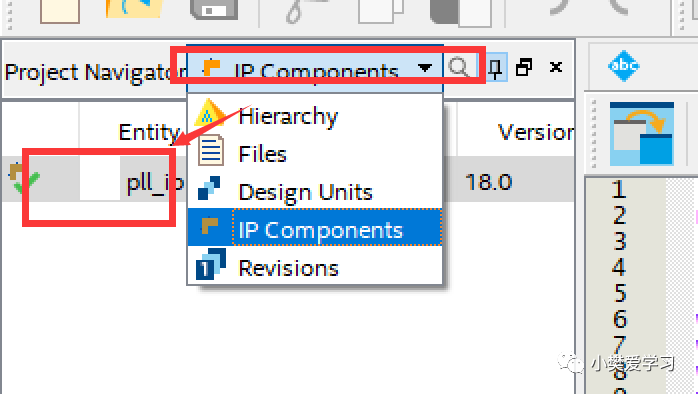

7.如果需要再修改pll_ip的内容,只要在此处点击即可,到此该内容已经结束,下面跑一下仿真。

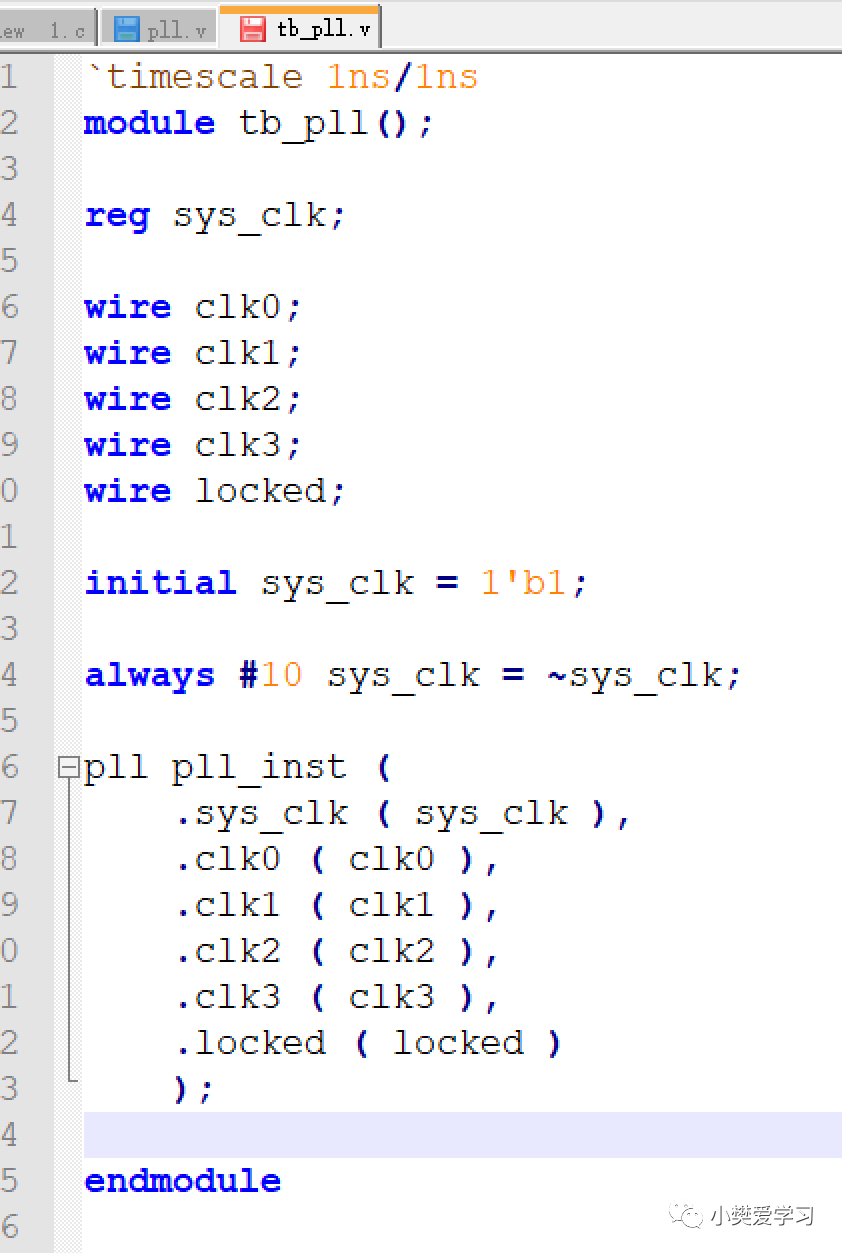

8.新建一个仿真文件,如下图。

9.在quartus软件中添加该仿真文件,全编译。这里补充一个modelsim的安装和破解方法(我的电脑跑仿真一直会有问题,尝试过网上很多方式都不成功,这里放一个我自己电脑能成功的方法)

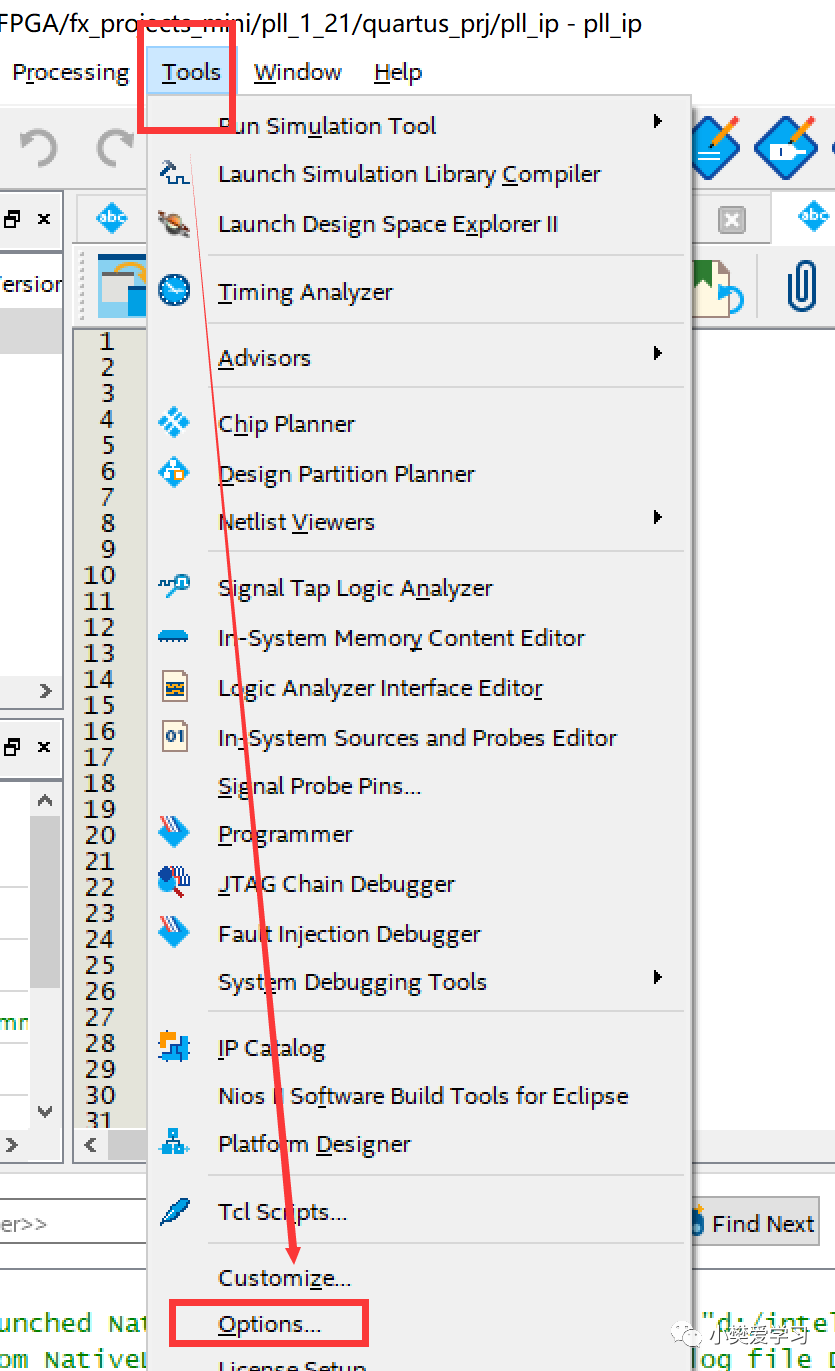

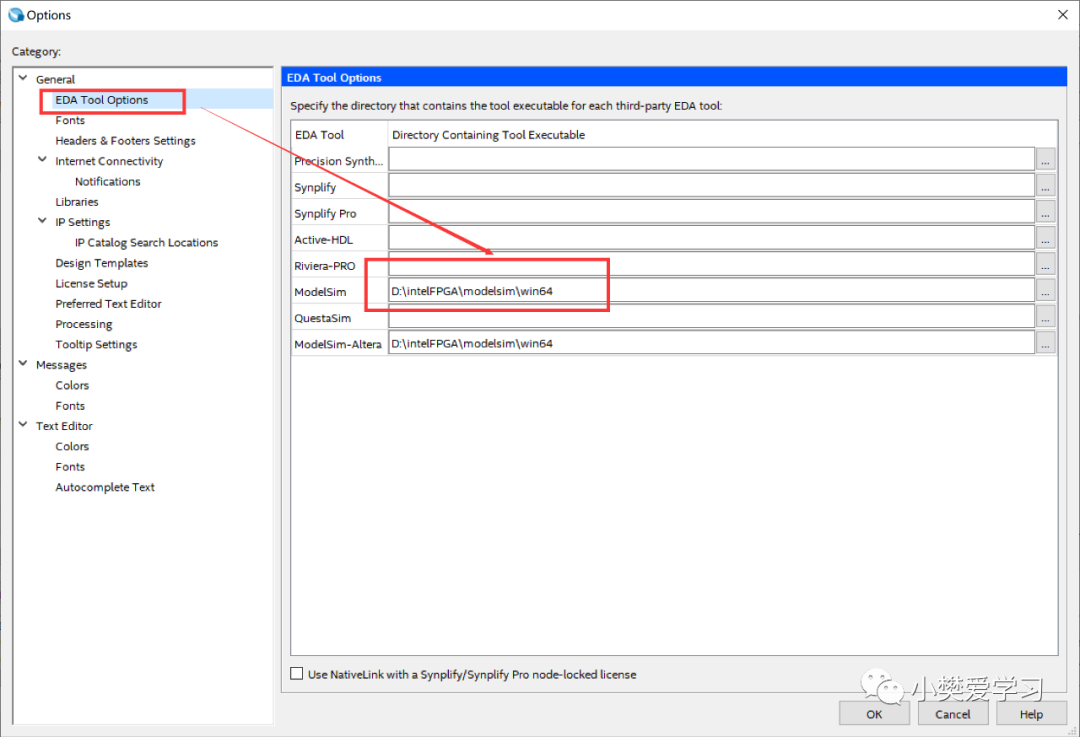

10.破解安装完成后,可以自己点击modelsim软件,能正常打开应该就是成功了。如果和我一样,在quartus运行时去安装并破解modelsim,需要重新启动quartus,否则会失败。接着按照下图的操做进行设置,打开tool—>options,在弹窗内选择EDA Tool Options,在右方红框内选择modelsim的安装目录,要定位到win32或win64。下方有个modelsim_altera ,好像是quartus自带的仿真,但是我尝试配置,一直没成功过,可以忽略。

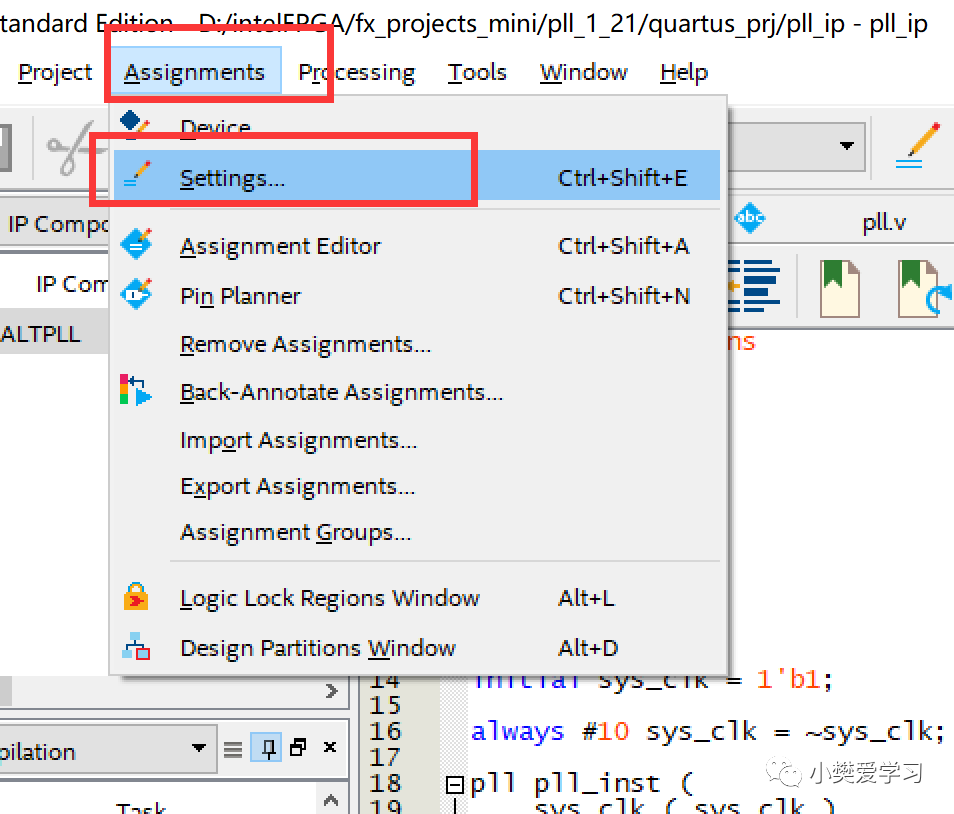

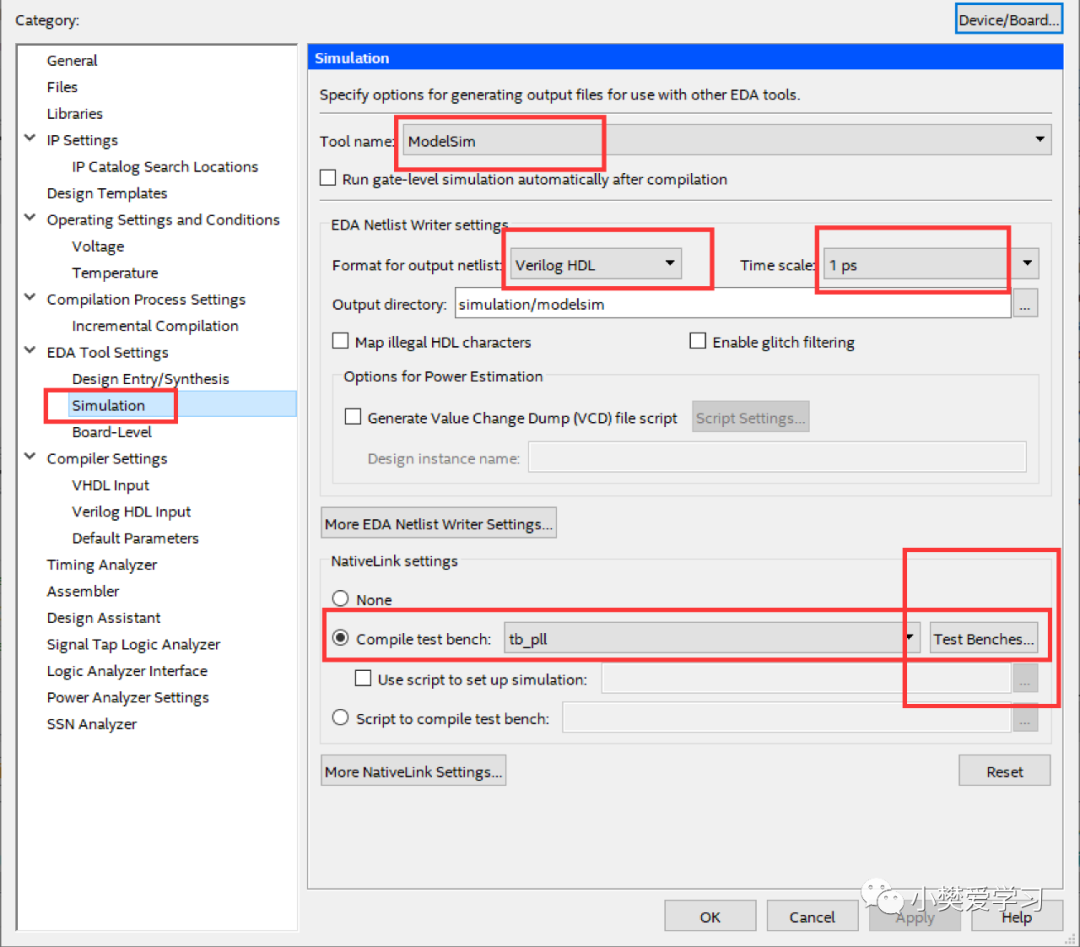

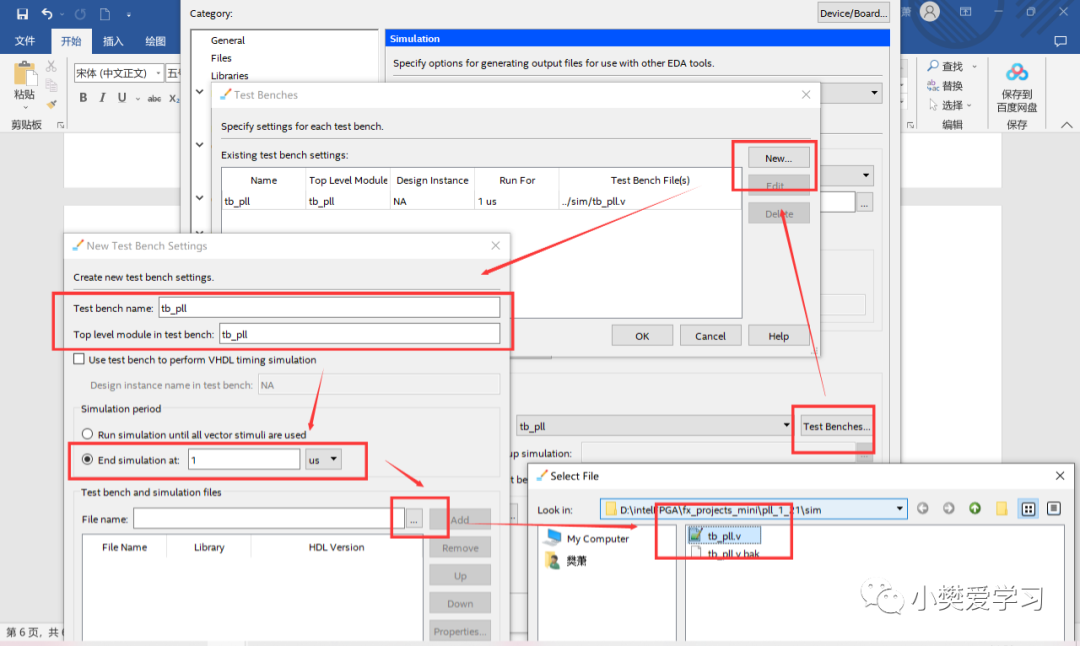

11.仿真软件目录配置完成后,在assignments里选择settings,再按照下方图片内容配置,大部分都是默认的,点击test benches,按下方箭头顺序操做,新建一个仿真,自己命名,然后设置结束时间是1us,最后将写好的仿真文件(tb_pll.v文件)添加进去即可。

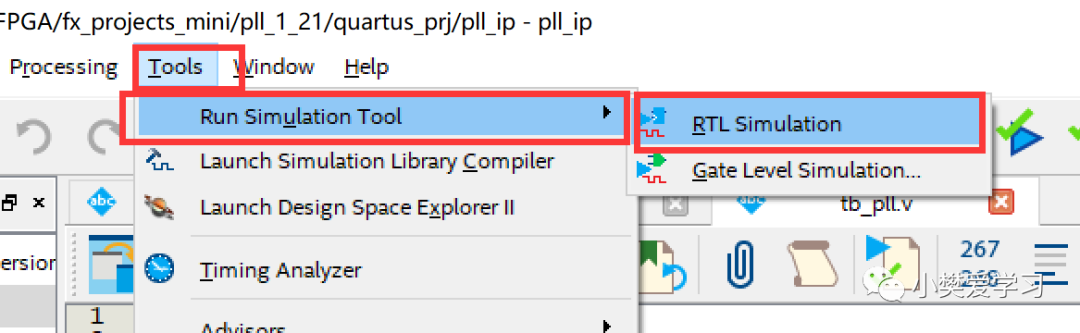

12.点击如下图按钮,开始仿真。

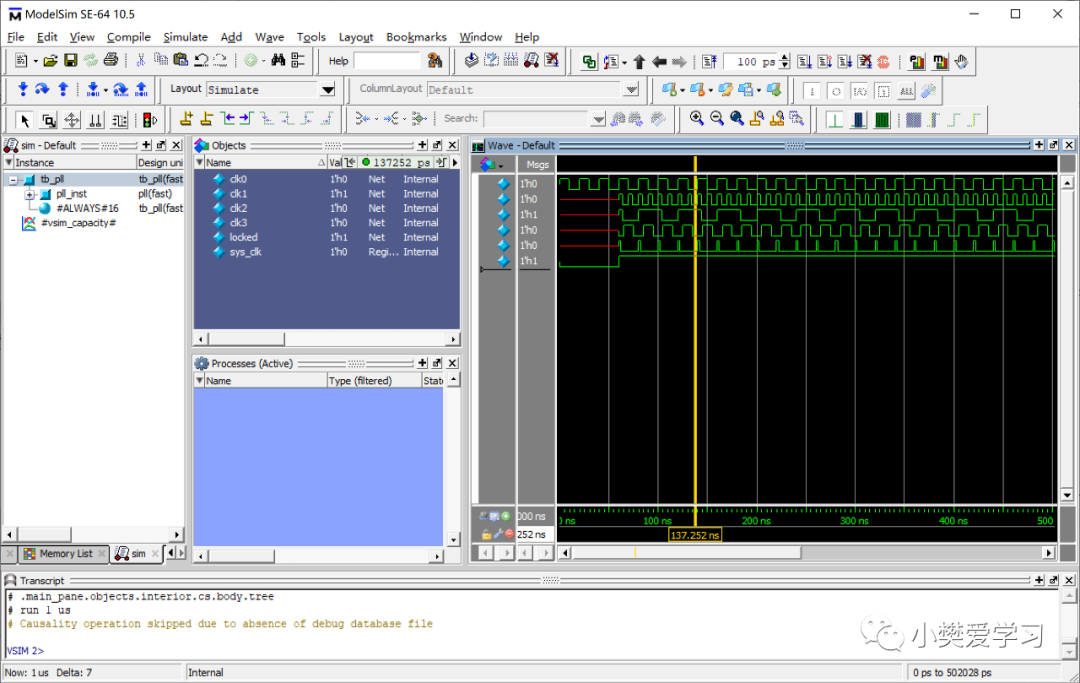

13.仿真结束,出现波形。可以看到波形和之前我在pll_ip核的设定一样,不同的频率,相位,占空比,pll_ip核的调用到此结束。

-

EDA工具

+关注

关注

4文章

268浏览量

31907 -

时钟频率

+关注

关注

0文章

50浏览量

20400 -

高电平

+关注

关注

6文章

153浏览量

21489 -

MODELSIM仿真

+关注

关注

0文章

15浏览量

7335 -

PLL电路

+关注

关注

0文章

92浏览量

6453

发布评论请先 登录

相关推荐

XILINX FPGA IP之MMCM PLL DRP时钟动态重配详解

【锆石A4 FPGA试用体验】IP核之PLL(一)新建IP核

xilinx FPGA的FFT IP核的调用

勇敢的芯伴你玩转Altera FPGA连载63:PLL IP核创建于配置

【正点原子DFPGL22G开发板体验】内置IP核使用体验-PLL之呼吸灯

QUARTUS II中IP核的调用方法(图文详解)

Xilinx Vivado的使用详细介绍(3):使用IP核

lattice DDR3 IP核的生成及调用过程

PLL_IP核的调用流程详解

PLL_IP核的调用流程详解

评论