什么是 ASIC 设计

ASIC 设计是开发复杂电子系统的过程。该系统可制造成特殊用途的半导体设备,通常用于大批量应用或具有严格的功耗、性能和尺寸限制的应用。ASIC 系统设计人员使用高级语言并通过仿真和可视化来开发和评估算法。

许多系统设计人员使用 MATLAB 和 Simulink 作为高级环境来指定 ASIC 设计的算法。通过将这些产品与第三方 EDA 工具结合使用,系统设计人员可以与 ASIC 硬件设计人员协作,使用 MATLAB 和 Simulink 对数字和模拟/混合信号 (AMS) ASIC 设计的新算法内容进行建模、仿真、优化和实现。

建模

您可以选择使用 MATLAB 或 Simulink 开发硬件实现的算法来开始 ASIC 设计开发。MATLAB 提供了一种基于语言且无时间限制的简洁建模环境,而 Simulink 提供了一种支持使用多速率模块图、状态机和其他建模结构进行图形化建模的环境。MATLAB 代码可以整合到 Simulink 模型中,因此,您可以从 MATLAB 顺利过渡到 Simulink 工作流。

通过将 Simulink 模型与现有代码整合并使用 HDL 协同仿真对其进行仿真,来增强该模型以使其适用于 ASIC 设计。为了评估模拟组件与数字组件之间的交互,可以添加 Mixed-Signal Blockset 中的组件,如锁相环 (PLL) 与数据转换器(ADC 和 DAC)。

针对代码生成优化模型

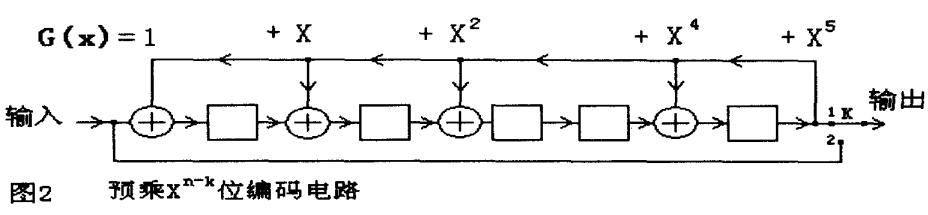

接下来,您可以基于硬件实现优化 ASIC 设计模型。算法开发人员可与 ASIC 硬件设计人员协作优化模型的硬件架构。首先是审查 MATLAB 代码或 Simulink 模型,验证它是否适用于 HDL 代码生成。我们有 300 多个 Simulink 模块和 200 多个 MATLAB 函数支持生成 HDL 代码,您可以使用它们来构建模型。其次是使用 Fixed-Point Designer 将浮点模型转换为定点模型,以减少设计的面积和功耗。通过将 Simulink 模型从基于帧的模型转换为流式模型,可以针对 ASIC 设计进一步优化这些模型。

针对 HDL 代码生成进行基于模型的优化

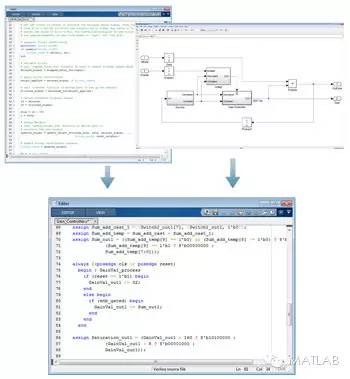

通过 ASIC 架构,可以采用多种方式从功耗-性能-面积 (PPA) 方面优化实现。系统设计人员可以与 ASIC 硬件设计人员协作,使用 HDL Coder 从 MATLAB 代码或 Simulink 模型生成可综合的 Verilog 和 VHDL 代码。HDL Coder 提供了一系列优化选项,可以帮助设计人员尽可能实现 ASIC 设计的最高性能。这些选项包括时钟速率自动优化、资源共享和流水线化,它们可以显著减少实现设计所需的逻辑数量。HDL Coder 还支持为多速率设计和触发子系统生成 HDL 代码。

HDL 和 SystemC 代码生成

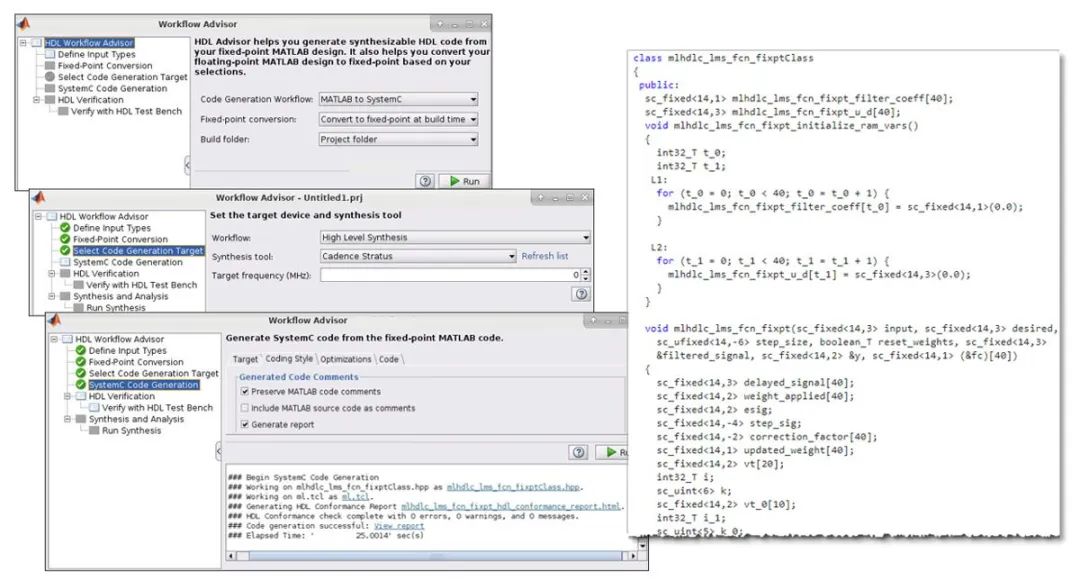

使用 HDL Coder,您可以按照引导式工作流完成 ASIC 设计的 HDL 代码生成过程。HDL Coder 可检查 MATLAB 和 Simulink 模型与 HDL 代码生成的兼容性,支持自定义生成的 HDL 代码,生成预综合报告,并生成 HDL 测试平台。

您可以通过 MATLAB 函数生成可综合的 SystemC 代码。生成的 SystemC 代码可作为 Cadence Stratus 高级综合工具的输入。通过将 Stratus HLS 与 Genus 逻辑综合解决方案和 Joules RTL 功耗解决方案相集成,ASIC 设计人员可以提前了解 ASIC 设计实现的功耗-性能-面积 (PPA)。

使用 HDL Coder,可以从 MATLAB 代码生成 SystemC、Verilog/SystemVerilog 或 VHDL 代码。

FPGA 原型构建

在 ASIC 设计中,FPGA 原型构建是一种通过硬件测试来评估算法实现的常见方法。HDL Coder 可与 AMD Xilinx、Intel 和 Microchip 设备的 FPGA 工作流相集成,在开发板上实现快速原型构建。

使用 FPGA 开发板对原型设计进行 FPGA 在环测试。

-

FPGA

+关注

关注

1635文章

21832浏览量

608117 -

asic

+关注

关注

34文章

1209浏览量

121125 -

仿真

+关注

关注

50文章

4152浏览量

134421 -

Verilog

+关注

关注

28文章

1355浏览量

110790 -

代码

+关注

关注

30文章

4857浏览量

69482

原文标题:什么是 ASIC 设计?利用仿真及 Verilog、VHDL 和 SystemC 代码生成进行 ASIC 设计

文章出处:【微信号:MATLAB,微信公众号:MATLAB】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何在FPGA上实现HDL代码完成MATLAB转换

如何在ModelSim下用SystemC的做验证?

如何使用FPGA器件进行ASIC原型设计

ASIC和FPGA有什么区别

ASIC,ASIC是什么意思

ASIC到FPGA的原型验证代码转换技术

MathWorks推出基于MATLAB生成HDL代码的产品

并行CRC电路HDL代码的快速生成

FPGA vs ASIC

什么是ASIC?ASIC中的“特定应用”是什么意思?

什么是ASIC设计?使用HDL和SystemC代码生成进行ASIC设计

什么是ASIC设计?使用HDL和SystemC代码生成进行ASIC设计

评论