在 SPI 中,主机可以选择时钟极性和时钟相位。在空闲状态期间,CPOL 为设置时钟信号的极性。空闲状态是指传输开始时 CS

为高电平且在向低电平转变的期间,以及传输结束时 CS 为低电平且在向高电平转变的期间。CPHA 为选择时钟相位。

根据CPHA位的状态,使用时钟上升沿或下降沿来采样和/或移位数据。主机必须根据从机的要求选择时钟极性和时钟相位。根据 CPOL 和 CPHA

位的选择,有四种SPI 模式可用。表1显示了这 4 种 SPI 模式。

表1.通过CPOL和CPHA选择SPI模式

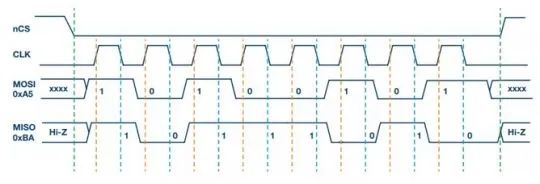

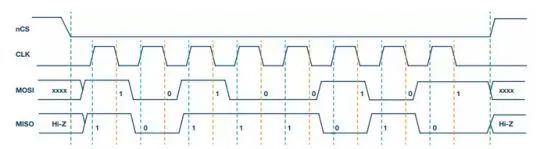

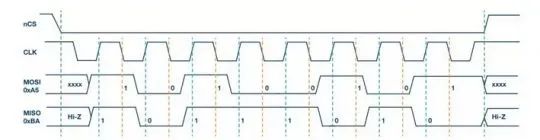

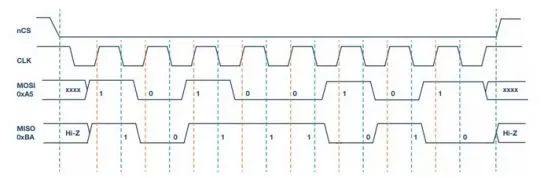

图2至图5显示了四种SPI模式下的通信示例。在这些示例中,数据显示在MOSI和MISO线上。传输的开始和结束用绿色虚线表示,采样边沿用橙色虚线表示,移位边沿用蓝色虚线表示。请注意,这些图形仅供参考。要成功进行SPI通信,用户须参阅产品数据手册并确保满足器件的时序规格。

图2给出了SPI模式0的时序图。在此模式下,时钟极性为0,表示时钟信号的空闲状态为低电平。此模式下的时钟相位为0,表示数据在上升沿采样(由橙色虚线显示),并且数据在时钟信号的下降沿移出(由蓝色虚线显示)。

图2. SPI模式0,CPOL = 0,CPHA = 0:CLK空闲状态 = 低电平,数据在上升沿采样,并在下降沿移出

图3给出了SPI模式1的时序图。在此模式下,时钟极性为0,表示时钟信号的空闲状态为低电平。此模式下的时钟相位为1,表示数据在下降沿采样(由橙色虚线显示),并且数据在时钟信号的上升沿移出(由蓝色虚线显示)。

图3. SPI模式1,CPOL = 0,CPHA = 1:CLK空闲状态 = 低电平,数据在下降沿采样,并在上升沿移出

图4. SPI模式2,CPOL = 1,CPHA = 1:CLK空闲状态 = 高电平,数据在下降沿采样,并在上升沿移出

图4给出了SPI模式2的时序图。在此模式下,时钟极性为1,表示时钟信号的空闲状态为高电平。此模式下的时钟相位为1,表示数据在下降沿采样(由橙色虚线显示),并且数据在时钟信号的上升沿移出(由蓝色虚线显示)。

图5. SPI模式3,CPOL = 1,CPHA = 0:CLK空闲状态 = 高电平,数据在上升沿采样,并在下降沿移出

图5给出了SPI模式3的时序图。在此模式下,时钟极性为1,表示时钟信号的空闲状态为高电平。此模式下的时钟相位为0,表示数据在上升沿采样(由橙色虚线显示),并且数据在时钟信号的下降沿移出(由蓝色虚线显示)。

-

通信

+关注

关注

18文章

6114浏览量

136768 -

SPI

+关注

关注

17文章

1731浏览量

92836

发布评论请先 登录

相关推荐

时钟相位噪声测量中杂散的讨论及应用

SPI通信的四种方式 FPGA的SPI从机实现方案

SPI中的极性CPOL和相位CPHA介绍

浅谈SPI总线

HbirdV2-SoC中如何配置QSPI1和QSPI2的时钟极性CPOL和时钟相位CPHA?

AD7606 SPI通信的时钟极性和时钟相位要求是什么?

根据时钟极性和时钟相位的不同,SPI有四个工作模式

如何生成和使用杂散进行测试:时钟相位噪声探讨资料下载

为什么杂散会带来额外抖动?时钟相位噪声测量解析资料下载

SPI时钟极性和时钟相位

SPI时钟极性和时钟相位

评论