来源:《半导体芯科技》杂志

美国麻省理工学院的研究人员对一种低温生长技术进行革新,将二维材料集成到硅电路上,为制造出更密集、更强大的芯片铺平了道路。新方法涉及直接在硅芯片顶部生长二维过渡金属二硫化物材料层,而在传统方法上这通常需要可能会损坏硅的高温。

据国外媒体报道,麻省理工学院(MIT)工程师使用一种新的低温生长和制造技术将二维(2D)材料直接集成到硅电路上,通过这种技术有望实现更密集和更强大的芯片。

新兴的人工智能应用,比如生成自然人类语言的聊天机器人,需要更密集、更强大的计算机芯片。但半导体芯片传统上是用块状材料制成的,这些材料是方形的三维(3D)结构,因此通过堆叠多层晶体管来实现更密集的集成非常困难。

MIT的研究人员开发了一种低温生长工艺,可将二维材料直接集成到硅芯片上,从而实现密度更高、功能更强大的半导体。该技术绕过了之前与高温和材料转移缺陷相关的挑战。它还缩短了生长时间,并允许在更大的8英寸晶圆上形成均匀的层,使其成为商业应用的理想选择。

由超薄二维材料制成的半导体晶体管,每个只有大约三个原子的厚度,可以堆叠起来制造更强大的芯片。MIT研究人员开发的新技术,可以直接在完全制造的硅芯片上有效且高效地“生长”二维过渡金属二硫化物(transition metal dichalcogenide, TMD)材料层,进而实现更密集的集成。

研究生Jiadi Zhu拿着一块带有二硫化钼薄膜的8英寸CMOS晶圆。右边是研究人员专门开发的外延生长炉,使他们能够使用不损坏晶圆的低温工艺在晶圆上“生长”一层二硫化钼。

将二维材料直接生长到硅CMOS晶圆上是一项重大挑战,因为该过程通常需要大约600摄氏度的温度,而硅晶体管和电路在加热到400摄氏度以上时可能会损坏。现在,MIT研究人员的跨学科团队已经开发出一种不会损坏芯片的低温生长工艺。该技术允许将二维半导体晶体管直接集成在标准硅电路之上。

过去,研究人员是先在其他地方生长二维材料,然后将它们转移到芯片或晶圆上。这通常会导致缺陷,从而影响最终器件和电路的性能。此外,在晶圆级顺利转移材料变得极其困难。相比之下,这种新工艺在整个8英寸晶圆上生长出了平滑、高度均匀的薄层。

新技术还能够显著减少生长这些材料所需的时间。以前的方法生长单层二维材料需要超过一天的时间,而新方法可以在不到一个小时的时间内在整个8英寸晶圆上生长出均匀的TMD材料层。

由于其速度快和均匀性高,这项新技术使研究人员能够成功地将二维材料层集成到比之前展示的更大的表面上。这使得他们的方法更适合用于商业应用,其中8英寸或更大的晶圆是关键。

“使用二维材料是提高集成电路密度的有效方法。我们正在做的就像建造一座多层建筑。如果你只有一层,这是传统的情况,它不会容纳很多人。但是随着楼层的增加,大楼将容纳更多的人,从而可以实现令人惊叹的新事物。由于我们正在研究异质集成,我们将硅作为第一层,然后我们可以将多层二维材料直接集成在上面,”电气工程和计算机科学研究生,关于这项新技术的论文的共同主要作者Jiadi Zhu说。该论文于2023年4月27日发表在《Nature

Nanotechnology》杂志上。Zhu与共同主要作者、麻省理工学院博士后Ji-Hoon Park共同撰写了这篇论文;论文通讯作者Jing Kong,电气工程与计算机科学(EECS)教授,电子研究实验室成员;论文作者还有EECS教授兼微系统技术实验室(MTL)主任Tomás Palacios;以及麻省理工学院、麻省理工学院林肯实验室、橡树岭国家实验室和爱立信研究中心的其他人。

1具有巨大潜力的超薄材料

研究人员关注的二维材料二硫化钼具有柔韧性、透明性,并具有强大的电子和光子特性,使其成为半导体晶体管的理想选择。它由夹在两个硫(化物)原子(层)之间的单原子钼层组成。

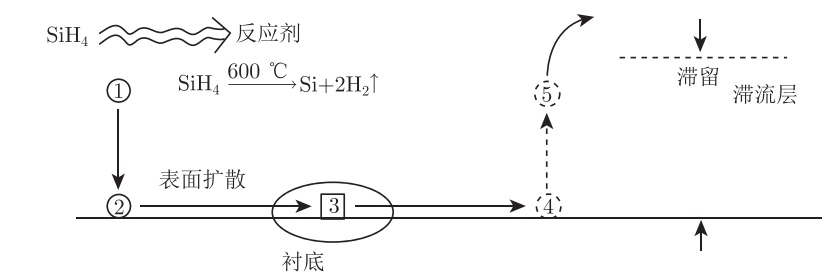

在表面上以良好的均匀性生长二硫化钼薄膜通常是通过称为金属有机化学气相沉积(MOCVD)的工艺完成的。六羰基钼和二亚乙基硫是含有钼原子和硫原子的两种有机化合物,它们在反应室内蒸发并被加热,在那里它们“分解”成更小的分子。然后它们通过化学反应连接起来,在表面形成二硫化钼链。

但是分解这些被称为前体的钼化合物和硫化合物需要550摄氏度以上的温度,而当温度超过400摄氏度时,硅电路就会开始受到损害。

因此,研究人员开始跳出框框思考——他们为金属有机化学气相沉积(MOCVD)工艺设计并建造了一个全新的外延生长炉。

炉子的烘箱由两个腔室组成,前部是低温区,放置硅片,后部是高温区。汽化的钼和硫前体被泵入生长炉。钼停留在低温区域,温度保持在400摄氏度以下——热到足以分解钼前体,但又不会热到损坏硅芯片。

硫前体流入高温区域,并在那里分解。然后它流回低温区,在那里发生在晶圆表面生长二硫化钼的化学反应。“你可以把分解想象成制作黑胡椒——你有一整粒胡椒,然后把它磨成粉末。所以,我们在高温区粉碎和研磨辣椒,然后粉末流回低温区,”Zhu解释道。

2更快的生长和更好的均匀性

该工艺有一个问题:硅电路通常将铝或铜作为顶层,因此芯片可以在安装到印刷电路板上之前连接到封装或载体。但是硫会导致这些金属硫化,就像一些金属暴露在氧气中会生锈一样,这会破坏它们的导电性。研究人员通过首先在芯片顶部沉积一层非常薄的钝化材料来防止硫化。然后他们可以打开钝化层再进行连接。

他们还将硅片垂直放置到炉子的低温区域,而不是水平放置。通过垂直放置,两端都不会太靠近高温区域,因此晶圆的任何部分都不会被热量损坏。此外,钼和硫气体分子在撞击垂直芯片时会旋转,而不是流过水平表面。这种旋转循环效应促进了二硫化钼的生长,并提高了材料的均匀性。

除了产生更均匀的沉积层外,他们的方法也比其他MOCVD工艺快得多。他们可以在不到一个小时的时间内生长一层,而通常MOCVD生长过程至少需要一整天。MIT使用最先进的MIT.Nano设施,他们能够在8英寸硅晶圆上生长高度均匀的优质材料,这对于需要更大晶圆的工业应用尤为重要。

“通过缩短生长时间,该工艺效率更高,并且可以更容易地集成到工业制造中。此外,这是一种与硅兼容的低温工艺,有助于将二维材料进一步推进到半导体行业中。”Zhu说。

未来,研究人员希望微调他们的技术,并用它来生长多层堆叠的二维晶体管。此外,他们还想探索这种低温生长工艺在柔性表面(如聚合物、纺织品甚至纸张)的应用。这可能会实现将半导体集成到衣服或笔记本等日常用品上。

这项工作在单层二硫化钼材料的合成技术方面取得了重要进展,在8英寸规模的低温生长能力使这种材料与硅CMOS技术的后端集成成为可能,为其未来的更多电子应用铺平了道路。

这项工作部分由MIT士兵纳米技术研究所、国家科学基金会综合量子材料中心、爱立信、MITRE、美国陆军研究办公室和美国能源部资助。该项目也得到TSMC University Shuttle的支持。

-

芯片

+关注

关注

463文章

54422浏览量

469241 -

半导体

+关注

关注

339文章

31236浏览量

266490

发布评论请先 登录

85页PPT,看懂芯片半导体的封装工艺!

集成电路制造中薄膜生长工艺的发展历程和分类

芯源半导体安全芯片技术原理

BW-4022A半导体分立器件综合测试平台---精准洞察,卓越测量

【新启航】碳化硅外延片 TTV 厚度与生长工艺参数的关联性研究

【「AI芯片:科技探索与AGI愿景」阅读体验】+半导体芯片产业的前沿技术

台阶仪应用 | 半导体GaAs/Si异质外延层表面粗糙度优化

高精度半导体冷盘chiller在半导体工艺中的应用

从原理到应用,一文读懂半导体温控技术的奥秘

苏州芯矽科技:半导体清洗机的坚实力量

揭秘半导体电镀工艺

新型低温生长工艺改变半导体芯片技术

新型低温生长工艺改变半导体芯片技术

评论