PCIe接口全称PCI Express,由PCI-SIG组织发布的用于替代PCI总路线的新一代高速串行总线与接口。PCIe接口版本经历PCIe1.0、PCIe2.0、PCIe3.0,目前主流应用的PCIe接口为PCIe2.0。

PCIe作为高速差分串行接口用于替代PCI单端并行接口,在进行物理层信号测试时,不同于PCI利用同步时钟(33MHz)进行数据读写,PCIe通过高达2.5Gbps的速率对信号进行收发操作,硬件测试时主要关注其参考时钟(100MHz)和差分收发信号(2.5Gbps或5Gbps)。

PCIe接口硬件特性

PCIe规范非常复杂,规格分为基本标准(Base)和CEM标准(Card Electromechanical),前者主要描述PCIe的基本结构、协议、链路层、物理层以及软件接口,适用于所有PCIe接口,后者重点关注PCIe接口在PCI桌面/服务器中的应用策略,包括各种类型的插卡的定义与使用等,两个规范互有关联,要理解芯片级互连的硬件(电气)特性要求,需要深入分析两个规范。

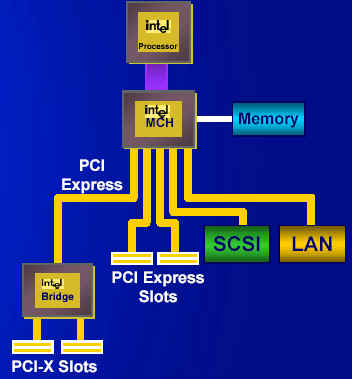

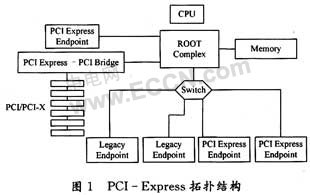

PCIe基本拓扑结构

PCIe CEM标准规范根据PCIe器件的位置将PCIe分成三种拓扑结构:

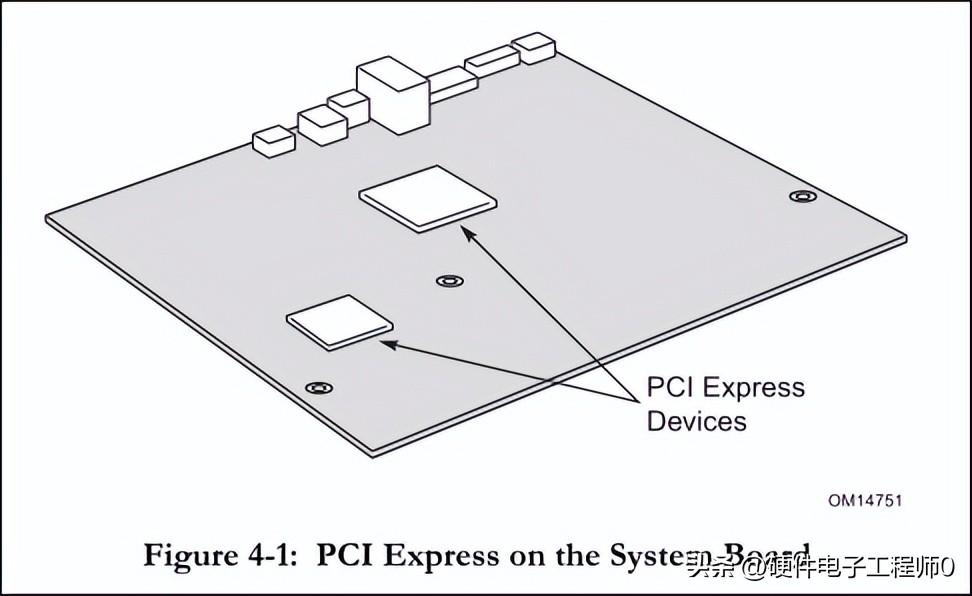

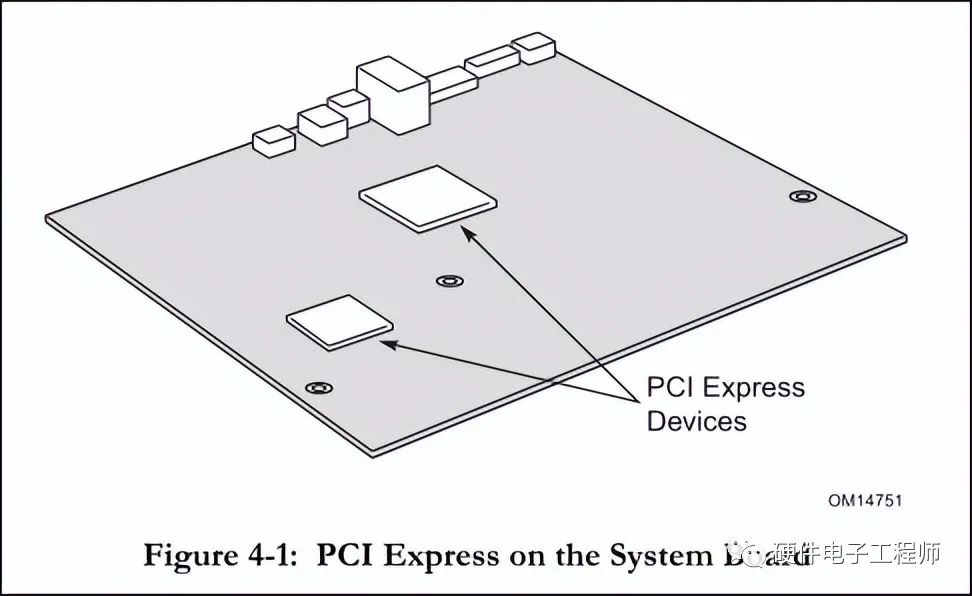

芯片级互连,PCIe器件在同一系统单板上;

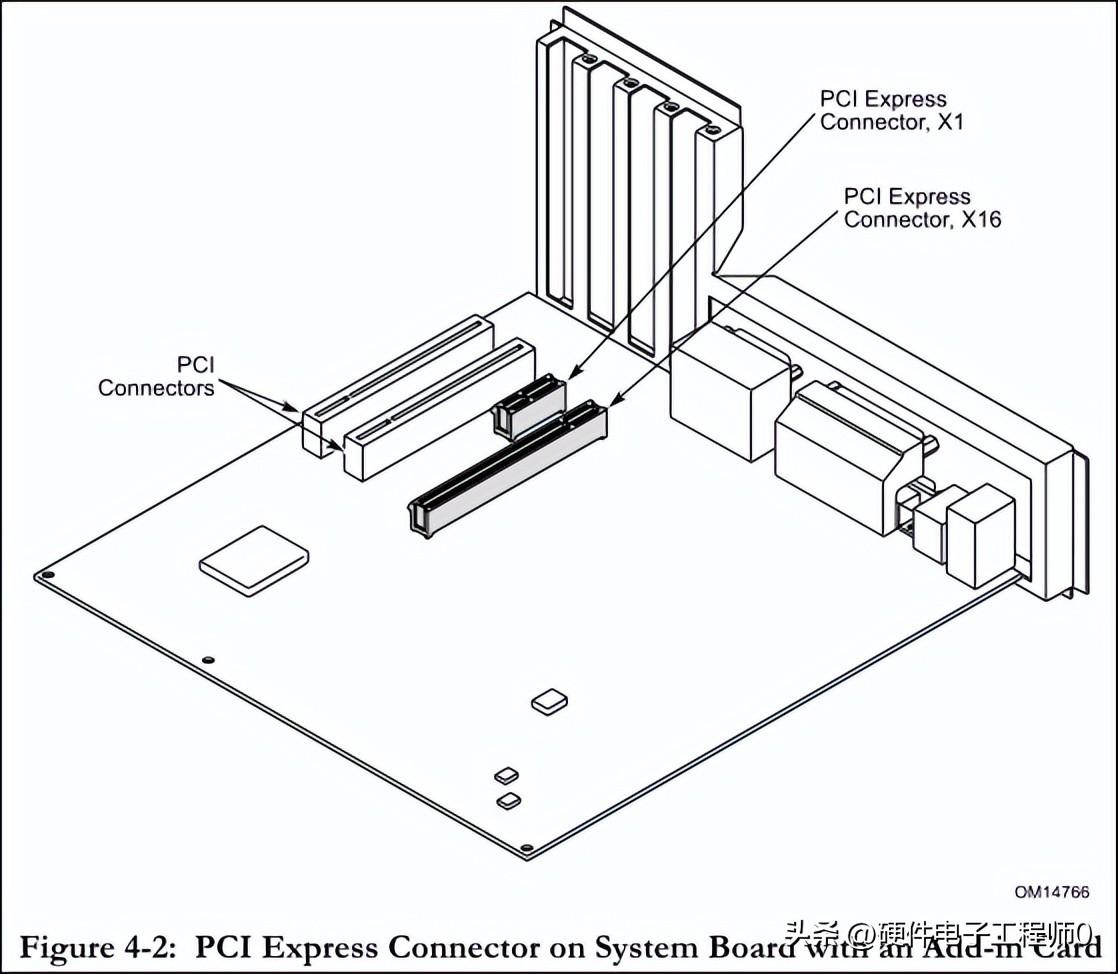

插卡级互连,PCIe器件通过插卡与系统板插座互连,系统板和插卡上各有一个PCIe器件;

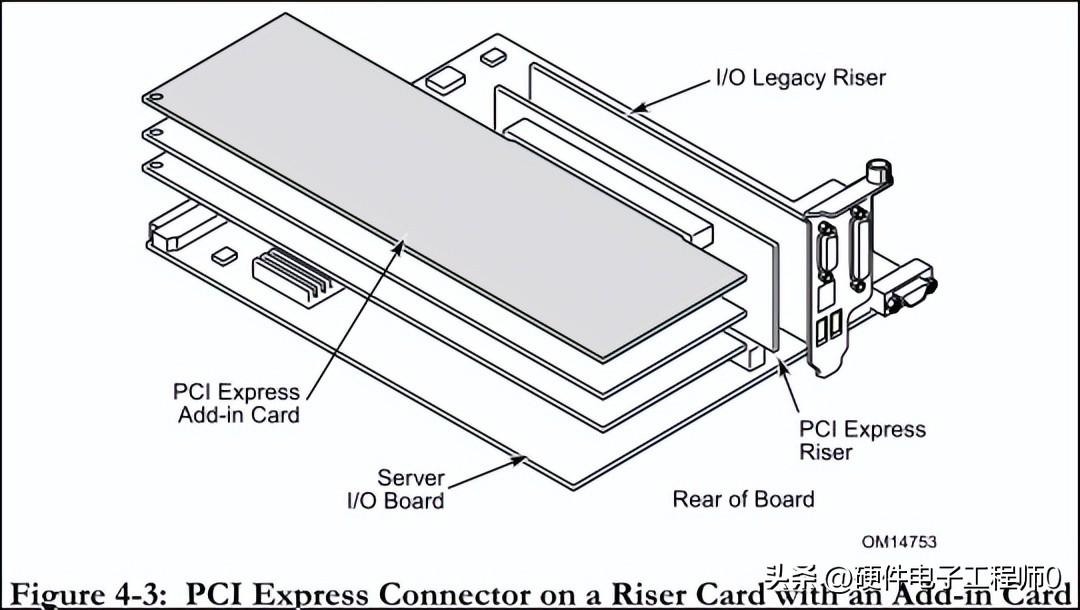

背板级互连,PCIe器件分别在两种插卡,通过背板(或系统板)上插座完成PCIe互连。

图2.1‑1、芯片级互连

图2.1‑2、插卡级互连

图2.1‑3、背板级互连

其中,插卡级互连与背板级互连多用于PC或服务器的主板,PCIe CEM规范对其硬件电气特性描述非常详细,且主流的高端示波器厂家都提供了一致性测试夹具和软件,这里不作描述。

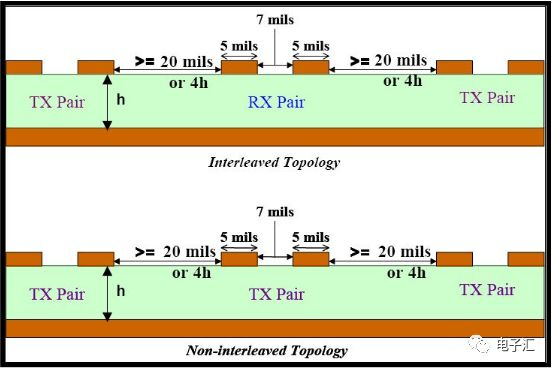

芯片级互连PCIe电气特性

芯片级PCIe互连在通信产品中应用极为广泛,目前几乎完全替代PCI接口,成为了芯片互连的标准接口。芯片级PCIe接口通过是1 lane的差分串行线连接,主要信号包括复位、参考时钟Refclk以及收发差分串行SerDes信号,复位信号较为简单,PCIe规范没有特殊要求,本文重点讨论Refclk与SerDes信号要求与测试。

参考时钟Refclk±

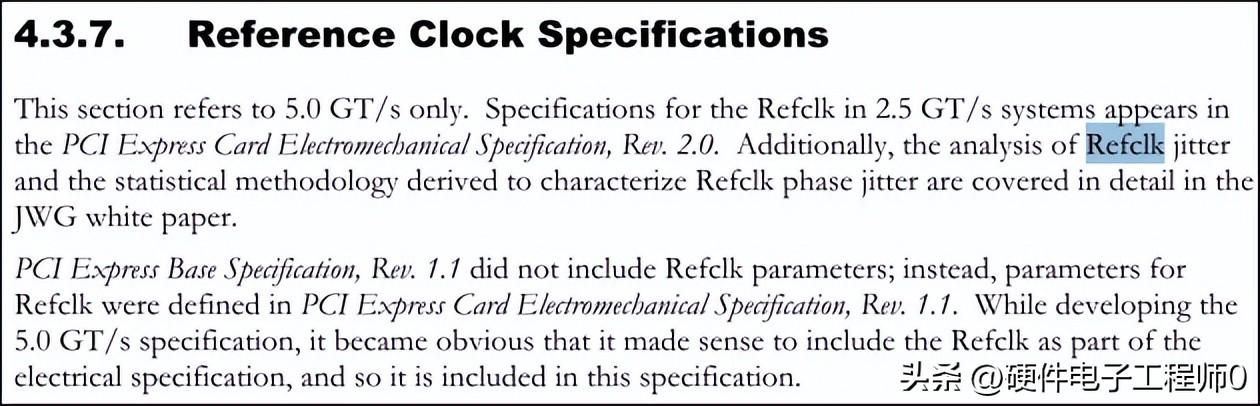

关于PCIe参考时钟, PCIe Base 2.1规范中没有对Refclk的电气特性有明确说明,只是在4.3.7章节说明对于2.5GT/s系统的时钟参考《PCE Express Card Electromechanical Specification, Rev.2.0》。

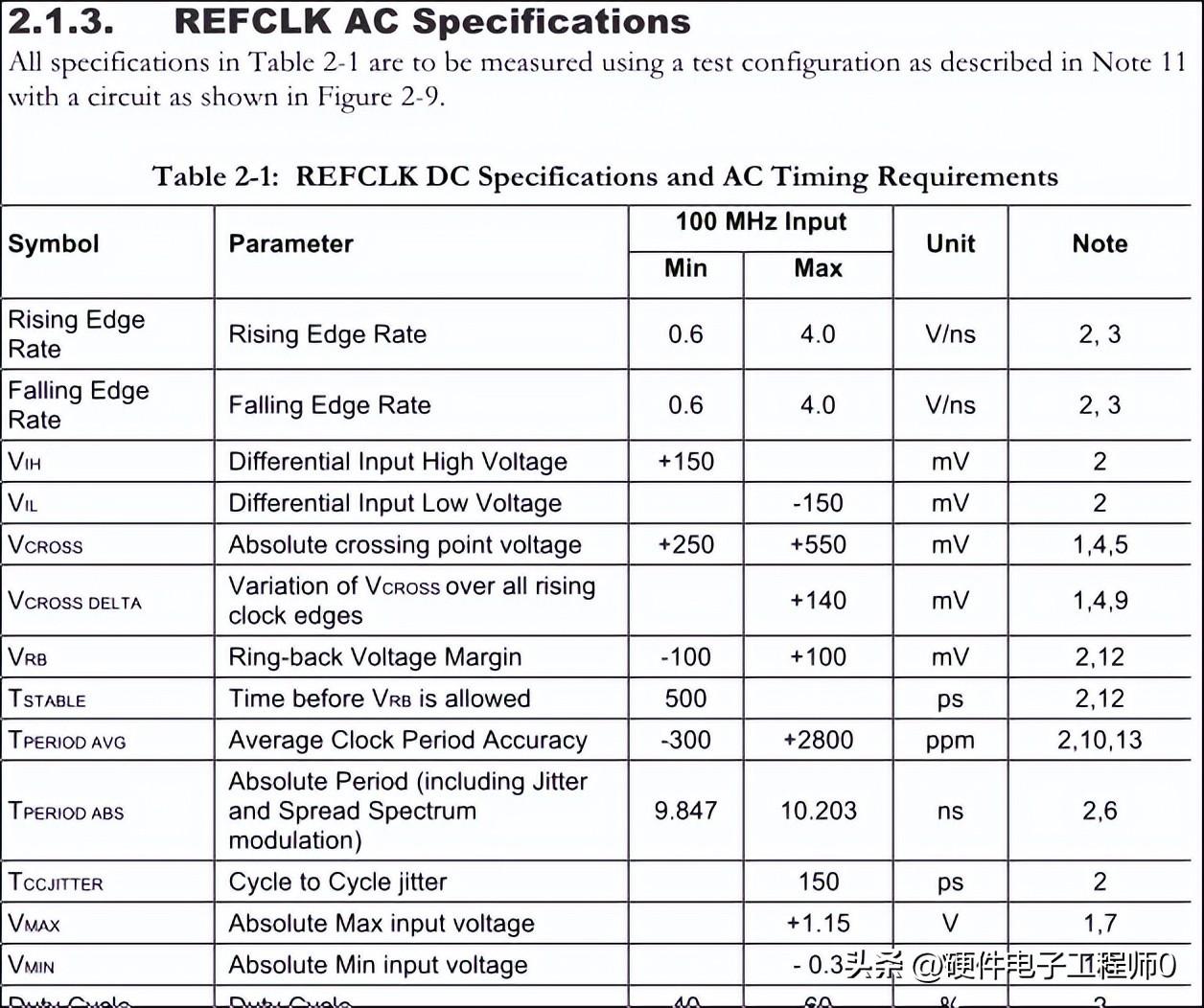

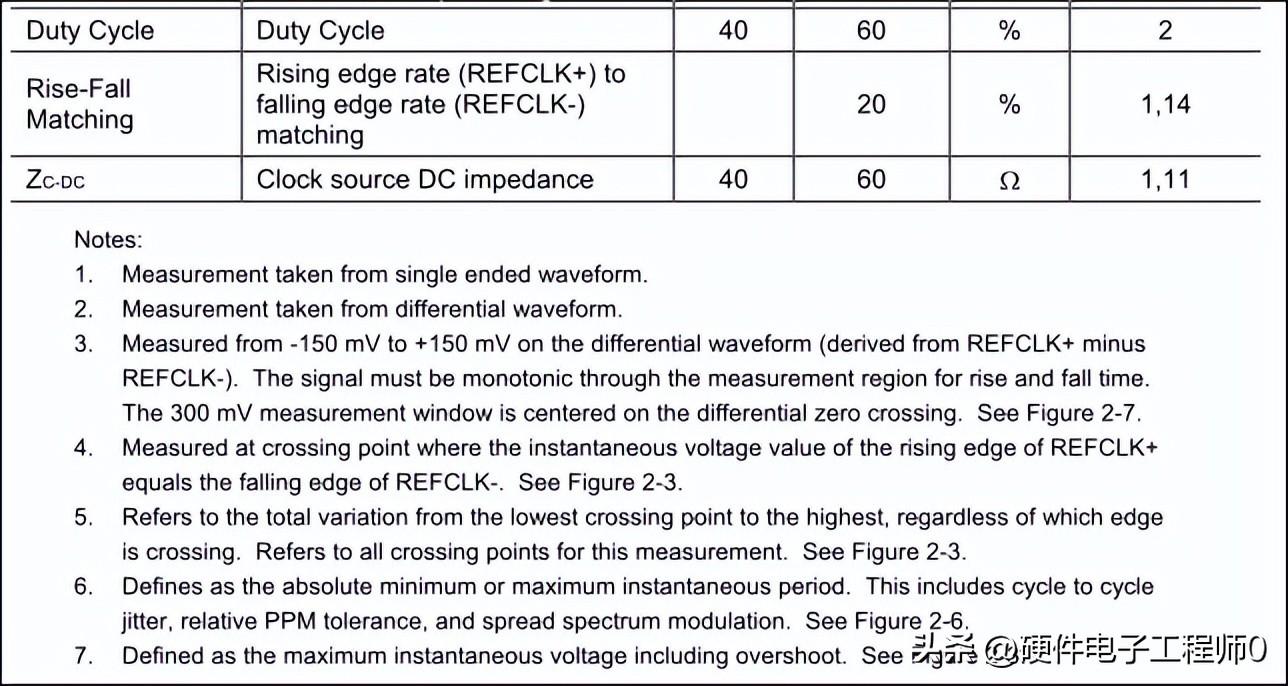

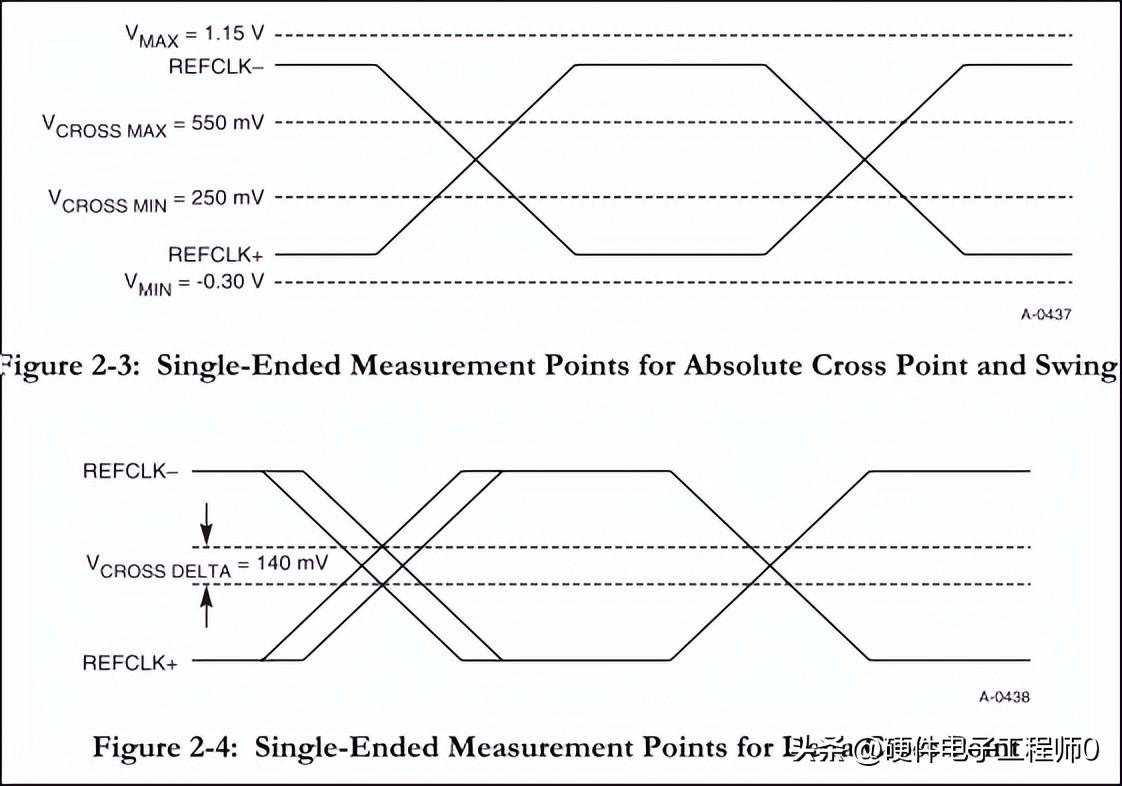

查看PCIe card 2.0,对差分时钟Refclk±有明确的电气特性要求,如下所示。

从规范的要求来看,对输入参考时钟重点关注时钟频率(周期)、占空比、上升/下降沿、差分输入高低电平、边沿单调性、单端交叉点电平以及周期间抖动等指标。

对于PCIe参考时钟的使用,一般也有两结构Common-clock bus与 Source synchronous bus,前者是通过晶振或差分时钟驱动器同时给PCIe的主(master)从(slave)器件提供参考时钟,后者是同主器件驱动时钟给从器件接收。对于common-clock模式,主从器件的参考时钟都要测试,PCIe接口中的参考时钟只是作为基准时钟使用,对差分信号没有同步要求,所以不需要测试主从时钟的时延skew,对source syschronous模式,只需要在从器件测试参考时钟的接收端即可。

高速串行差分信号RXD±与TXD±

PCIe2.X支持5GT/s和2.5GT/s两种速率,对于板内芯片级互连来说,驱动端(Transimitter)信号质量不是最重要的,重点关注接收端(Receiver)信号的电气特性要求。

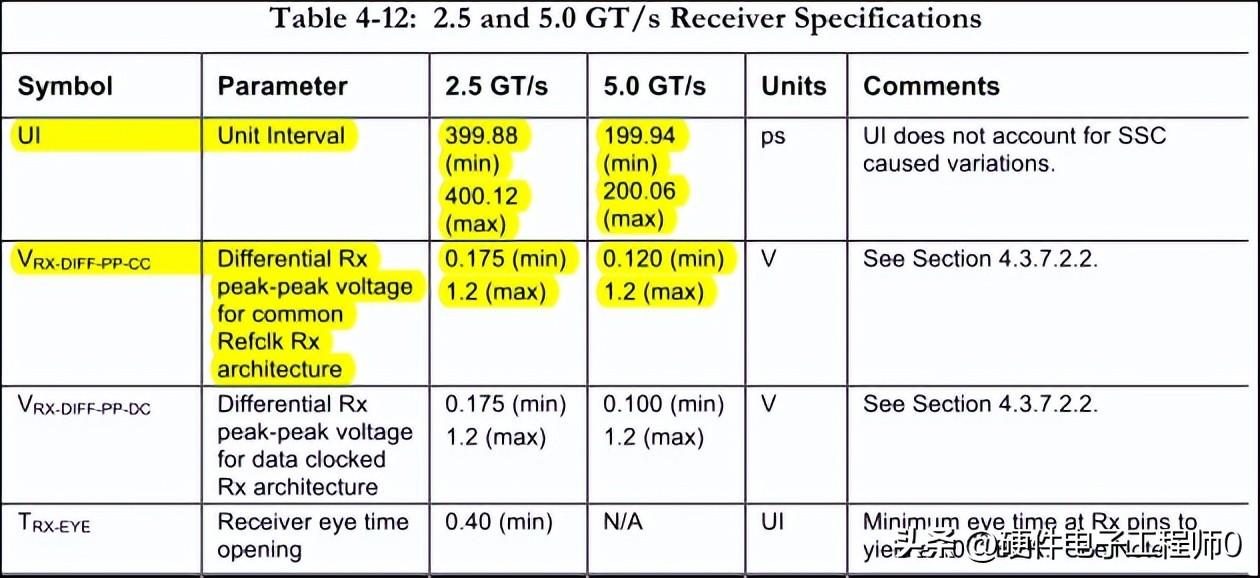

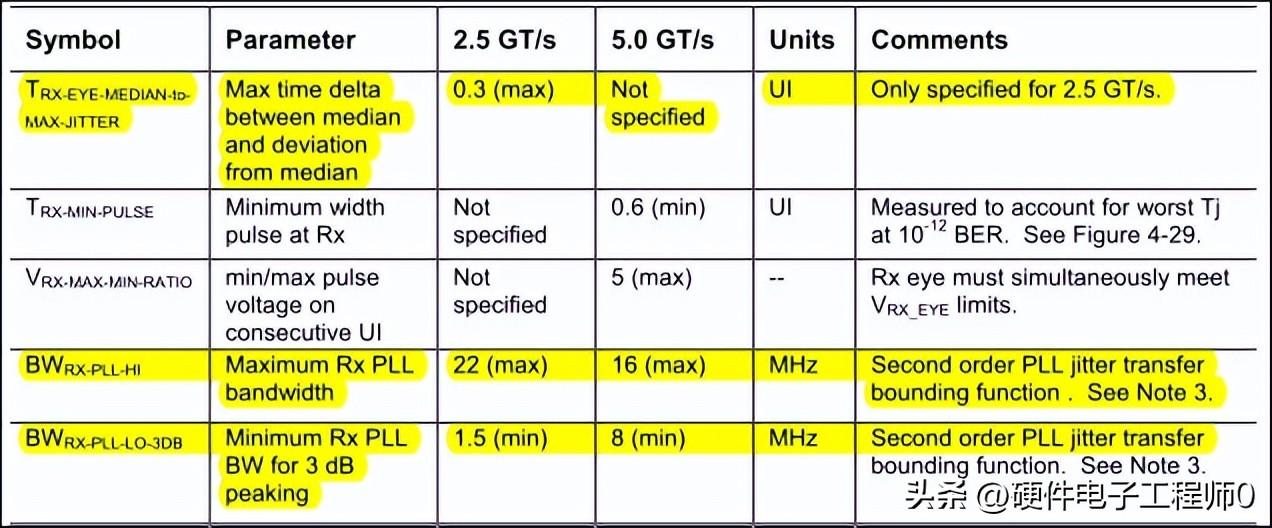

PCIe Base 2.1中第4.3.4章节对Receiver的电气特性有了明确要求。

从规范得出,Receiver重点关注差分信号眼图和抖动,对应VRX-DIFF-PP-CC和TRX-EYE-MEDIAN-to-MAX-JITTER,同时,测试时需要设计Rx PLL的带宽。

PCIe接口硬件测试

根据上述章节对芯片级PCIe硬件电气特性的描述,PCIe硬件测试主要包括PCIe参考时钟测试和PCIe接收端信号测试。

PCIe参考时钟测试

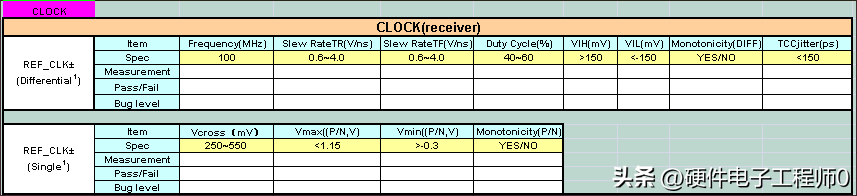

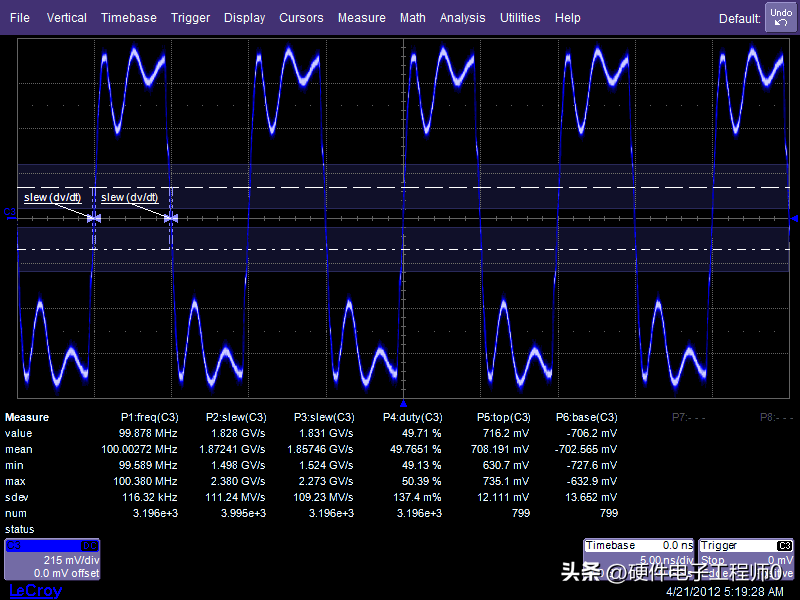

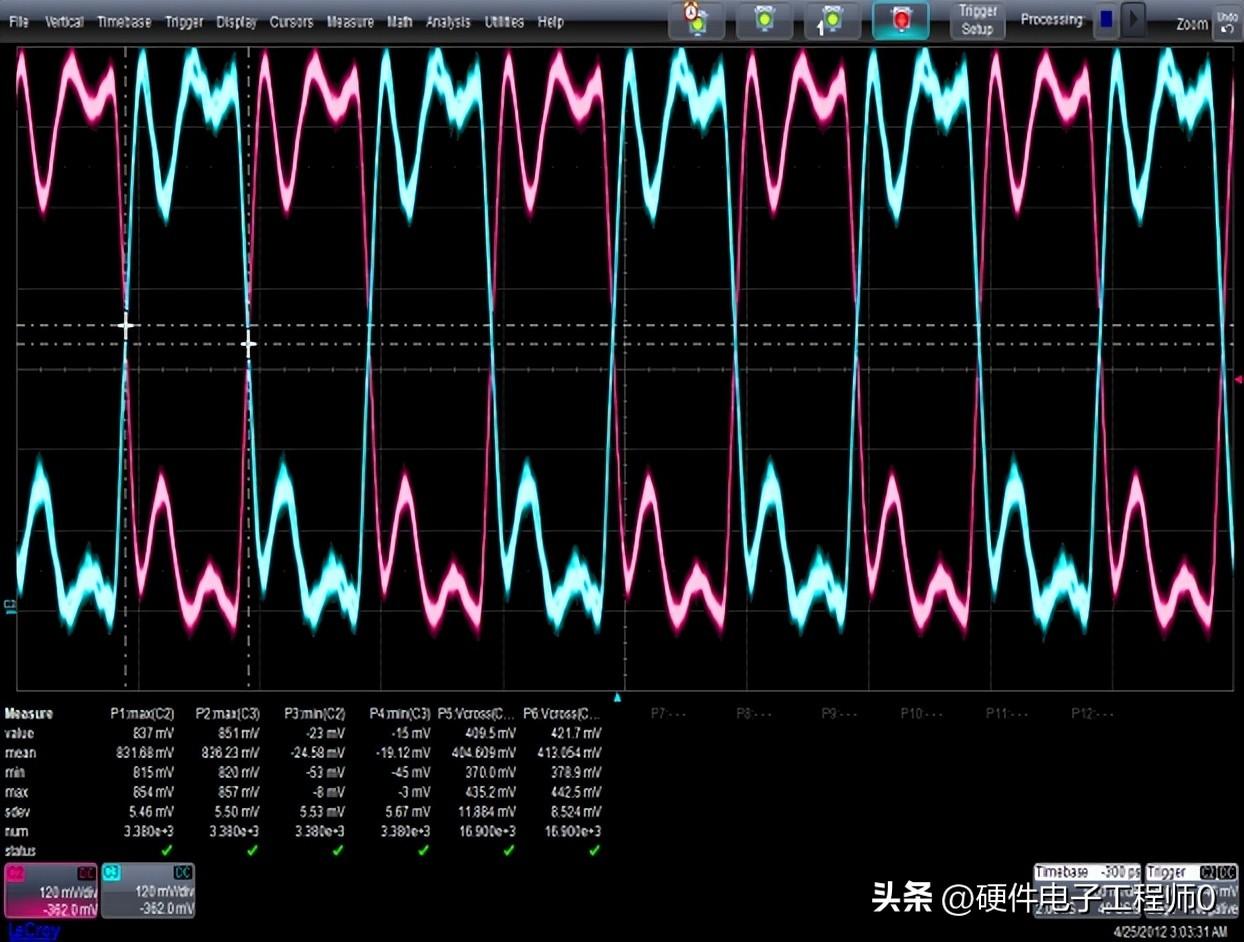

PCIe参考时钟Refclk±为差分信号,分单端测试和差分测试,前者使用两个有源单端探头同时测试参考时钟的正负端,测量交叉点电压VCROSS,同进观察边沿单调性;后者利用差分探头测试差分时钟的正负端,测量项包括频率、上升/下降沿斜率、差分高低电平、点空比、边沿单调性、时钟抖动等。具体测量项见下表所示。

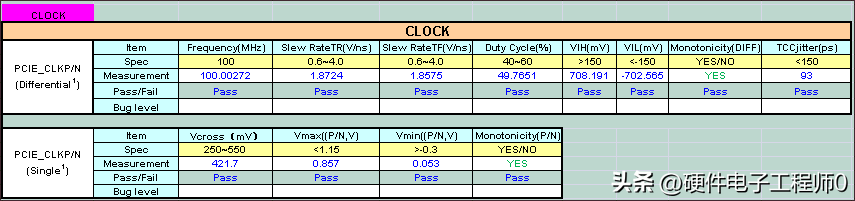

表3.1‑1、PCIe参考时钟特性测试数据

PCIe接收端信号测试

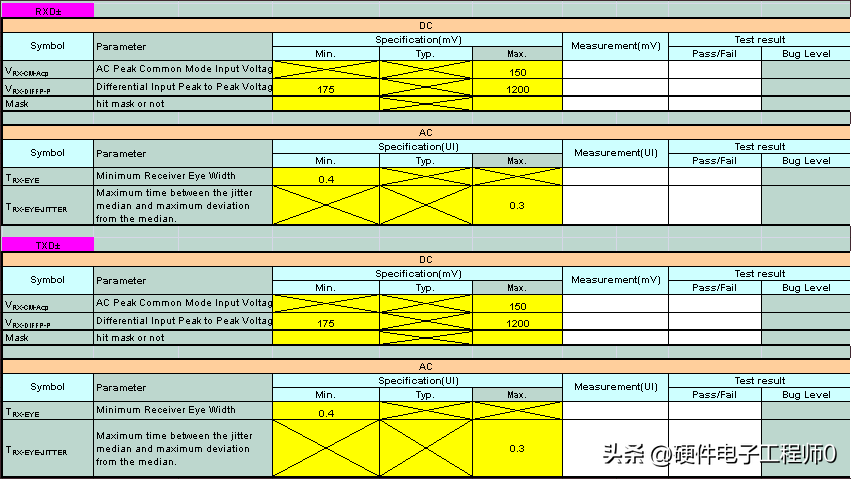

PCIe串行数据信号测试,只测试信号的接收端(RXD在master端测试,TXD在slave端测试),测试点尽量靠近芯片引脚处。因PCIe规范对数据交叉电压没有要求,数据信号主要是测试差分信号,单端不作测试。测试内容分为眼图和抖动,测试时注意示波器PLL带宽的设置。

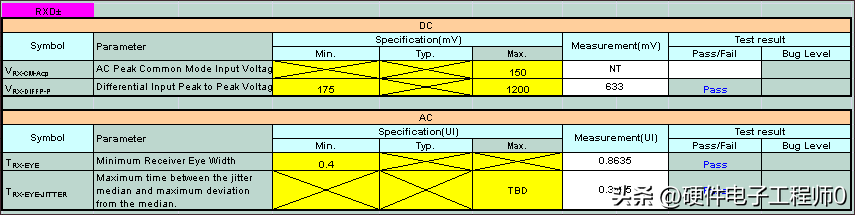

表3.2‑1、PCIe数据测试数据

PCIe硬件测试案例

以某通信产品为例,测试其WIFI与CPU互连的PCIe接口信号,测试结果如下。

表3.3‑1、 PCIe时钟测试数据

表3.3‑2、 PCIe时钟测试数据

图3.3‑1、PCIe参考时钟测试波形

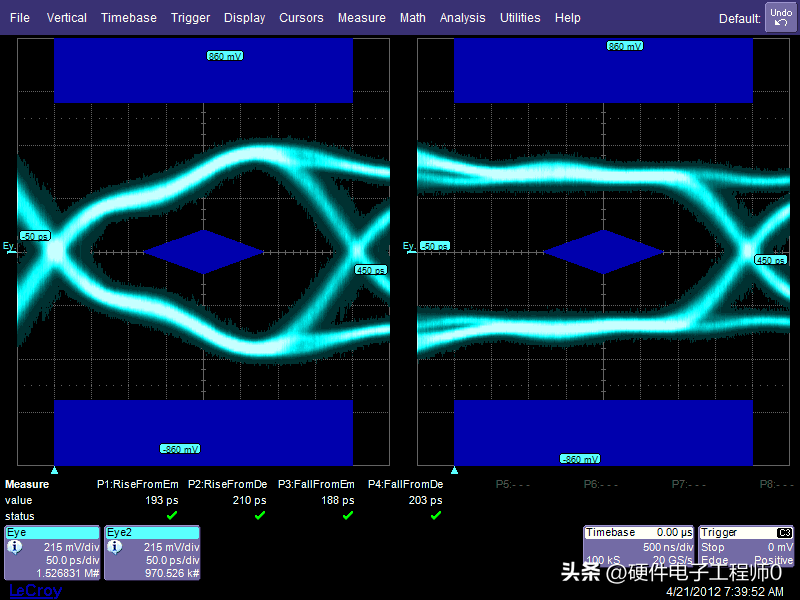

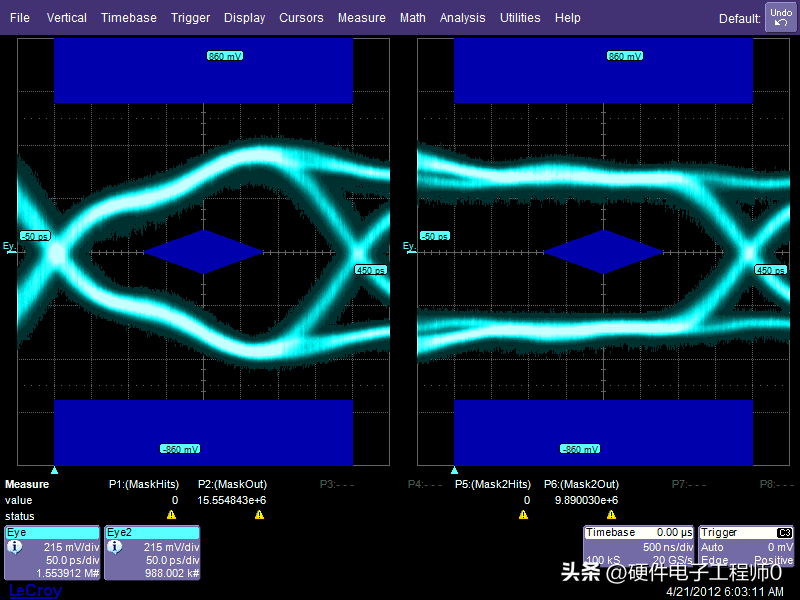

图3.3‑2、PCIe接收端RXD测试眼图

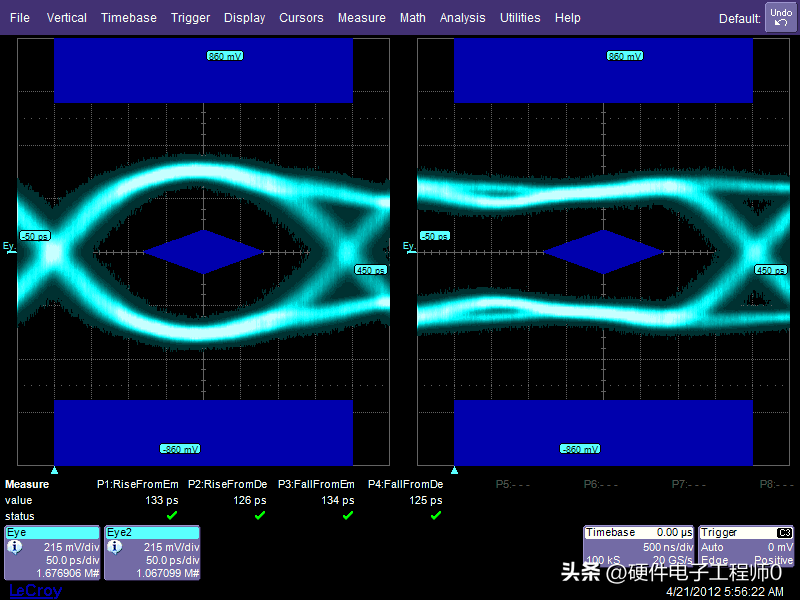

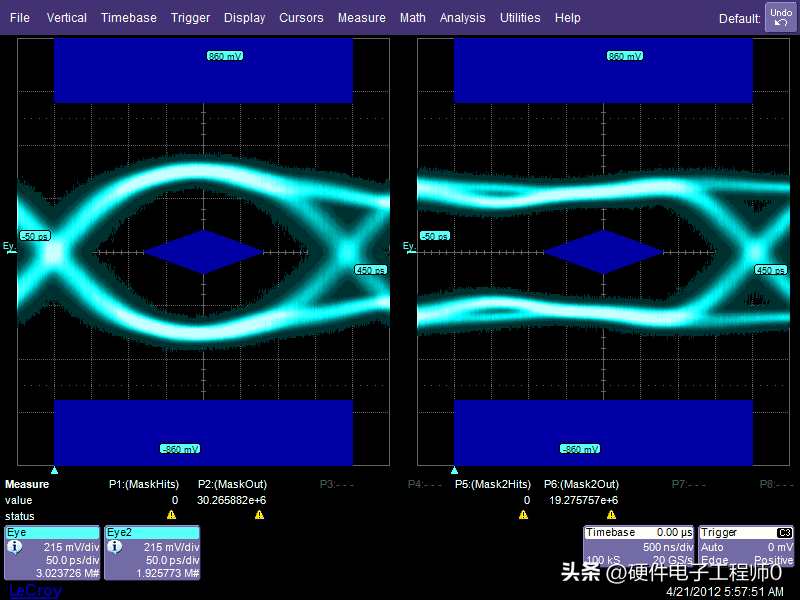

图3.3‑3、PCIe接收端TXD测试眼图

审核编辑:刘清

-

示波器

+关注

关注

113文章

6405浏览量

187162 -

高电平

+关注

关注

6文章

159浏览量

21709 -

时钟驱动器

+关注

关注

0文章

50浏览量

13958 -

PCIe接口

+关注

关注

0文章

121浏览量

9931

发布评论请先 登录

相关推荐

如何进行PCI-Express的一致性测试和分析

基于PCI-Express的高速数据交换设计及应用

如何对PCI-Express总线的SSC(扩频时钟)进行验证

pci express总线概念

PCI Express插槽,什么是PCI Express插槽

基于Virtex5的PCI-Express总线接口设计

PCI-Express插槽

从PCI、PCI-X到PCI-Express之间的连接

【科普】一文读懂PCI-Express硬件接口

【科普】一文读懂PCI-Express硬件接口

评论